本文以硅基相控阵收发组件中的数控式幅度衰减器为主要研究对象,从零极点补偿的角度分析旁路电容补偿结构对衰减器拓展工作频率的作用。在此基础上,提出改良式的π/T型衰减结构,该结构基于容性RC矫正网络的补偿结构,调节幅度和相位对频率的响应,在节约核心电路面积的同时,提升了带内精度,满足了衰减器在收发组件中跨频段、宽频域的工作需求.

1. 衰减电路设计与分析方法

1.1. 开关内嵌衰减器

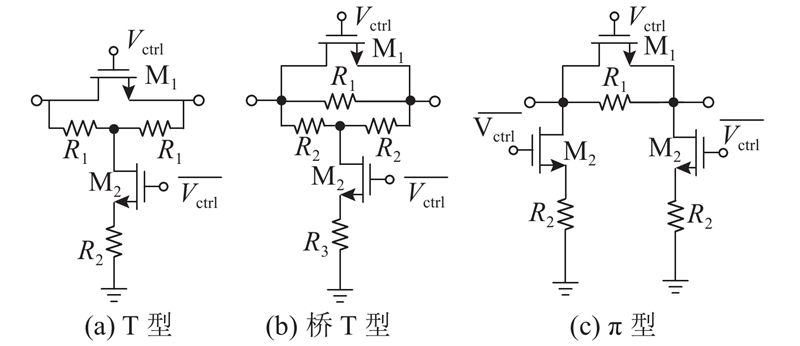

图 1

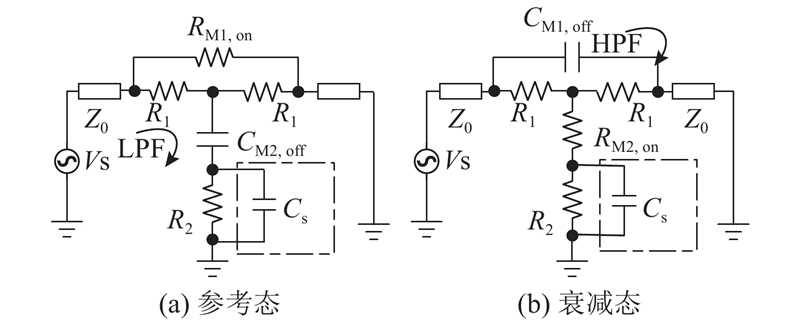

如图2所示,以不含虚线框内旁路补偿电容Cs的简单T型结构为例,在串联和并联支路上分别由2个NMOS晶体管充当开关. 开关开启时,NMOS等效为起主要作用的沟道电阻RM1,on、RM2,on,关闭时等效为寄生电容CM2,off、CM1,off[5-6]. R1、R2分别为串联支路和并联支路上用于调节衰减量的电阻;Z0为级联匹配电阻,Z0 = 50 Ω.理想情况下,调整阻值M1、M2宽长比尺寸即可达到所需的衰减量,但随着频率增加,高频下的寄生电容和衬底耦合效应引起的信号损失增大,影响了衰减量的平坦精度.在串联支路上,电阻和CM2,off、CM1,off分别在参考态和衰减态构成低通滤波(low-pass filter,LPF)和高通滤波(high-pass filter,HPF)结构,使得衰减态比参考态的相位超前[5, 7, 13],二者叠加形成相位误差,极大地影响了系统稳定性.

图 2

1.2. 零极点对系统频率响应的影响

已知对于多阶连续信号系统,在s域输出输入响应可用线性常微分关系式表示为

式中:增益因子

若式(1)写成极坐标形式,则可以得到用零、极点表示的系统幅度频率响应

式中:

2. 基于零极点的衰减模块分析与设计

2.1. 普通衰减结构的零、极点分析

以桥T型结构的衰减单元为例,图2中不含虚线框内旁路补偿电容Cs的电路部分为普通结构. 为了分析在2种状态下,对信号产生主要影响的零、极点位置,计算参考态衰减态的传输函数,通过零、极点所在频点判断零、极点对幅相变化的影响:

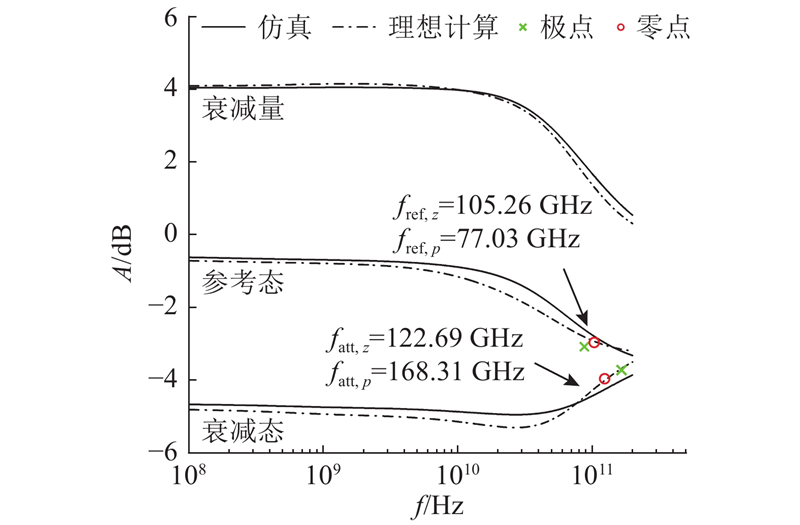

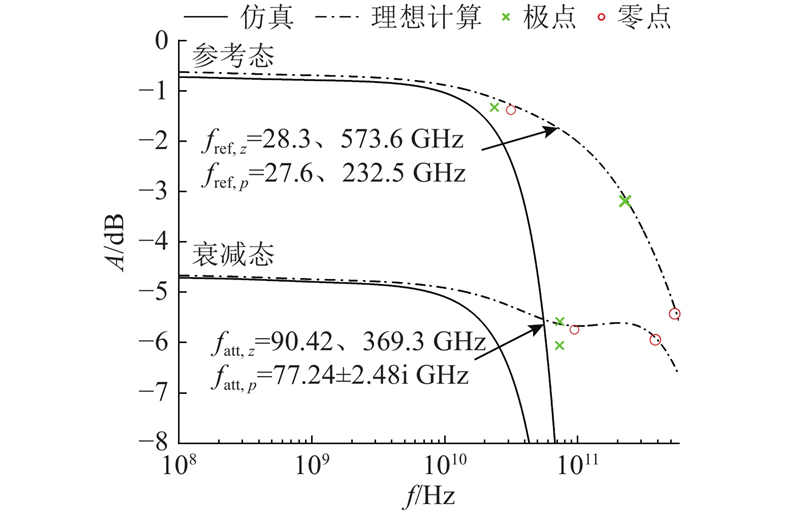

在理想情况下,桥T单元只有一个零点和一个极点. 如图3所示,理想计算曲线表明采用理想晶体管、电阻等器件搭建桥T衰减单元时零、极点分布情况. 图中,A为衰减量,f为工作频率。参考态时极点(fref,p)率先出现在77.03 GHz,零点(fref,z)位于105.26 GHz;衰减态零极点出现的顺序恰好相反,零点(fatt,z)先于极点(fatt,p),分别位于122.69 GHz和168.31 GHz.

图 3

图 3 4 dB桥T衰减幅度响应及零、极点分布

Fig.3 Amplitude response and pole-zero distribution of 4 dB bridge-T cell

表 1 4 dB桥T衰减单元器件参数

Tab.1

| 参数 | 单位 | 数值 | 参数 | 单位 | 数值 | |

| R1 | Ω | 44.00 | RM1,on | Ω | 9.84 | |

| R2 | Ω | 38.00 | CM1,off | fF | 43.36 | |

| R3 | Ω | 56.00 | RM2,on | Ω | 23.00 | |

| Z0 | Ω | 50.00 | CM2,off | fF | 20.66 |

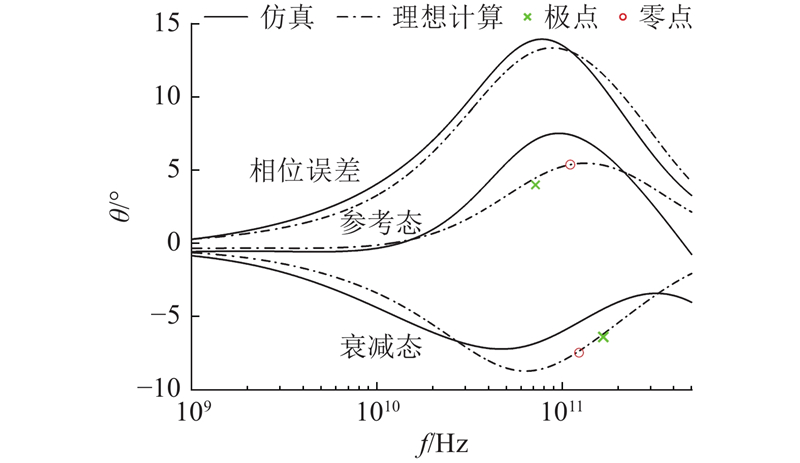

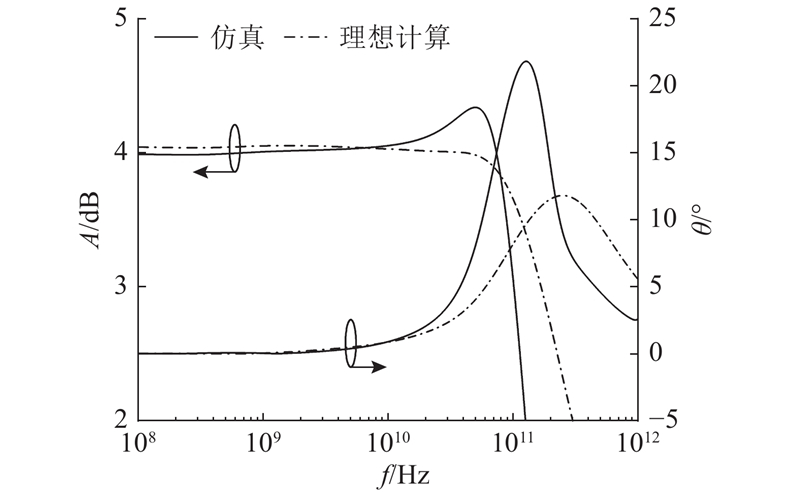

零极点分布对于2种状态下的相位响应,如图4所示.图中,

图 4

图 4 4 dB桥T衰减相位响应及零、极点分布

Fig.4 Phase response and pole-zero distribution of 4 dB bridge-T cell

2.2. 旁路电容补偿结构

由于各器件参数值已知,式中表示常数的多项式被部分省略,但能通过传输函数中s的次幂数得知Cs的引入额外增加了一对零极点.零极点的位置变化如图5所示. 由图可知,参考态,第一对零点和极点分别出现在28.3 GHz 和27.6 GHz,非常接近,因此两者的影响几乎可以抵消,同时也表明未显现的对消零、极点对整体平坦的重要意义. 另一对极点先于零点出现,因此极点起到了主要调节作用. 衰减态时,2个极点率先出现在77±2.48i处. 在系统响应中,极点的虚部代表系统震荡的快慢,在极点出现时衰减态的幅度产生衰减,而后在90.42 GHz出现的零点修正了这一影响,相比于普通桥T结构工作频段,带有旁路电容的桥T衰减结构的工作频段得到极大拓展.相比于无补偿的普通桥T结构,引入新的容性元件以及高频耦合的影响使得高频段的波动加剧,导致随着频率升高,实际电路频率响应的曲线与理想计算出现偏差. 如图6所示为电路仿真与理想计算幅相响应曲线,对比表明:极点和零点附近可能会影响衰减器单元的频率特性,需要结合具体情况仿真调节补偿电容的容值,以消除隐匿的其他零、极点,达到拓展工作频段的目的.

图 5

图 5 含有旁路电容补偿的4 dB桥T衰减结构零极点分布

Fig.5 Pole-zero distribution of 4 dB bridge-T cell with Cs

以上分析表明在容性校正结构可以通过调整零极点的位置改变频率响应,进而优化工作频带和误差精度. 对于衰减量较大的单元,如8、16 dB,一般采用π型结构. 由于π型结构器件数目多,含有Cs补偿电容的结构在设计大衰减量单元时,受到的寄生效应和高频影响更复杂,存在较宽工作频带内性能不稳定的问题,需要进一步补偿.

图 6

图 6 含有旁路电容4 dB桥T衰减结构幅相响应

Fig.6 Amplitude and phase response of 4 dB bridge-T cell with Cs

3. 整体电路设计和仿真

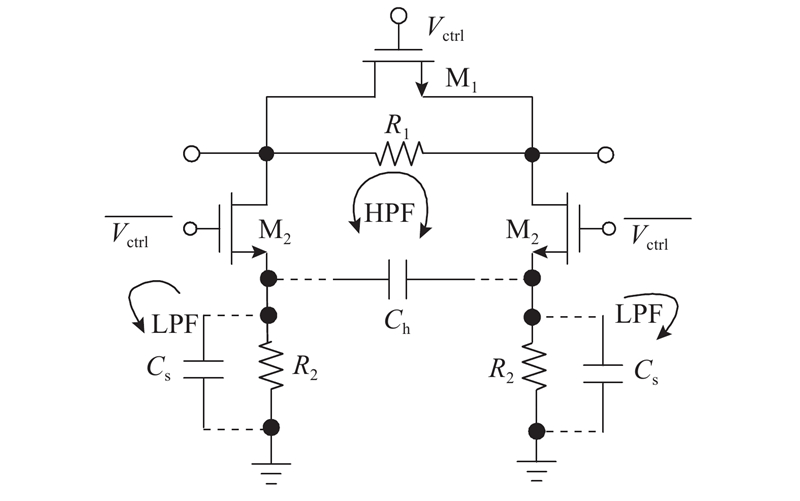

3.1. 新型的双重电容补偿衰减结构

如图7所示,本文提出具有双重电容补偿的全新结构. 图中,虚线连接部分为增添的补偿电容,在π型2个并联支路的旁路补偿电容基础上,再增加一个水平方向的Ch,构成三阶滤波结构,再增加一对零、极点. 由于传输函数过于复杂,在此不予列出,双重电容补偿结构的容值确定与旁路电容方法相同,可以通过Matlab计算得到.

图 7

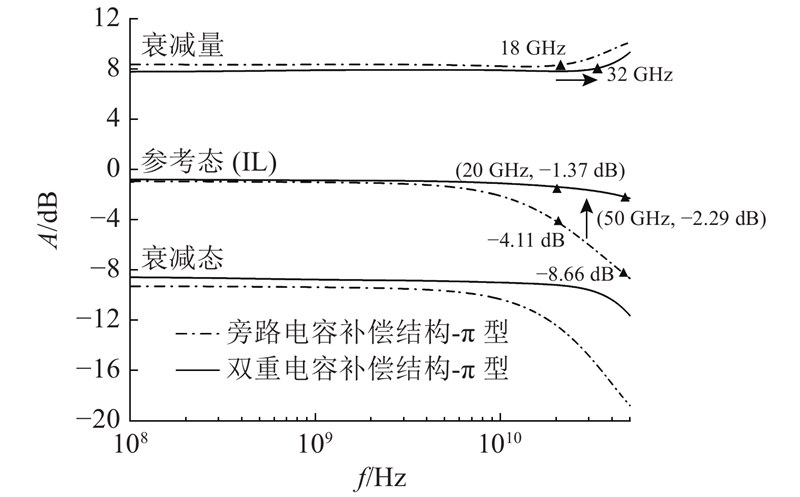

旁路电容补偿结构和具有双电容补偿结构幅度响应如图8所示,参考态曲线,同时也代表衰减单元的插入损耗(insert loss,IL),表明前者在18 GHz以后衰减平坦度急剧恶化,在20 GHz处达到−4.1 dB. 而本文提出的双重电容补偿结构不但在32 GHz频带内依然维持着相对平坦的衰减量,同时在50 GHz的频带内,插入损耗仍小于−2.3 dB,表明具有双重电容补偿的衰减结构对于降低整个衰减系统功耗有着重要意义.

图 8

图 8 2种电容补偿结构幅度响应对比

Fig.8 Comparison of amplitude response of two capacitors compensation structures

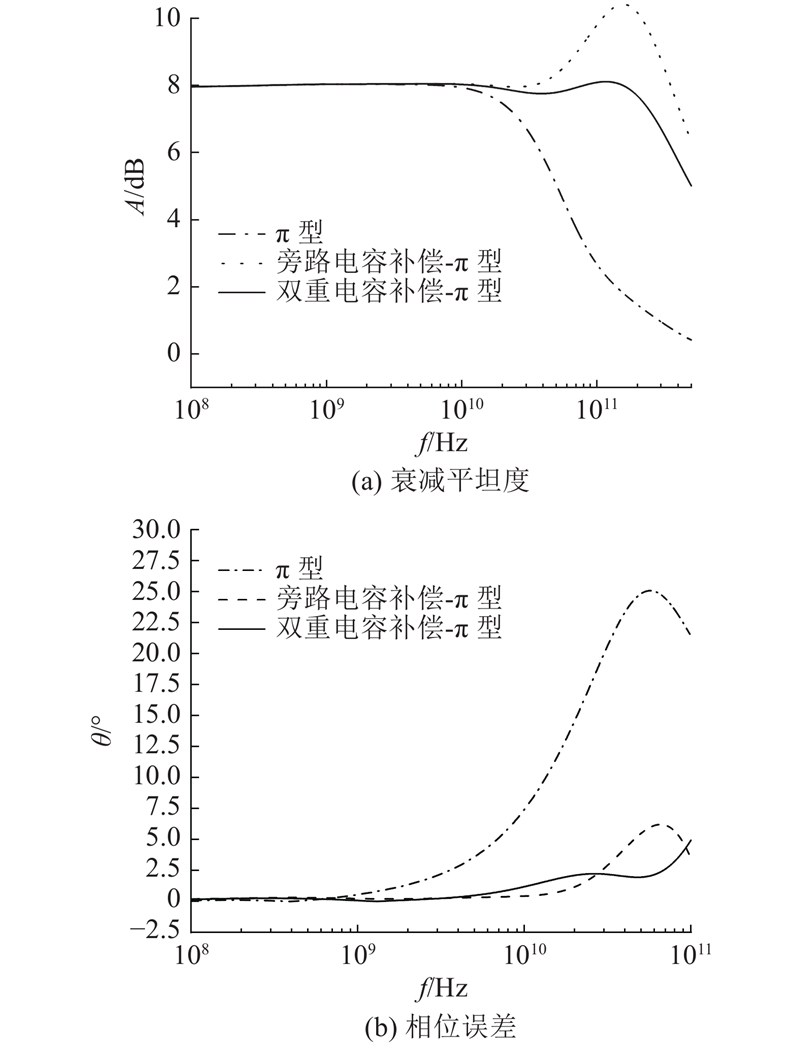

如图9所示为普通π型衰减单元与其他2种补偿结构的信号衰减平坦度和相位误差的仿真结果对比. 由图可知,仅含有Cs的π型电路,衰减态时在55 GHz出现了一对不在实轴的零点,而下一个极点出现在78 GHz;增加Ch后分别在58 GHz和68.5 GHz增加了2个极点,补偿了率先出现的零点.双重补偿结构在旁路电容补偿的基础上进一步拓展了最高工作频率,同时减小了衰减和相移的误差,对插损亦有优化.

图 9

图 9 普通衰减单元与2种改进π型结构对比

Fig.9 Comparison of ordinary π-topology attenuation cell and two improved structures

3.2. 减小插损设计

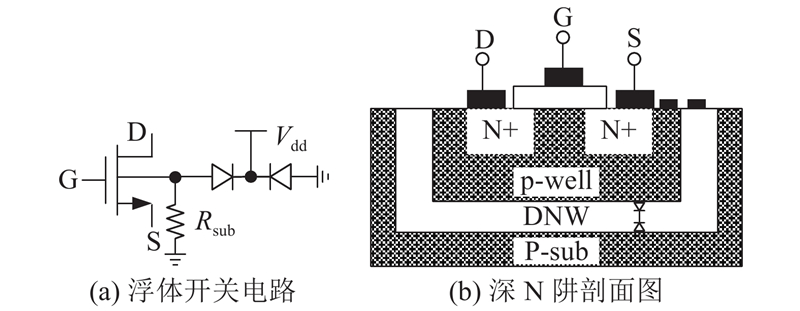

在硅基工艺中,晶体管开关导通的沟道电阻是产生插入损耗的主要原因. 本文全部开关均采用体悬浮的深N阱技术,以减小衬底耦合产生的信号损失. 同时对衰减单元进行简化设计以整体减小插损.

3.2.1. 体悬浮深N阱晶体管开关

图 10

图 10 浮体开关电路及深N阱剖面图

Fig.10 Body-float switch circuit and cross section of deep N-type well

3.2.2. 简化T衰减结构

图 11

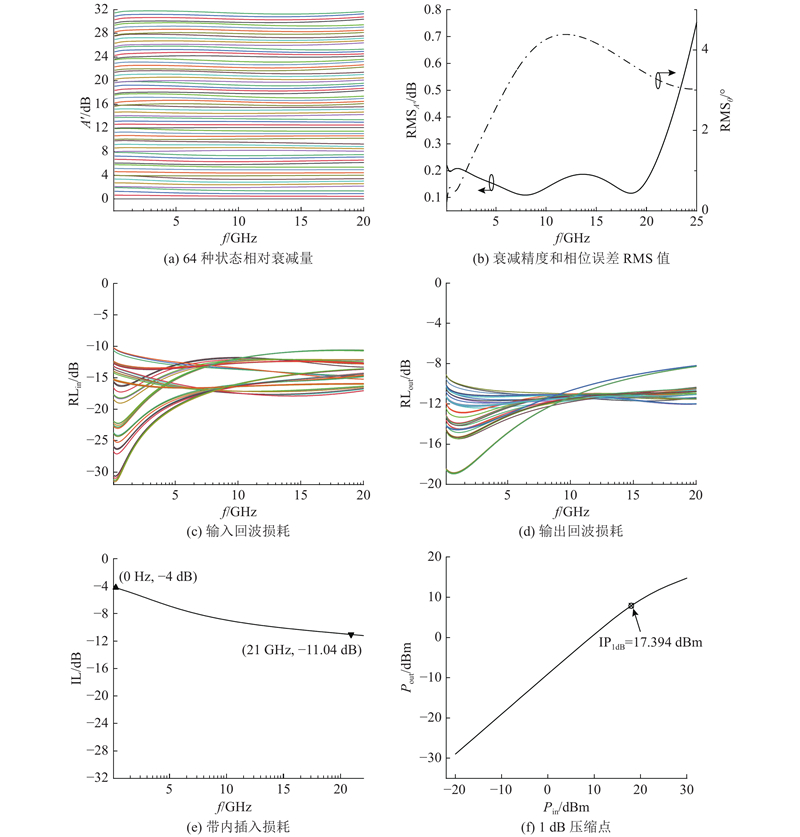

3.3. 整体版图设计与仿真

使用Cadence Spectre RF 进行后仿提参,并使用ADS momentum工具对电感、传输线效应、信号线等高频敏感部分进行电磁仿真,整体电路仿真结果如图12所示.图12(a)为0~21 GHz工作频带内衰减器衰减情况。图中,A'为相对衰减量。由图可知,64态相对衰减曲线表明设计的6位衰减器相对衰减量平坦均匀,具有较好的衰减功能. 图12(b)为衰减器的衰减精度和附加相移均方根(root mean square, RMS),在0~21 GHz的超宽工作频率范围内,衰减误差均方根小于0.23 dB,相位误差均方根小于4.38°,衰减器具有良好的衰减平坦特性和相位误差. 图12(c)、(d)分别为输入和输出的回波损耗(return loss, RL),由于采用简化T结构的设计,输入回波损耗中的两态曲线在高频处有所恶化. 图12(e)表明工作频带内插入损耗为−4~ −11.04 dB.图12(f)显示中心频率10 GHz处输入1 dB 压缩点 IP1dB为17.3 dBm,表明整体电路具有良好线性度. 图中P为功率。

图 12

表 2 电容补偿结构衰减器关键性能对比

Tab.2

| 设计结构 | D/μm | f/GHz | RA/dB | SA/dB | IL/dB | RL/dB | RMSA'/dB | RMSθ/(°) | IP1dB/dBm | S/mm2 |

| *为核心电路面积 | ||||||||||

| 文献[5] | 0.130 | 0~20 | 0~31.50 | 0.5 | 1.7-7.2 | <−12 | 0.37 | <4.0 | 10 | 0.14*(1.00×0.14) |

| 文献[6] | 0.350 | 14~18 | 0~31.50 | 0.5 | 8±0.6 | <−10 | 0.29 | <3.9 | >10 | 0.27*(0.80×0.34) |

| 文献[8] | 0.180 | 3~22 | 0~31.00 | 1 | 5.53~13.07 | <−11 | 0.53 | <6.3 | 18.4 | — |

| 文献[10] | 0.130 | 3~13 | 0~31.75 | 0.25 | <6.6 | <−9 | 0.17 | <2.8 | 16.8 | 1.57(1.59×0.79) |

| 文献[19] | 0.065 | 8~18 | 0~31.50 | 0.5 | 6.1~8.6 | <−10 | 0.1 | <5.5 | 12 | 0.273*(0.91×0.3) |

| 文献[20] | 0.180 | 0~18 | 0~31.50 | 0.5 | 2.9~6.1 | <−11 | 0.39 | <2.4 | — | — |

| 本文 | 0.180 | 0~21 | 0~31.50 | 0.5 | 4~11.05 | <−8.35 | 0.23 | <4.38 | 17.3 | 0.172*(0.86×0.02) |

4. 结 论

(1)在开关内嵌衰减电路中,晶体管开关引入的非理想特性和寄生参数造成衰减器误差,本文通过零、极点分析方法,提出改良式的π/T 型衰减结构,有效提高了衰减器的工作带宽和带内精度.

(2)利用HHNEC 0.18 μm SiGe BiCMOS工艺进行设计调试,仿真结果表明所设计衰减结构性能优良,具有较高精度,提出的新型双重电容补偿结构具有可拓展性和实用性,为实现数字衰减器多波段切换、跨频域覆盖的工作提供了新的设计方法.

(3)与其他相同尺寸的硅基工艺衰减器相比,本文仍存在插入损耗较大的问题. 同时,为了减小插入损耗引入的简化结构造成了高频处输出匹配性能的恶化,针对高频耦合对线性度和相位频率响应特性的影响,可以进一步采用开关电路进行级联匹配电感的切换,优化衰减电路输出匹配性能.

参考文献

Analysis and design of RF CMOS attenuators

[J].DOI:10.1109/JSSC.2008.2004325 [本文引用: 1]

A CMOS K-band 6-bit attenuator with low phase imbalance for phased array applications

[J].DOI:10.1109/ACCESS.2017.2750203 [本文引用: 1]

Design and analysis of a low loss, wideband digital step attenuator with minimized amplitude and phase variations

[J].DOI:10.1109/JSSC.2018.2850559 [本文引用: 6]

7-Bit SiGe-BiCMOS step attenuator for x-band phased-array RADAR applications

[J].DOI:10.1109/LMWC.2016.2585565 [本文引用: 1]

A 5-bit lumped 0.18 μm CMOS step attenuator with low insertion loss and low phase distortion in 3~22 GHz applications

[J].

6-Bit CMOS digital attenuators with low phase variations for x -band phased-array systems

[J].DOI:10.1109/TMTT.2010.2049691 [本文引用: 2]

A 7-bit reverse-saturated SiGe HBT discrete gain step attenuator

[J].DOI:10.1109/TCSII.2019.2922418 [本文引用: 1]

A 10~67 GHz CMOS dual function switching attenuator with improved flatness and large attenuation range

[J].

一种5~20 GHz低插损低相位误差的CMOS衰减器

[J].

5~20 GHz CMOS attenuator with a low insertion loss and a low phase error

[J].

Analysis and design of a DC to 18 GHz 6-bit attenuator with simultaneous phase and gain error correction

[J].DOI:10.1016/j.aeue.2019.152829 [本文引用: 1]

Ku波段 SiGe幅相多功能芯片设计

[J].

Design of Ku-band SiGe multi-function chip with phase and amplitude control

[J].

5~40 GHz CMOS衰减器的设计与实现

[J].

Design and implementation of a 5~40 GHz CMOS attenuator

[J].

Ka-band low-loss and high-isolation switch design in 0.13 μm CMOS

[J].DOI:10.1109/TMTT.2008.921749 [本文引用: 1]

A switched T-attenuator using 0.18 μm CMOS optimized switches for DC-20 GHz

[J].DOI:10.1016/j.aeue.2015.08.016 [本文引用: 2]

A novel concurrent 22~29/57~64 GHz dual-band CMOS step attenuator with low phase variations

[J].DOI:10.1109/TMTT.2016.2546256 [本文引用: 1]