[1]

ROSHAN-ZAMIR A, IWAI T, FAN Y H, et al. A 56 Gb/s PAM4 receiver with low-overhead threshold and edge-based DFE FIR and IIR-tap adaptation in 65nm CMOS [C]// IEEE Custom Integrated Circuits Conference . San Diego: IEEE, 2018: 1-4.

[本文引用: 1]

[2]

SEGAL Y, LAUFER A, KHAIRI A, et al. A 1.41 pJ/b 224 Gb/s PAM-4 SerDes receiver with 31dB loss compensation [C]// International Solid-State Circuits Conference . San Francisco: IEEE, 2022: 114-115.

[本文引用: 1]

[3]

POON C F, ZHANG W F, CHO J H, et al A 1.24-pJ/b 112-Gb/s (870 Gb/s/mm) transceiver for in-package links in 7-nm FinFET

[J]. IEEE Journal of Solid-State Circuits , 2022 , 57 (4 ): 1199 - 1210

DOI:10.1109/JSSC.2022.3141802

[本文引用: 1]

[4]

LU P. A 25.6-27.5GHz phase-locked loop for SerDes transceiver clocking in 5nm FinFET [C]// IEEE Nordic Circuits and Systems Conference . Oslo: IEEE, 2021: 1-4.

[本文引用: 1]

[5]

辛可为, 吕方旭, 王建业, 等 适用于4通道100 Gbps SerDes的两级架构正交12.5 GHz低功耗低抖动时钟发生器

[J]. 空军工程大学学报: 自然科学版 , 2019 , 20 (5 ): 64 - 69

[本文引用: 1]

XIN Kewei, LV Fangxu, WANG Jianye, et al A 12.5 GHz clock generator applicable for 4-way 100 Gbps high-speed serial interface circuits

[J]. Journal of Air Force Engineering University: Natural Science Edition , 2019 , 20 (5 ): 64 - 69

[本文引用: 1]

[6]

李沛杰, 沈剑良, 苑红晓, 等 一种应用于软件定义互连系统的多协议SerDes电路

[J]. 电子学报 , 2021 , 49 (4 ): 817 - 823

[本文引用: 1]

LI Peijie, SHEN Jianliang, YUAN Hongxiao, et al A multi-protocol SerDes circuit for the application in software defined interconnection system

[J]. ACTA Electronica Sinica , 2021 , 49 (4 ): 817 - 823

[本文引用: 1]

[7]

SAURABH K, KUMAR S Y A low-phase-noise self-aligned sub-harmonically injection-locked PLL using aperture phase detector-based DLL windowing technique

[J]. IEEE Access , 2023 , 11 : 6641 - 6655

DOI:10.1109/ACCESS.2023.3237539

[本文引用: 1]

[8]

YANG X, LIU F, HUO Z L Wide-range and high-accuracy four-phase DLL with the adaptive-bandwidth scheme

[J]. Xi'an Dianzi Keji Daxue Xuebao/Journal of Xidian University , 2022 , 49 (1 ): 194 - 201

[本文引用: 1]

[9]

BAE W. State-of-the-art circuit techniques for low-jitter phase-locked loops: advanced performance benchmark FOM based on an extensive survey [C]// IEEE International Symposium on Circuits and Systems . Daegu: IEEE, 2021: 1-5.

[本文引用: 1]

[10]

LIU H L, SUN Z, HUANG H Y, et al A 265-mu W fractional-N digital PLL with seamless automatic switching sub-sampling/sampling feedback path and duty-cycled frequency-locked loop in 65-nm CMOS

[J]. IEEE Journal of Solid-State Circuits , 2019 , 54 (12 ): 256 - 257

[本文引用: 1]

[11]

LIU L X, JI Y L, LIAO X F, et al A 0.8-V, 2.55-GHz, 2.62-mW charge-pump PLL with high spectrum purity

[J]. IEEE Transactions on Very Large Scale Integration Systems , 2022 , 30 (2 ): 113 - 122

DOI:10.1109/TVLSI.2022.3140457

[本文引用: 1]

[12]

ZHANG Z, YANG J, LIU L, et al A 0.9-2.25 GHz sub-0.2-mW/GHz compact low-voltage low-power hybrid digital PLL with loop bandwidth-tracking technique

[J]. IEEE Transactions on Very Large Scale Integration Systems , 2018 , 26 (5 ): 933 - 944

DOI:10.1109/TVLSI.2018.2797280

[本文引用: 1]

[13]

吴金, 孙亚伟, 彭杰, 等 一种应用于阵列TDC的低抖动锁相环设计

[J]. 电子学报 , 2020 , 48 (9 ): 1703 - 1710

[本文引用: 1]

WU Jin, SUN Yawei, PENG Jie, et al Design of a low jitter phase locked loop for array TDC

[J]. ACTA Electronica Sinica , 2020 , 48 (9 ): 1703 - 1710

[本文引用: 1]

[14]

邓涵, 韦雪明, 尹仁川, 等 一种自适应可重构宽带低抖动锁相环时钟

[J]. 微电子学 , 2023 , 53 (1 ): 89 - 94

[本文引用: 1]

DENG Han, WEI Xueming, YIN Renchuan, et al A wideband low jitter PLL clock with adaptive reconfigurable charge pump

[J]. Microelectronics , 2023 , 53 (1 ): 89 - 94

[本文引用: 1]

[15]

FISCHETTE D. A 45-nm SOI-CMOS dual-PLL processor clock system for multi-protocol I/O [C]// IEEE International Solid-State Circuits Conference. San Francisco: IEEE, 2010: 246-248.

[本文引用: 1]

[16]

ZHAN Y Z, LI T, ZOU X F, et al. Low-power 25Gb/s 16: 1 multiplexer for 400Gb/s ethernet PHY [C]// 2nd International Conference on Applied Physics and Computing . Ottawa: Elsevier, 2021.

[本文引用: 1]

[17]

ZHANG Y, WEN Z P, HOU X P. A 0.78mW inductor-less 21GHz CML frequency divider in 65nm CMOS [C]// IEEE 3rd Information Technology, Networking, Electronic and Automation Control Conference . Chengdu: IEEE, 2019: 1395-1399.

[本文引用: 1]

[18]

KUNDERT K. Predicting the phase noise and jitter of PLL based frequency synthesizers [Z]. Designer’s Guide Consulting, Inc. 2006.

[本文引用: 1]

[19]

SOPHIYA S S, YELLAMPALLI S S. Design of 6.7GHz~7. 518GHz cross coupled LC-VCO in 180nm CMOS technology [C]// 5th International Conference on Computing Methodologies and Communication . Erode: IEEE, 2021: 665-671.

[本文引用: 1]

[20]

MAHESHWARI N, CHAUHAN P S, PANDA D K. Design and optimization of switched capacitor array based differential CMOS LC VCO for wide band application [C]// International Conference on Information, Communication, Instrumentation and Control . Indore: IEEE, 2017.

[本文引用: 1]

[21]

SAMARAS D, HATZOPOULOS A. A low-power low-noise 65nm charge pump using mismatch compensation and smoothing capacitor [C]// 11th International Conference on Modern Circuits and Systems Technologies . Bremen: IEEE, 2022: 1-4.

[本文引用: 1]

[22]

GHASEMIAN H, BAHRAMI A, JAMADI B, et al. Implement of two new high-speed low-power PFDs with low blind zone and dead zone in 65nm CMOS technology [C]// 28th Iranian Conference on Electrical Engineering . Tabriz: IEEE, 2020: 1-6.

[本文引用: 1]

[23]

BEUKEMA T. Topics on design and analysis of high data rate SerDes system [EB/OL]. [2019-11-30]. https://picture.iczhiku.com/resource/eetop/SYKhWDtRRtzOyvvn.pdf.

[本文引用: 1]

[24]

YUAN H, CHEN J, LIANG B, et al. A radiation-immune low-jitter high-frequency PLL for SerDes [C]// CCF National Conference on Computer Engineering and Technology . Xiamen: Elsevier, 2017: 45-51.

[本文引用: 3]

[25]

ZHOU P Z, WU L, LI C, et al. A 6.3-8.7 GHz phase-locked loop in 65nm CMOS [C]// IEEE International Workshop on Electromagnetics: Applications and Student Innovation Competition . Guangzhou: Elsevier, 2021: 1-4.

[本文引用: 2]

[26]

HUANG Y B, CHEN Y, ZHAO B, et al A 3.6-GHz type-II sampling PLL with a differential parallel-series double-edge S-PD scoring 43.1-fs RMS jitter, −258.7-dB FOM, and −75.17-dBc reference spur

[J]. IEEE Transactions on Very Large Scale Integration Systems , 2023 , 31 (2 ): 188 - 198

DOI:10.1109/TVLSI.2022.3229342

[本文引用: 5]

[27]

KIM D, CHO S H. A supply noise insensitive PLL with a rail-to-rail swing ring oscillator and a wideband noise suppression loop [C]// Symposium on VLSI Circuits . Kyoto: Elsevier, 2017: 180-181.

[本文引用: 2]

[28]

YUAN H Z, GUO Y, LIU Y, et al A self-biased low-jitter process-insensitive phase-locked loop for 1.25Gb/s-6.25Gb/s SerDes

[J]. Chinese Journal of Electronics , 2018 , 27 (5 ): 1009 - 1014

DOI:10.1049/cje.2018.02.003

[本文引用: 2]

[29]

GROUT K, KITCHEN J A dividerless ring oscillator PLL with 250fs integrated jitter using sampled low pass filter

[J]. IEEE Transactions on Circuits and Systems II: Express Briefs , 2020 , 67 (11 ): 2337 - 2341

[本文引用: 4]

[30]

YANG Z S, CHEN Y, YANG S H, et al A 10.6-mW 26.4-GHz dual-loop type-II phase-locked loop using dynamic frequency detector and phase detector

[J]. IEEE Access , 2020 , 8 : 2222 - 2232

DOI:10.1109/ACCESS.2019.2962060

[本文引用: 1]

1

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

1

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

A 1.24-pJ/b 112-Gb/s (870 Gb/s/mm) transceiver for in-package links in 7-nm FinFET

1

2022

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

1

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

适用于4通道100 Gbps SerDes的两级架构正交12.5 GHz低功耗低抖动时钟发生器

1

2019

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

适用于4通道100 Gbps SerDes的两级架构正交12.5 GHz低功耗低抖动时钟发生器

1

2019

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

一种应用于软件定义互连系统的多协议SerDes电路

1

2021

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

一种应用于软件定义互连系统的多协议SerDes电路

1

2021

... 在人工智能、自动驾驶、云计算和大数据等高算力的驱动下,高速SerDes串行接口得到快速发展,接口速率达到224 Gb/s[1 -2 ] . 400G以太网中4×100 Gb/s、8×50 Gb/s和16×25 Gb/s的高速串口对锁相环电路(phase-locked loop, PLL)的动态性能提出了更高的设计要求[3 -4 ] ,特别是对随机抖动均方差(RMS Jitter)的要求很高. 时钟信号的RMS抖动直接影响高速串行链路的时域阈值和传输信号的质量. 低抖动高速PLL成为高速SerDes传输链路的研究焦点[5 -6 ] . ...

A low-phase-noise self-aligned sub-harmonically injection-locked PLL using aperture phase detector-based DLL windowing technique

1

2023

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

Wide-range and high-accuracy four-phase DLL with the adaptive-bandwidth scheme

1

2022

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

1

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

A 265-mu W fractional-N digital PLL with seamless automatic switching sub-sampling/sampling feedback path and duty-cycled frequency-locked loop in 65-nm CMOS

1

2019

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

A 0.8-V, 2.55-GHz, 2.62-mW charge-pump PLL with high spectrum purity

1

2022

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

A 0.9-2.25 GHz sub-0.2-mW/GHz compact low-voltage low-power hybrid digital PLL with loop bandwidth-tracking technique

1

2018

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

一种应用于阵列TDC的低抖动锁相环设计

1

2020

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

一种应用于阵列TDC的低抖动锁相环设计

1

2020

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

一种自适应可重构宽带低抖动锁相环时钟

1

2023

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

一种自适应可重构宽带低抖动锁相环时钟

1

2023

... 为了达到这一目的,目前国内外的研究学者主要集中在电路结构、参数优化、可编程等方面. 在电路结构上,注入型PLL[7 ] (injection-locked phase-locked loop, ILPLL)和延迟型PLL[8 ] (delay-locked loop, DLL)分别通过引入注入锁定技术和压控延迟技术,解决高频单环PLL中环路带宽限制的问题,抑制振荡器所引起的噪声. 注入锁定技术会增加额外的功耗、面积及较大的注入杂散,恶化了品质因数(figure-of-merit, FoM)性能[9 ] . 压控延迟技术的延迟单元间存在失配,导致相位时钟之间的相位误差无法精确调整,这会增大高速传输链路中时序错误的可能性. 为了避免上述额外的抖动影响,亚采样锁相环在锁定状态下没有分频器的作用[10 ] ,通过采样-保持电路抑制鉴频鉴相器、电荷泵带来的带内噪声. 亚采样锁相环的频率锁定范围十分有限,大约为环路带宽的2倍,严重限制了PLL在高速串行传输链路中的应用. 除此之外,上述锁相环的性能受限于环路参数. 针对该问题,部分研究学者展开相应的研究,取得了一定的成果. Liu等[11 ] 采用0.18 μm工艺设计低电压低功耗CPPLL,通过采用双混合环路C类压控振荡器、自适应调节机制、动态电流补偿技术来优化相位噪声和参考杂散,即-123.97 dBc/Hz @1 MHz和−89 dBc,优于基于65nm的CPPLL性能[12 ] . 此外,吴金等[13 ] 结合开环最大裕度法,利用特定激励下的迭代数据分析法,实现环路带宽最优化,改善了锁相环电路的频率范围、频率偏差和抖动特性. 邓涵等[14 ] 采用可重构并联电荷泵结构,通过自适应调整电荷泵电流和倍频因子的关系,抑制高倍频比对时钟抖动的影响,实现低抖动的时钟信号. 延迟振荡器的最高输出频率仅为4 GHz,难以满足高速串行链路的速率需求. 在高速串行链路中采用较小的分频比,可以有效地降低锁相环的带内噪声. 鉴频鉴相器、电荷泵、振荡器等电路所产生的噪声成为影响PLL性能的主要原因. ...

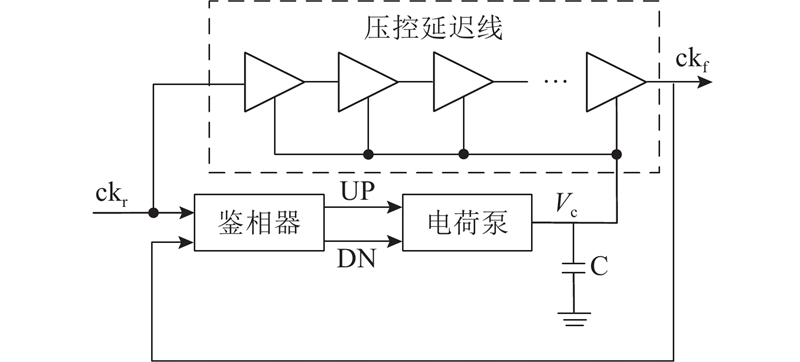

1

... 锁相环作为时钟产生电路,是SerDes链路中重要的模块之一. 按照环路结构,可以分为延迟型和LC振荡型. 图1 给出延迟型锁相环的电路结构,包括鉴相器、电荷泵和压控延迟线. 由于DLL存在无反馈回路,压控延迟线产生的抖动或相位噪声不会循环累积. 振荡频率ω osc 主要取决于电路的延时t 和级数N ,即ω osc =1/(2Nt ),具有占用面积小、功耗低的优点,主要适用于5.0 GHz以下的低频应用场景. 随着SerDes传输速率的不断提高,如10 Gb/s+,DLL需要更大的电流来提高振荡频率,无法满足更高的相位噪声、抖动和功耗等要求. LC-VCO PLL中电感和电容所占用的面积将更小,在功耗和抖动上凸显优势. 在10 Gb/s及以上的应用场景中,尤其是在400 Gb/s物理层,基于LC-VCO的PLL更合适[15 ] . ...

1

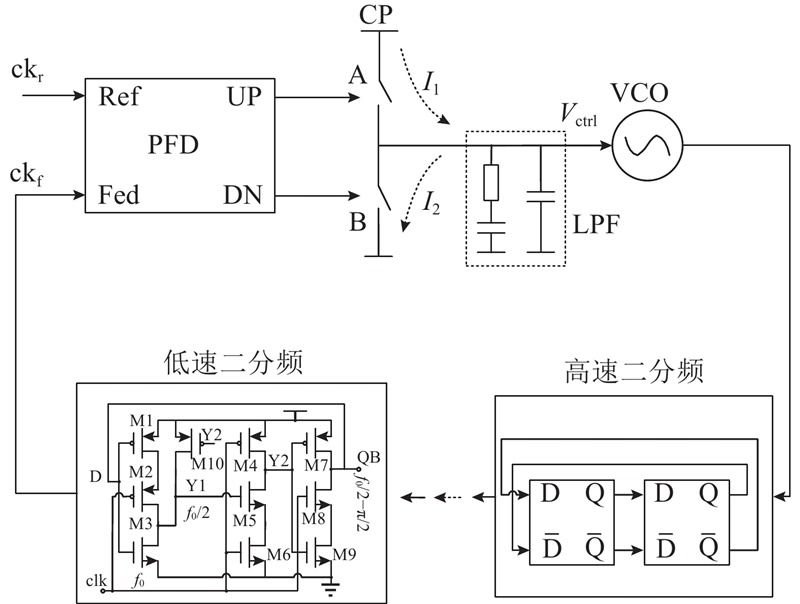

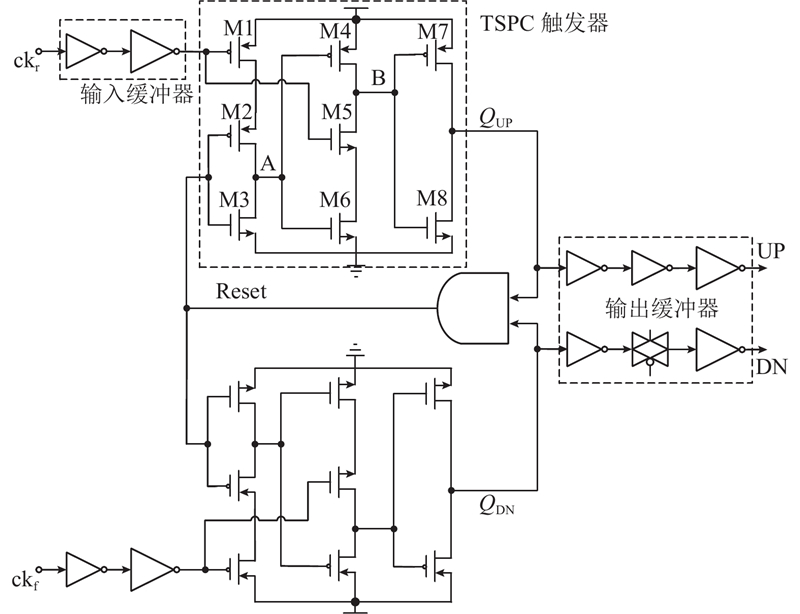

... 如图2 所示,为了满足物理层25 Gb/s串口中32∶1复接器[16 ] 和行列交织器读写的时钟频率关系,即12.5 GHz∶6.25 GHz∶1.562 5 GHz∶781.25 MHz,采用较小的分频数(=16)以抑制锁相环的带内噪声. 采用781.25 MHz的时钟信号作为输入参考频率ckr . 在16级分频器中,高速二分频器选择基于电流模(current mode logic, CML)的D触发器实现VCO输出频率的二分频[17 ] ,低速二分频采用带有上拉电阻M1的真单相时钟型触发器(single phase clock type, TSPC)进行分频. 分频后,PFD对输入参考频率和反馈频率ckf 进行鉴频鉴相,控制CP的充电过程I 1 和放电过程I 2 ,通过LPF抑制控制电压的纹波,稳定输出12.5 GHz信号. ...

1

... 如图2 所示,为了满足物理层25 Gb/s串口中32∶1复接器[16 ] 和行列交织器读写的时钟频率关系,即12.5 GHz∶6.25 GHz∶1.562 5 GHz∶781.25 MHz,采用较小的分频数(=16)以抑制锁相环的带内噪声. 采用781.25 MHz的时钟信号作为输入参考频率ckr . 在16级分频器中,高速二分频器选择基于电流模(current mode logic, CML)的D触发器实现VCO输出频率的二分频[17 ] ,低速二分频采用带有上拉电阻M1的真单相时钟型触发器(single phase clock type, TSPC)进行分频. 分频后,PFD对输入参考频率和反馈频率ckf 进行鉴频鉴相,控制CP的充电过程I 1 和放电过程I 2 ,通过LPF抑制控制电压的纹波,稳定输出12.5 GHz信号. ...

1

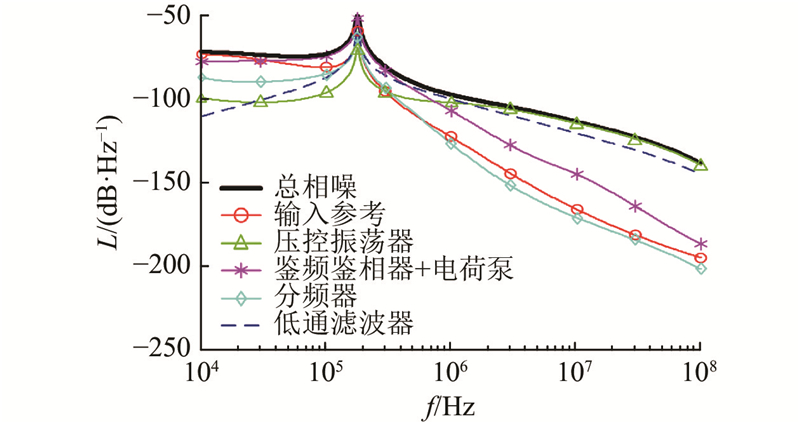

... 图3 中,PFD、CP和VCO是PLL总噪声的主要来源,分别引起VCO控制线上纹波引起的抖动D j 和VCO内部器件引起的随机抖动R j [18 ] . 下面对VCO、PFD和CP进行优化设计. ...

1

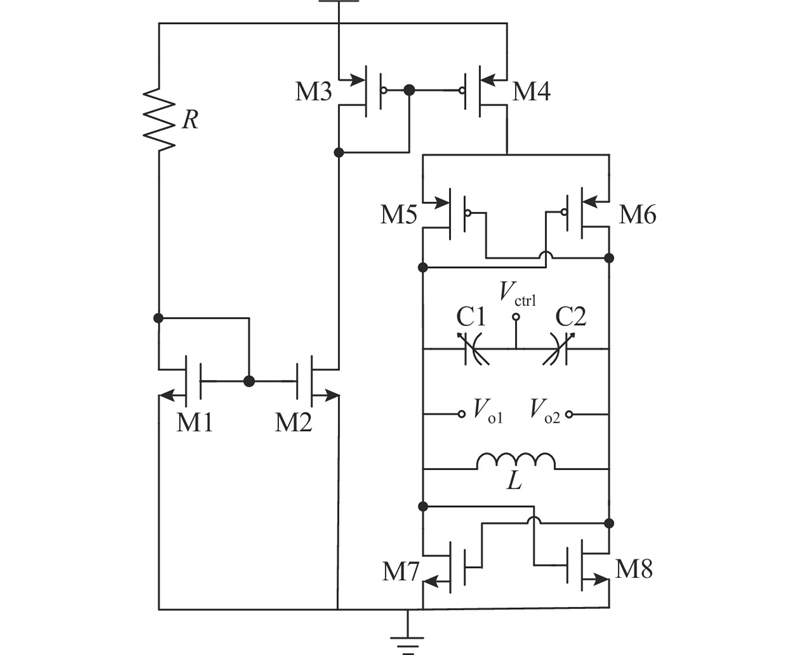

... LC-VCO CPPLL中VCO向SerDes链路提供高频时钟信号[19 ] ,VCO性能直接影响了输出信号的抖动. 如图5 所示, MOS管M1、M2、M3、M4提供恒定的尾电流,M5、M6和M7、M8构成PMOS/NMOS交叉耦合对,提供有源负阻R N . LC网络构成谐振电路,并联等效电阻R P 一般为ωL/Q ,其中ω 为角频率(=2πf 0 ),Q 为LC谐振电路的品质因数. ...

1

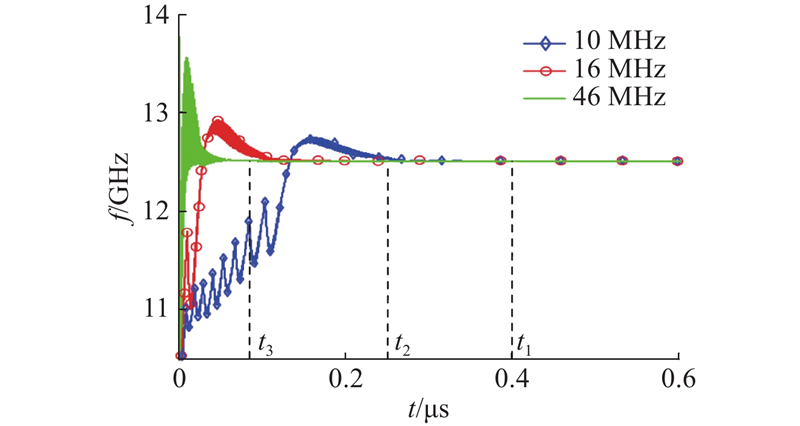

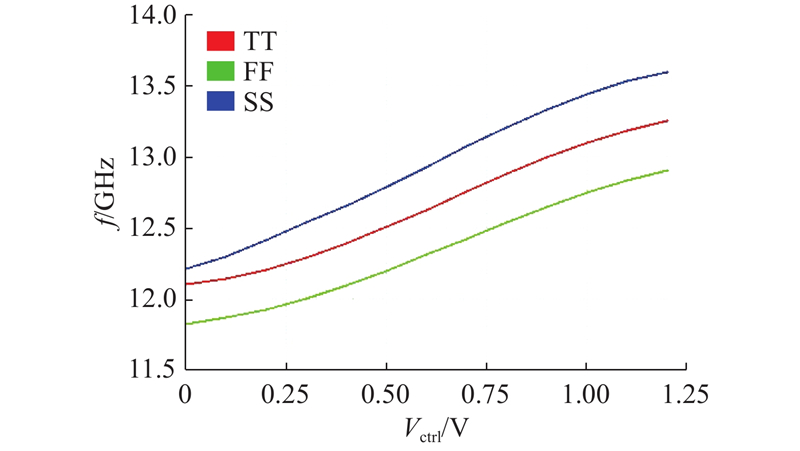

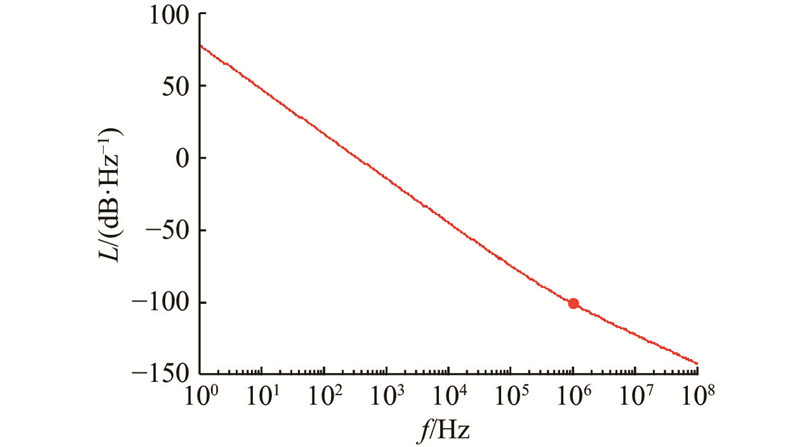

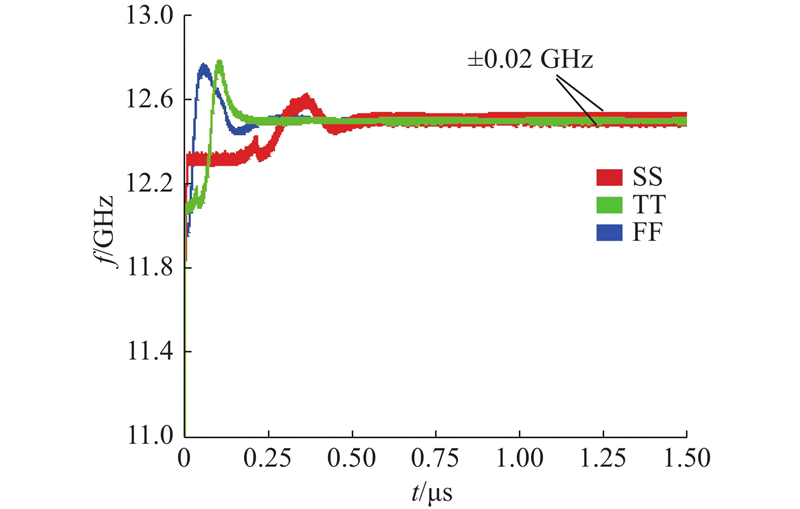

... 为了保证不同工艺角下满足振荡频率的要求,优化调谐线性度,以实现宽调谐范围,如图7 所示. 图中,V ctrl 为VCO的控制电压. 从图7 可以看出,在TT工艺角下的输出频率为12.1~13.2 GHz,完全覆盖目标频率12.5 GHz,在TT工艺角下K VCO =2π×1.125×109 rad/ (s·V). 较大的K VCO 在一定程度上恶化了相位噪声,如图8 所示. 可以看出,在1 MHz频偏处VCO的相位噪声为−101.3 dB/Hz,稍差于文献[20 ] (−113.4 dB/Hz). ...

1

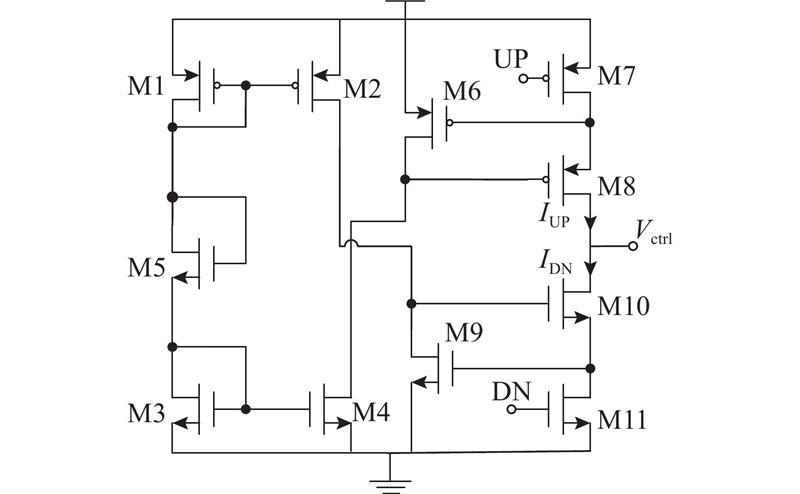

... 式中:ΔV ctrl 为控制线上纹波v (t )的电压偏离值,T dz 为控制线上纹波v (t )的时间宽度. 可以看出,在给定的振荡频率f 0 上,D j V ctrl 、T dz 及K VCO 成正比. 为了降低抖动D j [21 ] ,对CP电路中的非理想因素(如电流失配、漏电流、电荷共享等)进行优化设计. ...

1

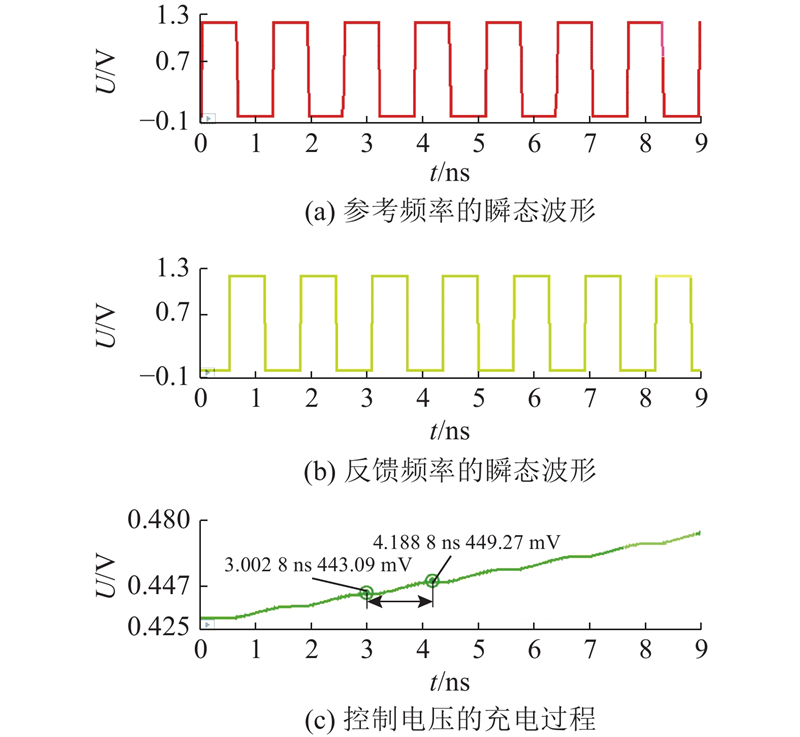

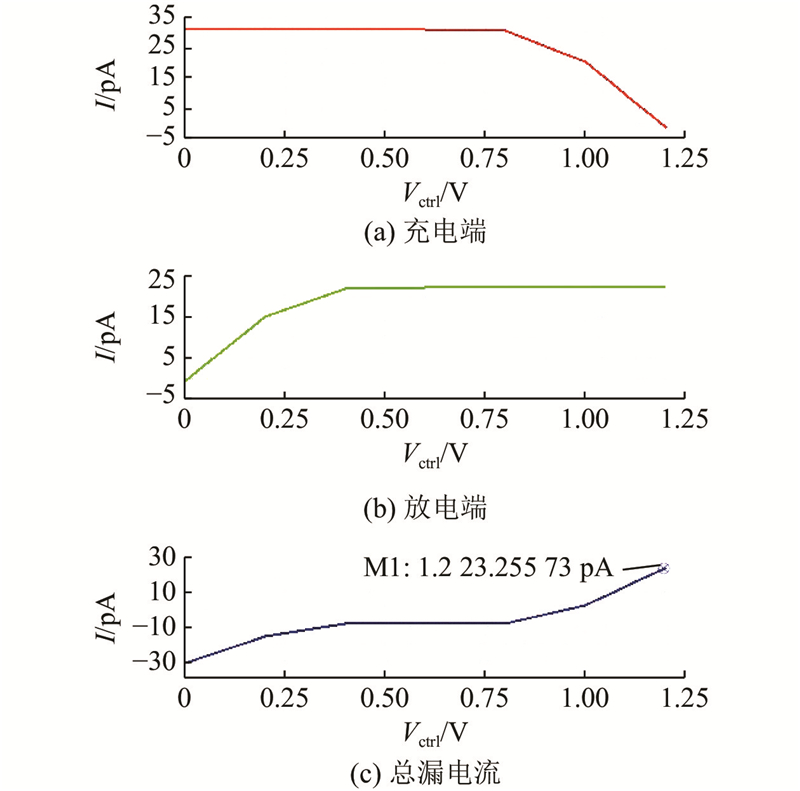

... 在共源共栅电路中,M8和M10管隔离了开关管M7/M11和LPF,以降低开关管M7和M11引起的电荷共享效应. 结合PFD电路[22 ] ,如图11 所示,图12 给出PFD和CP级联的充电放电过程. 可以看出,在开关管M7和M11开启或关断瞬间,充电电流没有尖峰电流,充电波形的线性度良好. 当控制信号关断时,电容的电压维持不变,没有较大的电压变化,因此 VCO的控制电压不会产生较大的纹波,不会造成较大的频率跳变,有利于降低输出时钟信号的抖动. M8和M10管实现了输出端与电源/地之间的隔离,减小了漏电流,如图13 所示. 可以看出,在0~1.2 V下CP的总漏电流最大为23.3 pA,说明漏电流较小,对CPPLL系统的影响可以忽略不计. 可知,CP中充放电电流失配和电荷共享均得到较好的抑制效果. ...

1

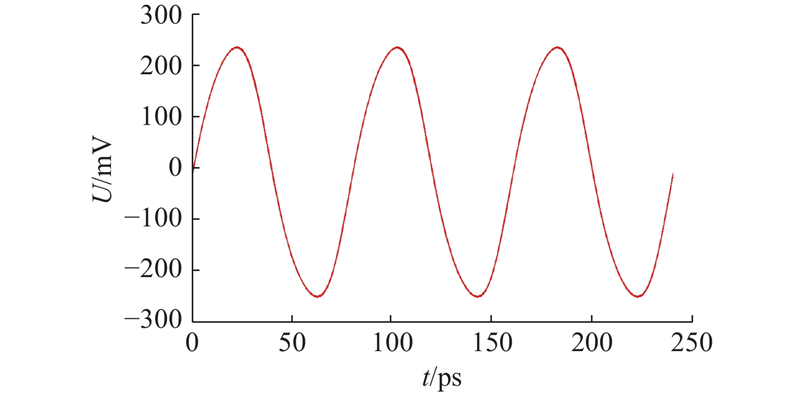

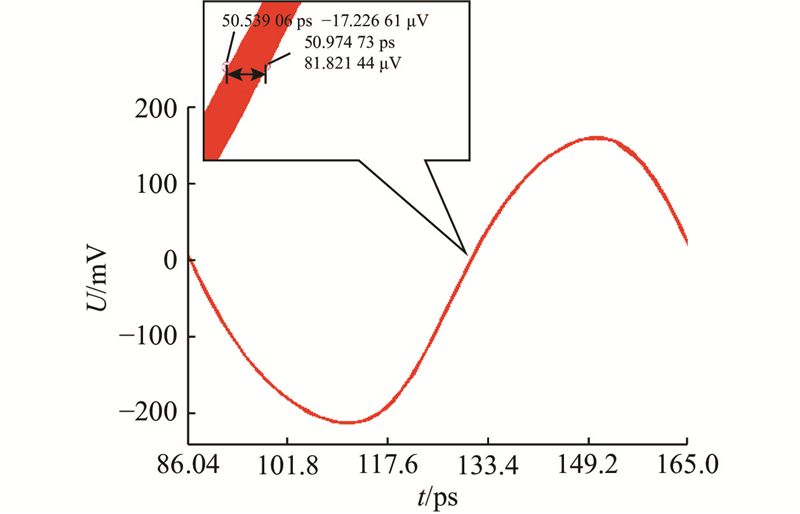

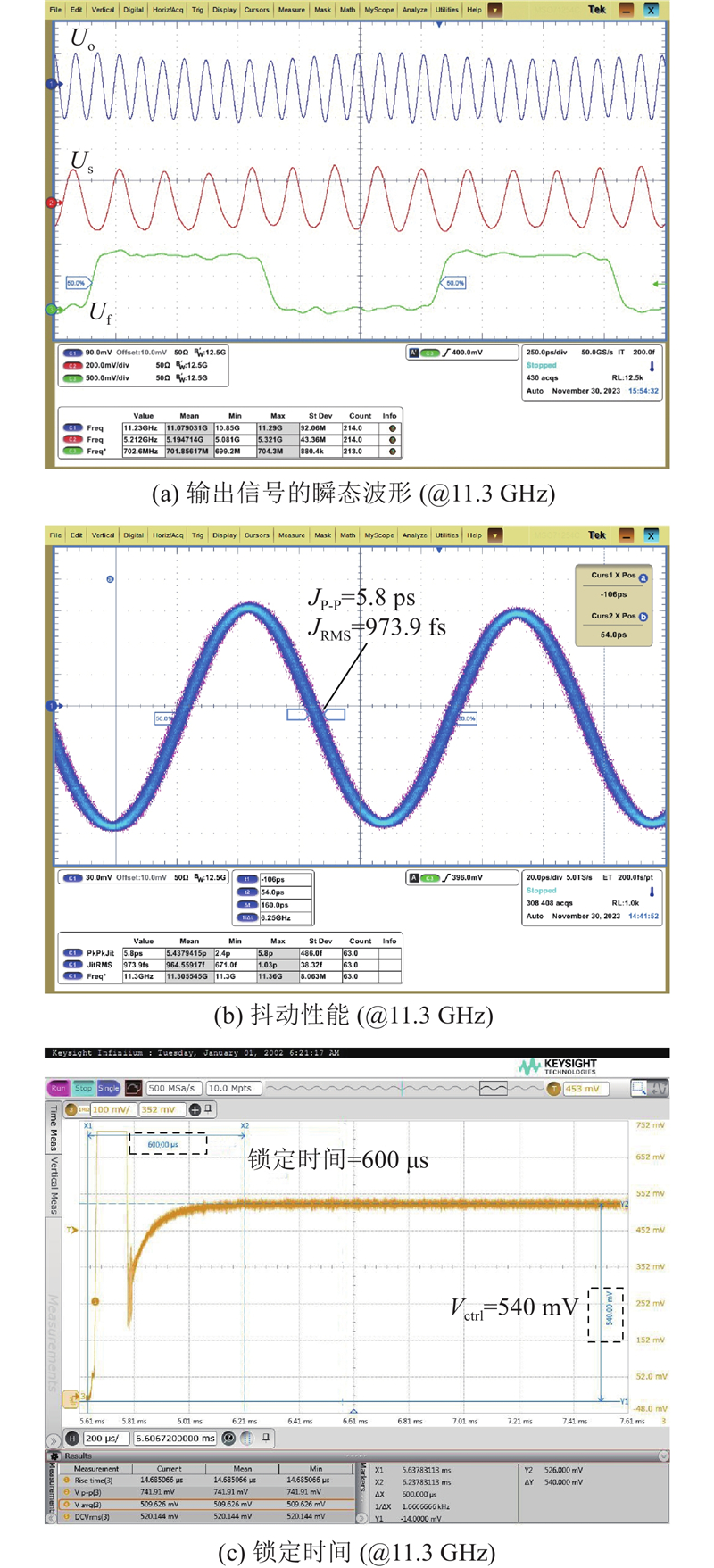

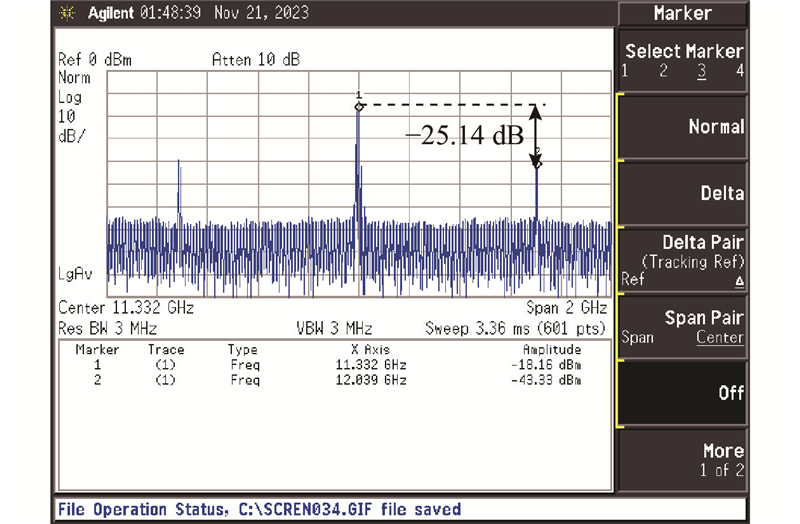

... 图18 给出参考频率为706.25 MHz时的瞬态测试,包括输出信号的瞬态波形、输出抖动性能和锁定时间. 从图18 (a)可以看出,PLL输出信号U o 、二分频输出信号U s 和反馈信号U f 的分频比是8级二分频,这说明PLL能够完成锁频和分频的功能. 从图18 (b)、(c)可以看出,当输出时钟信号的频率为11.3 GHz时,VCO输出时钟信号的峰峰抖动和RMS抖动分别是5.8 ps和973.9 fs,约为0.065 UI,而且锁定时间为600 μs,说明输出时钟频率的抖动较小,VCO能够快速地输出相对稳定的时钟频率,满足高速串行链路的应用需求[23 ] . ...

3

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... Summary and comparison of CPPLL performance using 65 nm technology

Tab.1 文献 VCO 锁频范围/GHz RMS /ps 相位噪声/(dB·Hz−1 ) 参考杂散/dB 功耗/mW 面积/mm2 FoM/dB 本文 LC 10.9~12.0 0.9739 −111.47@10 MHz −25.14 47.3 0.309 −223.5 文献[24 ] LC 1.25~3.125 2.17 — — 43.6 — −216.8 文献[25 ] LC 6.3~8.7 1.2 −116.6@1 MHz <−50 50 0.72 −161.4 文献[26 ] LC 3.6 0.043 −141.1@1 MHz −80.34 7.27 0.497 −258.7 文献[27 ] Ring 3.2 7.5 −107.9@10 MHz −45.5 2.73 0.047 −218.1 文献[28 ] Ring 1.25~3.125 1.65 — −47.63 28.8 0.384 −221.1 文献[29 ] Ring 1.2~2.5 0.25 −124.8@1 MHz −46 8.5 0.0066 −242.7

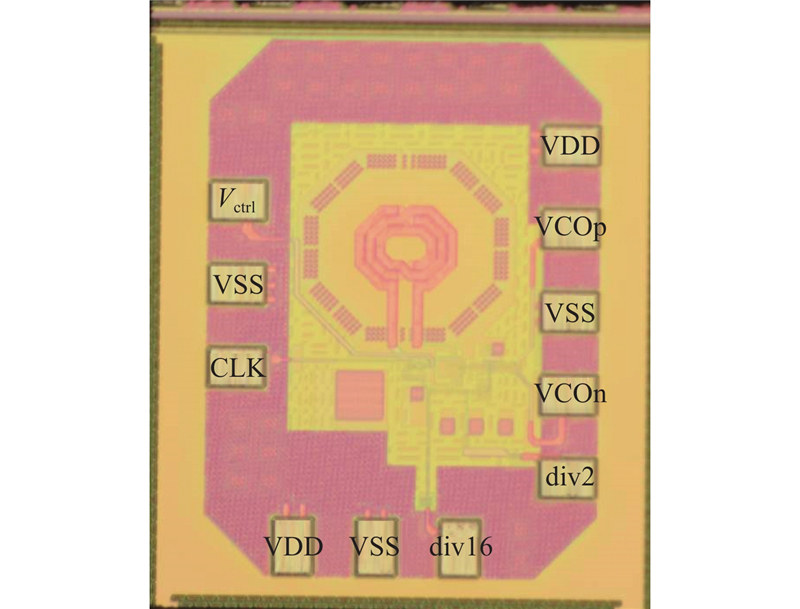

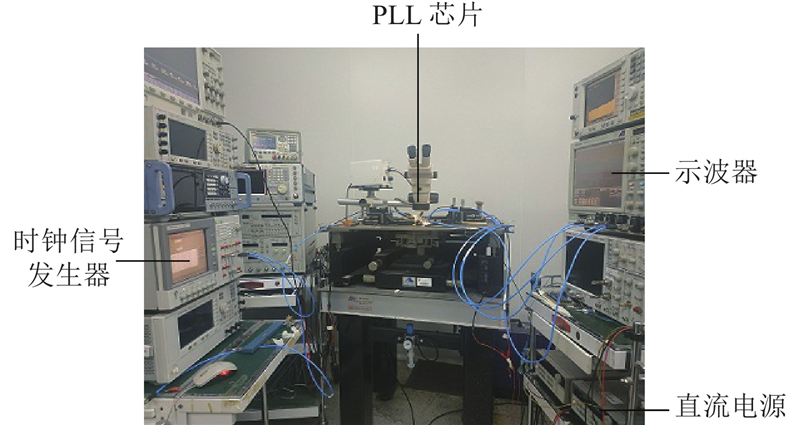

5. 结 语 本文设计基于65 nm CMOS 工艺的快锁定宽频低抖动CPPLL. 为了在保证环路稳定性的同时降低PLL的锁定时间,通过分析时域模型和频域模型获得最优的环路带宽. VCO采用交叉耦合管和尾电流技术来降低内部器件噪声,通过优化调频线性度来实现宽锁频范围. CP利用管联结构和增益提升技术,降低电路中电流失配和电荷共享的影响. 测试结果表明,CPPLL 能够实现10.9~12 GHz下的输出时钟信号. 当包括整个焊盘在内的芯片面积为0.474 6 mm×0.651 mm,电源电压为1.2 V,输入参考频率为706.25 MHz 时,电路的功耗为47.3 mW,输出时钟信号的RMS抖动是973.9 fs,约为0.065 UI,适用于20 Gb/s 及以上的高速串行链路. ...

2

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... Summary and comparison of CPPLL performance using 65 nm technology

Tab.1 文献 VCO 锁频范围/GHz RMS /ps 相位噪声/(dB·Hz−1 ) 参考杂散/dB 功耗/mW 面积/mm2 FoM/dB 本文 LC 10.9~12.0 0.9739 −111.47@10 MHz −25.14 47.3 0.309 −223.5 文献[24 ] LC 1.25~3.125 2.17 — — 43.6 — −216.8 文献[25 ] LC 6.3~8.7 1.2 −116.6@1 MHz <−50 50 0.72 −161.4 文献[26 ] LC 3.6 0.043 −141.1@1 MHz −80.34 7.27 0.497 −258.7 文献[27 ] Ring 3.2 7.5 −107.9@10 MHz −45.5 2.73 0.047 −218.1 文献[28 ] Ring 1.25~3.125 1.65 — −47.63 28.8 0.384 −221.1 文献[29 ] Ring 1.2~2.5 0.25 −124.8@1 MHz −46 8.5 0.0066 −242.7

5. 结 语 本文设计基于65 nm CMOS 工艺的快锁定宽频低抖动CPPLL. 为了在保证环路稳定性的同时降低PLL的锁定时间,通过分析时域模型和频域模型获得最优的环路带宽. VCO采用交叉耦合管和尾电流技术来降低内部器件噪声,通过优化调频线性度来实现宽锁频范围. CP利用管联结构和增益提升技术,降低电路中电流失配和电荷共享的影响. 测试结果表明,CPPLL 能够实现10.9~12 GHz下的输出时钟信号. 当包括整个焊盘在内的芯片面积为0.474 6 mm×0.651 mm,电源电压为1.2 V,输入参考频率为706.25 MHz 时,电路的功耗为47.3 mW,输出时钟信号的RMS抖动是973.9 fs,约为0.065 UI,适用于20 Gb/s 及以上的高速串行链路. ...

A 3.6-GHz type-II sampling PLL with a differential parallel-series double-edge S-PD scoring 43.1-fs RMS jitter, ?258.7-dB FOM, and ?75.17-dBc reference spur

5

2023

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... Summary and comparison of CPPLL performance using 65 nm technology

Tab.1 文献 VCO 锁频范围/GHz RMS /ps 相位噪声/(dB·Hz−1 ) 参考杂散/dB 功耗/mW 面积/mm2 FoM/dB 本文 LC 10.9~12.0 0.9739 −111.47@10 MHz −25.14 47.3 0.309 −223.5 文献[24 ] LC 1.25~3.125 2.17 — — 43.6 — −216.8 文献[25 ] LC 6.3~8.7 1.2 −116.6@1 MHz <−50 50 0.72 −161.4 文献[26 ] LC 3.6 0.043 −141.1@1 MHz −80.34 7.27 0.497 −258.7 文献[27 ] Ring 3.2 7.5 −107.9@10 MHz −45.5 2.73 0.047 −218.1 文献[28 ] Ring 1.25~3.125 1.65 — −47.63 28.8 0.384 −221.1 文献[29 ] Ring 1.2~2.5 0.25 −124.8@1 MHz −46 8.5 0.0066 −242.7

5. 结 语 本文设计基于65 nm CMOS 工艺的快锁定宽频低抖动CPPLL. 为了在保证环路稳定性的同时降低PLL的锁定时间,通过分析时域模型和频域模型获得最优的环路带宽. VCO采用交叉耦合管和尾电流技术来降低内部器件噪声,通过优化调频线性度来实现宽锁频范围. CP利用管联结构和增益提升技术,降低电路中电流失配和电荷共享的影响. 测试结果表明,CPPLL 能够实现10.9~12 GHz下的输出时钟信号. 当包括整个焊盘在内的芯片面积为0.474 6 mm×0.651 mm,电源电压为1.2 V,输入参考频率为706.25 MHz 时,电路的功耗为47.3 mW,输出时钟信号的RMS抖动是973.9 fs,约为0.065 UI,适用于20 Gb/s 及以上的高速串行链路. ...

2

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... Summary and comparison of CPPLL performance using 65 nm technology

Tab.1 文献 VCO 锁频范围/GHz RMS /ps 相位噪声/(dB·Hz−1 ) 参考杂散/dB 功耗/mW 面积/mm2 FoM/dB 本文 LC 10.9~12.0 0.9739 −111.47@10 MHz −25.14 47.3 0.309 −223.5 文献[24 ] LC 1.25~3.125 2.17 — — 43.6 — −216.8 文献[25 ] LC 6.3~8.7 1.2 −116.6@1 MHz <−50 50 0.72 −161.4 文献[26 ] LC 3.6 0.043 −141.1@1 MHz −80.34 7.27 0.497 −258.7 文献[27 ] Ring 3.2 7.5 −107.9@10 MHz −45.5 2.73 0.047 −218.1 文献[28 ] Ring 1.25~3.125 1.65 — −47.63 28.8 0.384 −221.1 文献[29 ] Ring 1.2~2.5 0.25 −124.8@1 MHz −46 8.5 0.0066 −242.7

5. 结 语 本文设计基于65 nm CMOS 工艺的快锁定宽频低抖动CPPLL. 为了在保证环路稳定性的同时降低PLL的锁定时间,通过分析时域模型和频域模型获得最优的环路带宽. VCO采用交叉耦合管和尾电流技术来降低内部器件噪声,通过优化调频线性度来实现宽锁频范围. CP利用管联结构和增益提升技术,降低电路中电流失配和电荷共享的影响. 测试结果表明,CPPLL 能够实现10.9~12 GHz下的输出时钟信号. 当包括整个焊盘在内的芯片面积为0.474 6 mm×0.651 mm,电源电压为1.2 V,输入参考频率为706.25 MHz 时,电路的功耗为47.3 mW,输出时钟信号的RMS抖动是973.9 fs,约为0.065 UI,适用于20 Gb/s 及以上的高速串行链路. ...

A self-biased low-jitter process-insensitive phase-locked loop for 1.25Gb/s-6.25Gb/s SerDes

2

2018

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... Summary and comparison of CPPLL performance using 65 nm technology

Tab.1 文献 VCO 锁频范围/GHz RMS /ps 相位噪声/(dB·Hz−1 ) 参考杂散/dB 功耗/mW 面积/mm2 FoM/dB 本文 LC 10.9~12.0 0.9739 −111.47@10 MHz −25.14 47.3 0.309 −223.5 文献[24 ] LC 1.25~3.125 2.17 — — 43.6 — −216.8 文献[25 ] LC 6.3~8.7 1.2 −116.6@1 MHz <−50 50 0.72 −161.4 文献[26 ] LC 3.6 0.043 −141.1@1 MHz −80.34 7.27 0.497 −258.7 文献[27 ] Ring 3.2 7.5 −107.9@10 MHz −45.5 2.73 0.047 −218.1 文献[28 ] Ring 1.25~3.125 1.65 — −47.63 28.8 0.384 −221.1 文献[29 ] Ring 1.2~2.5 0.25 −124.8@1 MHz −46 8.5 0.0066 −242.7

5. 结 语 本文设计基于65 nm CMOS 工艺的快锁定宽频低抖动CPPLL. 为了在保证环路稳定性的同时降低PLL的锁定时间,通过分析时域模型和频域模型获得最优的环路带宽. VCO采用交叉耦合管和尾电流技术来降低内部器件噪声,通过优化调频线性度来实现宽锁频范围. CP利用管联结构和增益提升技术,降低电路中电流失配和电荷共享的影响. 测试结果表明,CPPLL 能够实现10.9~12 GHz下的输出时钟信号. 当包括整个焊盘在内的芯片面积为0.474 6 mm×0.651 mm,电源电压为1.2 V,输入参考频率为706.25 MHz 时,电路的功耗为47.3 mW,输出时钟信号的RMS抖动是973.9 fs,约为0.065 UI,适用于20 Gb/s 及以上的高速串行链路. ...

A dividerless ring oscillator PLL with 250fs integrated jitter using sampled low pass filter

4

2020

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...

... ,29 ],这主要受功耗的影响. ...

... Summary and comparison of CPPLL performance using 65 nm technology

Tab.1 文献 VCO 锁频范围/GHz RMS /ps 相位噪声/(dB·Hz−1 ) 参考杂散/dB 功耗/mW 面积/mm2 FoM/dB 本文 LC 10.9~12.0 0.9739 −111.47@10 MHz −25.14 47.3 0.309 −223.5 文献[24 ] LC 1.25~3.125 2.17 — — 43.6 — −216.8 文献[25 ] LC 6.3~8.7 1.2 −116.6@1 MHz <−50 50 0.72 −161.4 文献[26 ] LC 3.6 0.043 −141.1@1 MHz −80.34 7.27 0.497 −258.7 文献[27 ] Ring 3.2 7.5 −107.9@10 MHz −45.5 2.73 0.047 −218.1 文献[28 ] Ring 1.25~3.125 1.65 — −47.63 28.8 0.384 −221.1 文献[29 ] Ring 1.2~2.5 0.25 −124.8@1 MHz −46 8.5 0.0066 −242.7

5. 结 语 本文设计基于65 nm CMOS 工艺的快锁定宽频低抖动CPPLL. 为了在保证环路稳定性的同时降低PLL的锁定时间,通过分析时域模型和频域模型获得最优的环路带宽. VCO采用交叉耦合管和尾电流技术来降低内部器件噪声,通过优化调频线性度来实现宽锁频范围. CP利用管联结构和增益提升技术,降低电路中电流失配和电荷共享的影响. 测试结果表明,CPPLL 能够实现10.9~12 GHz下的输出时钟信号. 当包括整个焊盘在内的芯片面积为0.474 6 mm×0.651 mm,电源电压为1.2 V,输入参考频率为706.25 MHz 时,电路的功耗为47.3 mW,输出时钟信号的RMS抖动是973.9 fs,约为0.065 UI,适用于20 Gb/s 及以上的高速串行链路. ...

A 10.6-mW 26.4-GHz dual-loop type-II phase-locked loop using dynamic frequency detector and phase detector

1

2020

... 如表1 所示为本文设计的CPPLL测试结果,并与近几年65 nm CPPLL的研究成果进行比较,其中,文献[24 ~26 ]是采用LC-VCO结构实现的,文献[27 ~29 ]采用的是Ring-VCO结构. 表中,FoM为品质因数[30 ] . 从表1 可以看出,在锁频范围和面积上,LC结构PLL高于Ring结构PLL. 本文中的高调谐线性度使得锁频范围宽于文献[26 ],但由于CP电流匹配范围有限,且本文未采用调谐电容阵列和自适应带宽,本文的锁频范围低于文献[24 ,25 ]. 尽管本文对VCO和CP进行了优化,但是VCO中的尾电流源结构增加了热噪声,缺少滤波处理和PVT补偿电路,且本文的频率最高,使得相位噪声高于文献[26 ,29 ]. 从FoM上来看,本文的FoM值接近于文献[28 ],仅次于文献[26 ,29 ],这主要受功耗的影响. ...