随着5G时代的到来,电子设备小型化成为了必然趋势. 电子设备中的电源模块通常分为低压差稳压器(low dropout regulator, LDO)与开关模式电压转换器2种,其中开关电源内部含有具备储能功能的电感器与电容器元件. 提高开关电源的工作频率是降低无源元件取值的主要方法,但更快的开关速度往往意味着更大的开关损耗和更加复杂的驱动器结构. 根据能量传输方式可以将开关电源拓扑分为开关电感式[1]、开关电容式[2]、谐振式[3]. 前两者的功率开关采用硬开关工作,且需要较大的无源元件值来控制输出纹波. 而谐振式转换器的功率开关在理想情况下可以在任意频率下工作. 在以零电压开启(zero voltage switching, ZVS)为代表的软开关状态下,其谐振元件也可以在较高开关频率下设计为较小的数值,有利于同时实现高集成度与高效率. 单开关谐振转换器(single switch resonant converter, SSRC)以简单的驱动方式和较少的无源元件数量成为功率电子领域的研究热点[4-8]. 不过,目前文献所报道的大部分单片集成式转换器输出功率均低于10 W [9-12],且多为用于外部芯片供电的低压芯片.

本研究首次尝试实现单片集成的谐振式DC-DC转换器,使用硅基半导体工艺结合耐受高工作电压的氮化镓功率管设计了高开关频率的驱动电路与功率转换电路,研究其输出功率和转换效率的影响因素. 该设计可以应用在48 V/12 V混合电源新能源汽车发光二极管(light emitting diodes, LEDs)系统的供电设备中.

1. 集成方案

1.1. 硅基SOI技术与谐振电感器

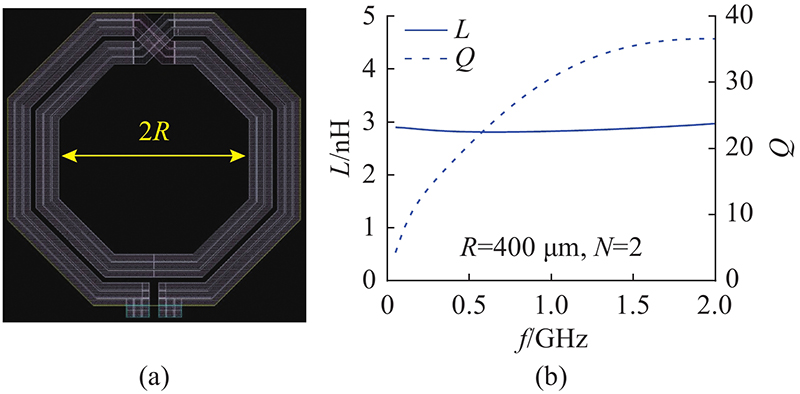

硅基绝缘体上硅(silicon on insulator, SOI)工艺如今被广泛应用在射频集成电路与电源管理芯片设计中,具有与硅基体互补金属氧化物半导体(complementary metal oxide semiconductor, CMOS)工艺的良好兼容性,被称为 “21世纪的硅基集成技术”. 硅基SOI工艺平台已经被证明可以实现高性能的高频电感器[13-14]. SOI PMOS(positive channel metal oxide semiconductor)与NMOS(negative channel metal oxide semiconductor)件之间无需若干隔离层分隔从而减小了寄生电容,硅片通过智能切割(smart-cut)技术薄技术制备可以得到具有较小栅极寄生电容的薄顶层硅片,因此SOI器件拥有更高的开关速率,适合于高频谐振转换器驱动电路的设计. SSRC电路功率转换的功能是通过谐振电感与谐振电容的能量存放实现的. 电感器作为磁性储能元件,通常占据着大部分低频功率电子电路的体积,而在特高频转换器中,小尺寸低功耗的电感器对转换器的性能影响明显. 电感器的关键指标包括等效直流电阻Rac、电感L、在给定工作频率下的品质因数Q(Q = ωL/Rac,ω为工作角频率)以及自谐振频率SRF等. 对于谐振式开关电路,传输基波(开关频率)能量是首要要求,因此电感器须在工作频率处具备准确的电感、较高的品质因数(即较低的直流电阻),同时在满足上述要求条件下最好具有较大的版图线宽以防止电感中的电流纹波损坏元件. 在本研究的设计中,根据130 nm SOI工艺库中的功率电感器选择电路工作频率. 硅基SOI工艺中共提供3种厚金属电感器,分别为平面螺旋电感、半周平面螺旋电感和对称式平面螺旋电感,其中对称式平面螺旋电感器具有可选择的2圈绕线或3圈绕线结构从而可以得到更宽的电感范围. 为了简化命名,分别将绕线2圈和3圈的电感器表示为“PSI2”和“PSI3”. 如图1(a)所示为PSI2电感版图结构,如图1(b)所示为PSI2电感在螺旋电感最内圈的半径R=400 μm时的电感与品质因数在0~2.0 GHz频段内随频率f变化的情况. 图中,N为螺旋电感金属圈数. 可以看出,当PSI2电感器在500 MHz以上频率工作时,品质因数高于20,电感波动较小,表示电感器具有相对小的交流焦耳功耗,2圈的走线使得总的金属宽度不低于120 μm,从而保证该电感器可以通过较大的交流电流.

图 1

图 1 对称式螺旋电感器PSI2版图以及PSI2的电感与品质因数随频率变化示意图

Fig.1 Layout of symmetrical spiral inductor PSI2 and its inductance and quality factor versus operating frequency

如图2(a)、(b)所示分别为PSI3电感器的版图示意图和内半径为400 μm时电感与品质因数在0~2 GHz频段内随频率的变化情况. 可以看出,PSI3电感器的品质因数在工作频率为0.5~2.0 GHz时也可以达到20以上,但电感却存在约3 nH的变动,这可能是因为3圈厚金属的走线使得电感器具有较大的寄生电容从而降低了电感器的自谐振频率. 由电感-电容谐振网络的频率特性可知,电感器在自谐振频率附近工作时具有较大的电压放大能力,但同时其特征阻抗随频率变化更加剧烈,将这种电感器应用在谐振式变换器中会导致谐波电流的幅度被明显放大从而导致转换器的损耗增加.

图 2

图 2 对称式螺旋电感器PSI3版图以及PSI3的电感与品质因数随频率变化示意图

Fig.2 Layout of symmetrical spiral inductor and its inductance and quality factor versus operating frequency

1.2. 氮化镓功率管与三维集成

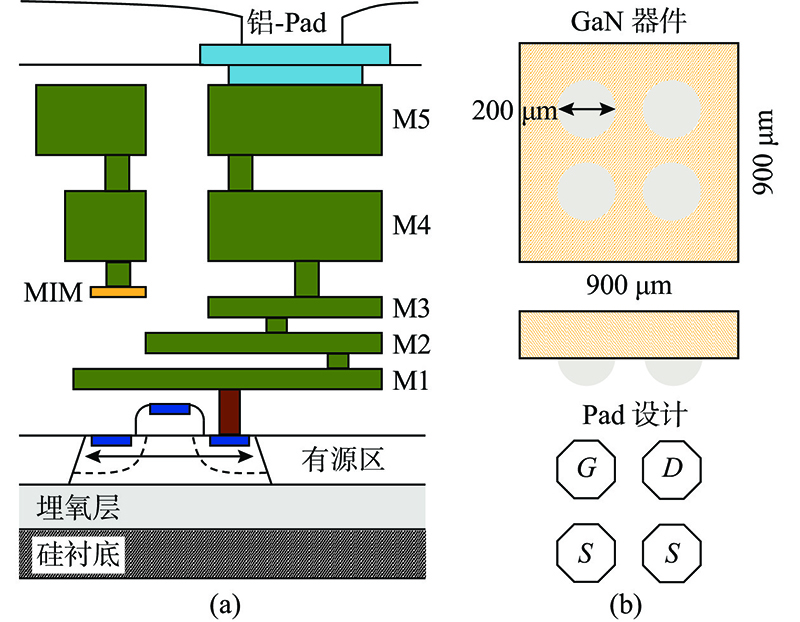

采用宜普电源转换公司制造的EPC2036器件作为功率开关与二极管. 该器件在源极与漏极之间并联一个额外的续流二极管用以在器件关断时通过反向电流,将源极与栅极端子短接即可让器件始终保持关断而同时使并接的二极管保持导通. 连接硅基芯片与分立器件的方式有2种,分别为平面键合与三维堆叠. 前者的工艺流程类似于芯片的键合过程,即用金线将芯片上的I/O Pad与印刷电路板上对应的焊盘连通,这种方法具有较大的设计自由度和容错率,因为片外连接的器件类型与尺寸完全可以按照键合所用电路板/衬底材料的焊盘位置修改. 但拉金丝键合的方式所使用的细度为几十微米的金线具有较大的寄生电感,其数量级在nH量级,相当于在转换器回路之间多引入了较大的电感器,这样会使得谐振电感的电感不准确进而导致转换器性能的恶化. 为了解决寄生效应的问题,很多高频转换器采用集成无源器件(integrated passive device,IPD)工艺平台实现[15],功率器件倒装在表面,通过IPD平台的高阻硅衬底上喷镀的低耗金属线连接,有效解决了寄生效应的问题. 但是,IPD平台较昂贵,且无法与主流硅基CMOS工艺兼容,驱动芯片也须通过倒装连接的方式接入,增加了系统的工艺复杂度. 三维堆叠技术最初应用于微波射频电路,其思路是把射频芯片与数字控制芯片通过垂直方向上的触点连接在一起,触点材料为导电率高的金属材质且为直径仅几十微米的球状材料,大大降低了寄生引起的信号衰减. 2017年三维堆叠技术首次被应用在一款40 MHz开关频率的片上降压转换器设计中[16],耗尽型GaN芯片与硅基驱动 / 控制芯片通过直径50 μm的锡球封装在一起,通过评估,每个锡球仅具有15 pF的寄生电感,几乎不会产生电压波形抖动与功率衰减,该设计实现了最高550 mW/mm2的片上功率密度. 2019年该技术又一次被成功应用于一款3.3 V转70.0 V的高转换比升压转换器中,实现了291 mW/mm2的片上功率密度[17].

图 3

图 3 硅基SOI工艺结构截面图与GaN器件EPC2036的尺寸信息

Fig.3 Cross-sectional sketch view of silicon based SOI process and size information of GaN device (EPC2036)

2. 转换器参数设计

2.1. 驱动级电路设计

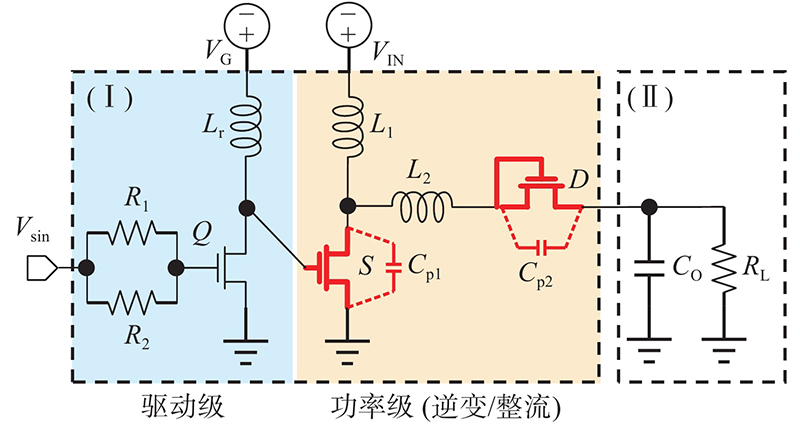

本研究所设计的转换器采用的电路是并联式Class-E拓扑,功率管栅极驱动器采用谐振式驱动器,电路原理图如图4所示. 图中,Ⅰ区域为片上实现电路,Ⅱ区域为片外测试电路,Vsin为外部正弦输入信号,VG、VIN分别为驱动级部分和功率级部分的电源电压,L1、L2为谐振电感器,Cp1、Cp2为谐振电容器,CO为输出滤波电容,RL为负载电阻.

图 4

图 4 全谐振式并联Class-E转换器原理图

Fig.4 Schematic diagram of full resonant parallel Class-E converter

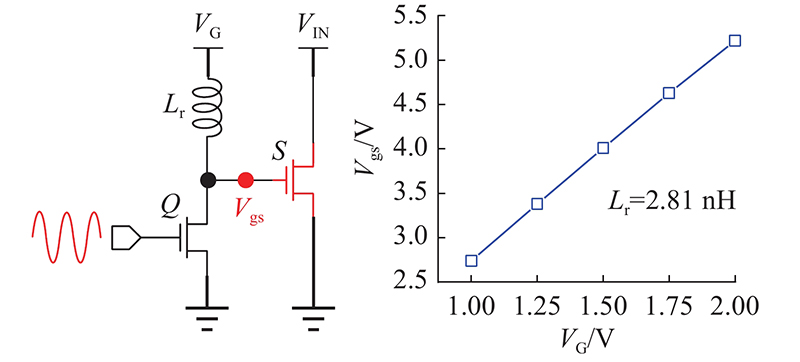

原理图中驱动级电路仅包含驱动NMOS的 Q管、谐振储能电感器Lr、驱动管栅极限流电阻R1、R2. 功率管S与二极管D采用GaN器件EPC2036[18]. 该驱动器利用驱动管Q关断期间谐振电感Lr与功率管S输入寄生电容的谐振使S开启. 谐振电压可以达到VG的2.2倍,具体放大倍数由Lr与功率管输入寄生电容的谐振频率决定,Lr的取值随开关频率的增加而减小. PSI2电感最小为2.81 nH,氮化镓器件的输入寄生电容约为75 pF,这样计算得到两者的谐振频率为346 MHz(0.692倍开关频率). 如图5所示为不同电源电压VG情况下最高驱动电压幅值的仿真结果. 可以看出,当VG = 1.5 V时,功率管栅-源电压摆幅即可达到4.0 V,为了避免实际转换器中振铃与毛刺导致的电压过冲损坏功率器件,选择VG = 1.5 V作为驱动器电源电压. 500 MHz的方波信号含有GHz级的高次谐波,很难通过数字系统准确生成,因此,采用正弦波作为Q管的驱动信号,正弦波的直流偏置电压略高于Q管的开启阈值电压以保证驱动管的开关占空比接近0.5.

图 5

图 5 谐振驱动器在不同电源电压下输出电压的最高摆幅

Fig.5 Max output voltage swing of resonant gate driver under different source voltage

2.2. 功率级电路设计

为了提高片上转换器系统的集成度,整个芯片的面积不可过大,应尽量减少无源元件的数量. 根据图4中的拓扑,转换器功率级电路包括L1-C1和L2-C22个谐振网络共4个谐振元件. 谐振电感作为功率传输通路的必要元件不可忽略,本研究尝试将2个谐振电容C1和C2在500 MHz的开关频率用功率器件S和D的寄生电容Cp1和Cp2替代,这样可以省略较大面积的片上电容占据的芯片面积,最大化地发挥功率器件的效用从而提升整个GaN转换器系统的功率密度. 因此,功率级电路设计的初始条件如下:

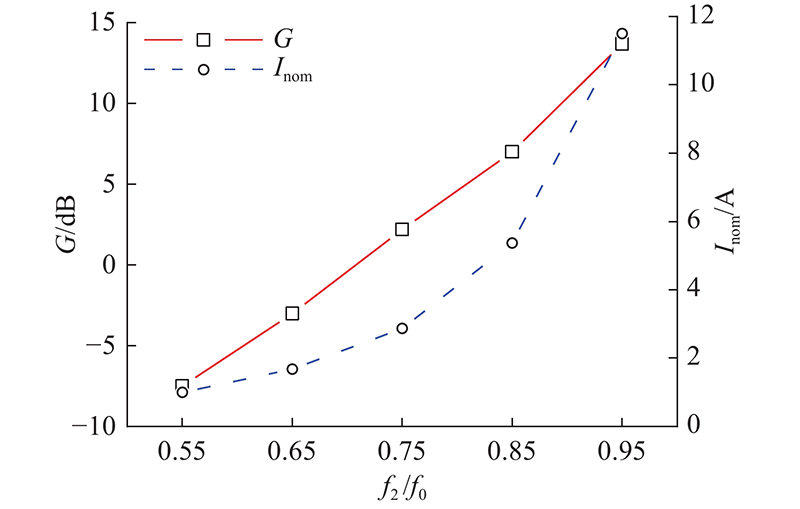

Cp1、Cp2可以通过器件的数据表查阅得到,此处电容为75 pF. 根据目标电压增益,在已知谐振电容C2数值的情况下首先对L2-C2-RL谐振网络的电压增益进行扫描. 获得较大电压增益的代价是谐振电感中较大的电流幅度,这样会增加电感器的交流焦耳功耗,因此在设计谐振电感L2数值的同时也要兼顾电流纹波的大小,最后在2个指标之间进行折中设计. 如图6所示为RL=50 Ω时谐振网络的电压增益G与归一化谐振电流Inom的值. 图中,f2为L2-C2的谐振频率,f0为开关频率. 可以看出,f2越接近f0,网络的电压增益越大,同时L2中的谐振电流幅度也越大,这是因为当输入信号的频率(f0)与网络谐振频率接近时谐振网络对其呈现的阻抗较小. 为了保证较大的电压增益同时避免谐振电流幅值超过10 A,本研究取f2 = 0.88 f0,此时可以计算得到谐振电感为1.73 nH. 查阅工艺手册可知可以用2个并联的内半径为475 μm的PSI2电感器实现该谐振电感,这样的设计可以将电感器中的谐振电流幅值均分到2个独立的电感器中,保证转换器正常工作的能力.

图 6

图 6 谐振网络的电压增益和谐振电流幅值随f2/f0的变化

Fig.6 Voltage gain and amplitude of resonant current versus f2/f0 of resonant tank

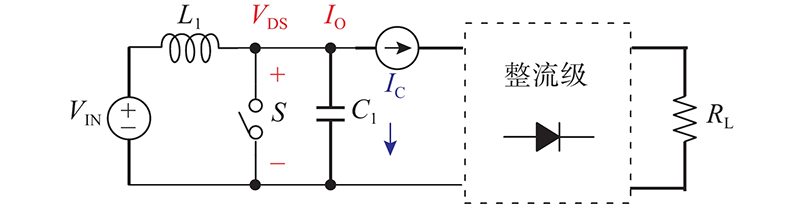

分析L1-C1谐振网络的设计方法,首先根据电瞬态电路分析推导功率管漏-源电压VDS的表达式,本研究仅考虑基波电流的传输,分析所用电路模型如图7所示. 图中,IC为通过电容C1的电流.

图 7

图 7 并联Class-E转换器逆变级电路分析模型

Fig.7 Analysis model of inverter stage circuit in parallel Class-E converter

根据正弦电流假设,逆变级电路输出电流IO可以表达为

式中:ω0为开关频率的角频率,IAC为谐振电流的幅值,φ为初始相位. 根据基尔霍夫定律,当功率开关S断开时,VDS表达式为

式(3)为一阶非齐次线性方程,其通解可以写为

代入如下边界条件来确定2个常系数CA、CB:

式中:

系数

式中:ω1、Z1分别为谐振元件L1、C1的谐振角频率和特征阻抗. 从而式(4)中仅剩下IAC与φ为未知量,初始相位的数值与图7中的整流级网络输入阻抗有关,即并联L2-C2-RL谐振网络的输入阻抗. 根据推导,整流级网络的输入阻抗Z2可以表达为

因此对于频率为f0的正弦电压输入信号,可以将谐振电流的初始相位表示为

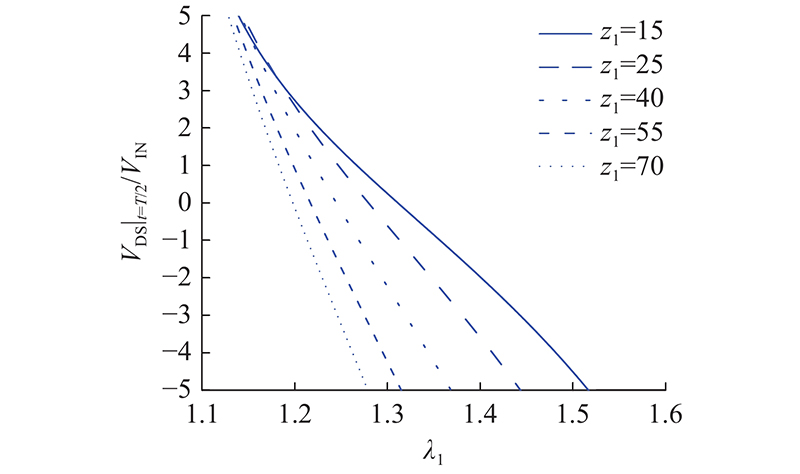

谐振电流中包含基波与同相位的高次谐波电流分量,另外整流级输入电压的基频分量也难以直接计算,因此无法通过基频处的输入阻抗准确确定IAC. 为了保证ZVS的工作性能,VDS的波形在开关从关断切换到开启的瞬间或之前的时刻须降到0 V,即VDS|t=T/2 = 0. 将RL= R0代入式(10)可以确定

图 8

图 8 谐振网络L1-C1谐振频率低于开关频率时功率管开启瞬间的VDS与L1-C1特征阻抗的关系

Fig.8 Relationship between VDS and characteristic impedance of L1-C1 with resonant frequency of L1-C1 lower than switching frequency

图 9

图 9 谐振网络L1-C1谐振频率高于开关频率时功率管开启瞬间的VDS与L1-C1特征阻抗的关系

Fig.9 Relationship between VDS and characteristic impedance of L1-C1 with resonant frequency of L1-C1 higher than switching frequency

表 1 驱动级、功率级电路元件取值与选型

Tab.1

| 变量 | 数值 | 备注 |

| Lr/nH | 2.81 | PSI2电感器,R = 400 μm |

| L1/nH | 8.1 | PSI3电感器,R = 500 μm |

| L2/nH | 1.73 | PSI2电感器,R = 475 μm |

| C1/pF | 75 | GaN HEMT寄生电容 |

| C2/pF | 75 | GaN HEMT寄生电容 |

2.3. 版图设计

在高功率密度转换器设计中,支路电流密度是制约芯片设计的重要因素,为了保证转换器正常工作且具有较长的使用寿命,回路中的电流必须低于按照手册计算出的最高耐流值. 如表2所示为本研究所用130 nm SOI工艺中主要金属层与I/O Pad铝金属在不同温度下的最高电流线密度,其中M1~M5分别表示第1~5层金属. 表中,Tm为金属层温度,Amax为最大电流密度.

表 2 各金属层在85、110、125 ℃时的最大电流线密度

Tab.2

| (mA·μm−1) | |||

| 金属层 | Amax | ||

| Tm=85 ℃ | Tm=110 ℃ | Tm=125 ℃ | |

| M1 | 5.88 | 1.34 | 1.14 |

| M2、M3 | 7.94 | 1.81 | 1.14 |

| M4、M5 | 77.48 | 17.63 | 11.08 |

| Pad | 31.64 | 7.20 | 3.23 |

图 10

3. 仿真分析

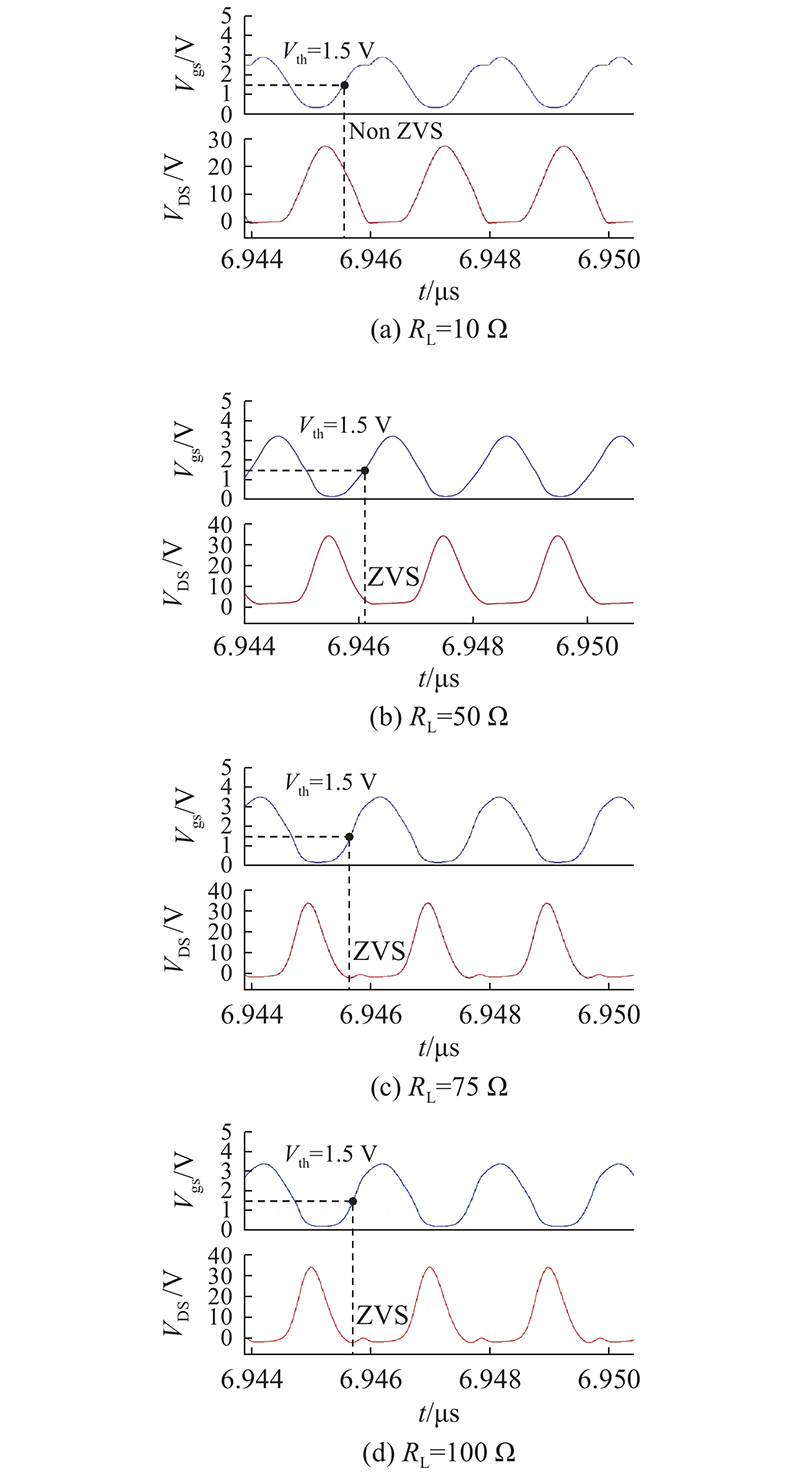

给出所设计的全谐振式并联Class-E升压转换器的仿真结果与分析,并与文献中的同类设计进行对比. 仿真原理图在Cadence Virtuoso软件里搭建,结合GaN器件EPC2036的spectre模型进行时域仿真,观察转换器的瞬态响应与软开关情况. 如图11所示为输入电压为12 V时,负载电阻RL = 10、 50、75、100 Ω时的驱动器输出电压Vgs波形和功率管漏-源电压VDS波形. 图中,Vth为EPC2036器件的栅极开启阈值电压,对于以二维电子气为沟道导通机制的功率器件来说,当Vgs > Vth时器件即可实现双向导通. 显然,当RL等于设计值R0 = 50 Ω时,转换器可以恰好工作在ZVS状态,而当RL > 50 Ω时,软开关特性依旧可以保持,且具有一定的时间裕度.

图 11

图 11 不同负载电阻下仿真得到的Vgs电压与VDS电压波形

Fig.11 Simulated Vgs and VDS waveforms at different load resistance values

由图11可以看出,当RL = 10 Ω时驱动电压Vgs的波形存在一段平缓的阶段,这是接在功率器件漏极与栅极之间的米勒电容(Cgd)所导致的. 在功率晶体管开通的过程中,漏-源电压持续下降,在Vgs超过阈值电压Vth后的一段时间内,功率管工作状态进入饱和区,可以等效为一个电流源负载的共源放大器,其电压增益为Au,米勒电容在功率管漏极与栅极之间起到了负反馈的作用,由于米勒效应该电容被放大了(1+Au)倍,造成Vgs电压上升缓慢. 当负载电阻较大时,VDS波形下降到0 V的时刻在功率开关开启之前,因此当功率管开通时VDS已经降到Vth以下,功率管工作在线性区失去放大功能,从而避免了米勒效应.

图 12

图 12 不同负载下的输出电压以及输出电压纹波

Fig.12 Simulated output voltage waveforms and ripples at different load resistance values

如图13所示为输入电压恒定时转换器的输出电压VOUT、转换效率η与负载电阻的关系,负载电阻越大则输出电压越高,这也是谐振网络L2-C2-RL的电压增益变化所导致的. 同时转换器重载下的效率可以达到89%,而在轻载情况下转换器虽然能保持ZVS工作但转换效率却不断降低,这是因为谐振回路中较大的交流电流纹波导致了较大的谐振电感器中的焦耳损耗和二极管的导通损耗.

图 13

图 13 转换器输出电压与转换效率随负载的变化

Fig.13 Output voltage and conversion efficiency versus load resistance

若仅考虑开关频率的基波分量对损耗的贡献,二极管导通损耗PD和电感器焦耳损耗PL可以分别表示为

式中:ID_+为通过二极管的正向电流平均值;VF为二极管的正向导通压降,可以通过查阅器件手册得到,本研究所用EPC2036器件的VF = 2.2 V;Rac与Rdc表示谐振电感器的交流等效电阻和金属线寄生电阻;Irms表示支路电流有效值.

式中:N为螺旋电感圈数(PSI2:N = 2,PSI3:N = 3),W为螺旋电感走线宽度,rtop为顶层金属的电阻率.

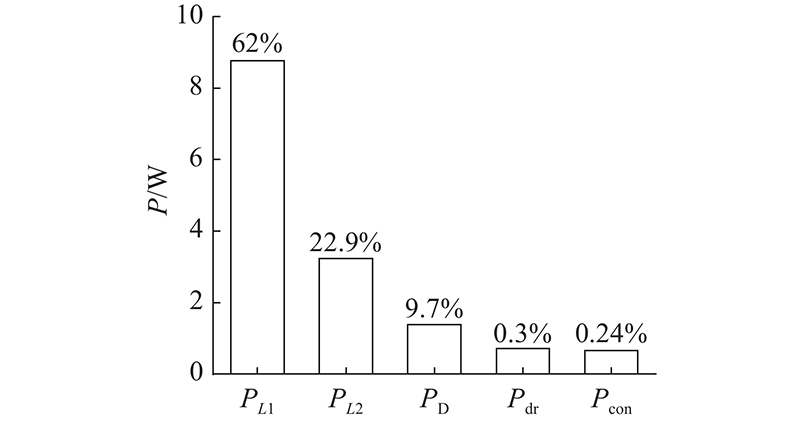

如图14所示为VIN = 12 V、RL = 50 Ω时的功耗构成情况. 图中,PL1为L1电感的功耗,PL2为L2电感的功耗,PD为二极管导通损耗,Pdr为驱动损耗,Pcon为功率管与二极管的导通电阻损耗. 可以看出,谐振电感L1、L2分别占了总功耗的62.0%、22.9%,谐振式驱动器的损耗仅为0.72 W. 这也表明本设计中的损耗主要来源于电感器的走线电阻,对于片上集成式全谐振转换器来说,低耗谐振电感器或谐振腔的研发具有很重要的意义,须同时满足储能需求与较高的集成度. 如表3所示,对比本设计与最近文献中报道的片上DC-DC转换器的性能. 表中,f为频率,VOUT/VIN为转换比,Pden为功率密度,A为面积. 与开关电感式转换器相比,本设计所用并联Class-E转换器中的元件均为谐振元件,且功率器件的寄生电容能够得到最大程度的利用,在相近输出功率水平的情况下本设计具有更高的转换效率. 与开关电容式转换器相比,本设计无需堆叠密度很高的片上电容器,可以实现更高的输出功率和工作电压,同时本设计仅含有单个功率开关,驱动器设计简单且更容易实现软开关工作.

图 14

图 14 转换器功耗构成以及占比

Fig.14 Compositions and percentages of power consumption of converter

表 3 本研究所提出的设计与相关设计的指标对比

Tab.3

| 设计 | f/MHz | 拓扑 | VOUT/VIN | 工艺 | Pden/(W·mm−2) | A/mm2 | η/% |

| 本研究 | 500.0 | 并联Class-E | 12.0 V/20.0 V | 130 nm SOI+GaN | 1.480 | 9.00 | 60 |

| Burkhart等[5] | 75.0 | 并联Class-E | 12.0 V/30.0 V | PCB | 0.012 | − | 87 |

| Liu等[15] | 300.0 | 并联Class-E | 12.0 V/18.0 V | IPD+GaN | 0.048 | 92.00 | 47 |

| Pilsoon等[1] | 680.0 | 开关电感 | 12.0 V/20.0 V | GaN-on-SiC | 0.240 | 9.00 | 39 |

| Mclaughln等[19] | 47.5 | 开关电容 | 4.4 V/2.2 V | 180 nm CMOS | 0.097 | 8.93 | 75 |

| Nghia等[20] | 450.0 | 开关电容 | 1.2 V/0.6 V | 65 nm CMOS | 0.730 | 0.65 | 78 |

4. 结 语

为了提高电源管理模块的集成度和功率密度,减小无源元件的体积,促进车载照明系统之类的功率电子进一步小型化,首次基于硅基130 nm SOI工艺平台与氮化镓高电子迁移率功率管设计实现了一款500 MHz开关频率、12 V输入电压、输出功率高于10 W的片上单开关谐振式升压DC-DC转换器. 转换器中的谐振电感器使用硅基SOI工艺中顶层厚金属电感器实现,谐振电容器使用功率开关管与二极管的寄生电容实现,最大化利用了器件的寄生效应与芯片面积. 具体给出了谐振驱动电路、功率级转换电路中各个元件的设计依据,通过合理的版图布局将整个转换器电路在9 mm2的芯片上实现,氮化镓功率管与二极管采用垂直方向低寄生倒装的方式与片上电路连接,提高了系统集成度. 仿真结果显示,该片上转换器可以在较宽负载范围内实现软开关ZVS工作,具有良好的负载响应功能,满载时片上功率密度可以达到1.48 W/mm2,转换效率为60%. 与片上开关电感式转换器相比,本设计中的转换器因工作在软开关状态而具有较高的效率,与片上开关电容式转化器相比,本设计不受片上电容器密度限制,可以实现较大的输出功率. 在未来的工作中须进一步减小片上元件的损耗,比如优化电感器的结构使其走线长度更短、使用可集成式的低导通压降功率肖特基二极管,提高整个转换器的效率.

参考文献

A fully integrated inductor-based GaN boost converter with self-generated switching signal for vehicular applications

[J].DOI:10.1109/TPEL.2016.2518183 [本文引用: 2]

Circuit techniques for high efficiency fully-integrated switched-capacitor converters

[J].DOI:10.1109/TCSII.2020.3046514 [本文引用: 1]

基于GaN器件的固态射频源应用研究

[J].

Research on applications of solid-state RF power supply based on GaN devices

[J].

A single-stage LED driver based on flyback and modified Class-E resonant converters with low-voltage stress

[J].DOI:10.1109/TIE.2018.2890502 [本文引用: 1]

Design methodology for a very high frequency resonant boost converter

[J].DOI:10.1109/TPEL.2012.2202128 [本文引用: 1]

Variable switching frequency ON-OFF control for Class-E DC-DC converter

[J].

A family of high frequency single-switch DC-DC converters with low switch voltage stress based on impedance networks

[J].

A fully integrated Li-ion-compatible hybrid four-level DC-DC converter in 28-nm FDSOI

[J].

A fully integrated buck regulator with 2-GHz resonant switching for low-power applications

[J].DOI:10.1109/JSSC.2018.2840513 [本文引用: 1]

Physical models of planar spiral inductor integrated on the high-resistivity and trap-rich silicon-on-insulator substrates

[J].DOI:10.1109/TED.2017.2700022 [本文引用: 1]

A miniature 300-MHz resonant DC-DC converter with GaN and CMOS integrated in IPD technology

[J].DOI:10.1109/TPEL.2017.2788946 [本文引用: 2]

Hybrid CMOS/GaN 40-MHz maximum 20-V input DC-DC multiphase buck converter

[J].DOI:10.1109/JSSC.2017.2672986 [本文引用: 1]

Heterogeneous integration of GaN and BCD technologies and its applications to high conversion-ratio DC-DC boost converter IC

[J].DOI:10.1109/TPEL.2018.2859419 [本文引用: 1]

Fully integrated switched-inductor-capacitor voltage regulator with 0.82-A/mm2 peak current density and 78% peak power efficiency

[J].DOI:10.1109/JSSC.2020.3036394 [本文引用: 1]