随着无线通信需求的不断增长,无线局域网(WLAN)被更加广泛地应用在计算机、移动手持设备以及物联网等各种高速无线通信场景中. 传输速率最高可达10 Gbps的WLAN标准802.11ax(Wi-Fi 6) 越来越普及[1-2]. 为了实现更高的通信速率,Wi-Fi 6协议引入更高阶的调制技术(1024QAM)和正交频分多址(orthogonal frequency division multiple access,OFDMA),这也给射频前端中的功率放大器(power amplifier,PA)设计提出新的重大挑战. 更高阶的调制对误差矢量幅度(error vector magnitude,EVM)的要求更高,须更严格控制PA的调幅至调幅(amplitude–amplitude,AM-AM) 、调幅至调相(amplitude–phase,AM-PM)失真. OFDMA技术的子载波更多,使得峰值平均功率比(peak to average power ratio,PAPR)更高,PA须在更大的功率回退区间工作,以避免峰值信号进入非线性区引起严重失真[3]. 商用Wi-Fi 6 PA须在放大1024QAM的MCS11信号时,仍然能在EVM小于−40 dB时有较大的平均输出功率[4].

1. 功率放大器的分析与设计

1.1. 非线性分析

当输入信号的PAPR较大时,PA往往会在峰值功率处进入AB类工作状态以同时实现较高的效率和线性度. 随着输入功率逐渐减小到平均功率甚至更低时,PA会逐渐进入A类工作状态. 在A类到AB类的转变过程中,静态偏置受到输入信号的影响增大,PA的动态电流上升,晶体管结电容Cbe、Cce、Cbc和结温都随之变化,引起输入输出阻抗以及β值的变化. 上述过程中的波形失真加剧也会使输出信号谐波分量增大. 工作状态的变化将使PA增益和输出信号相位随着输出功率变化而变化,引起AM-AM和AM-PM失真.

简单的有源偏置电路难以对偏置电压的补偿进行精细控制,会使增益在高输出功率时产生增益扩张. 定义ΔG为PA增益,

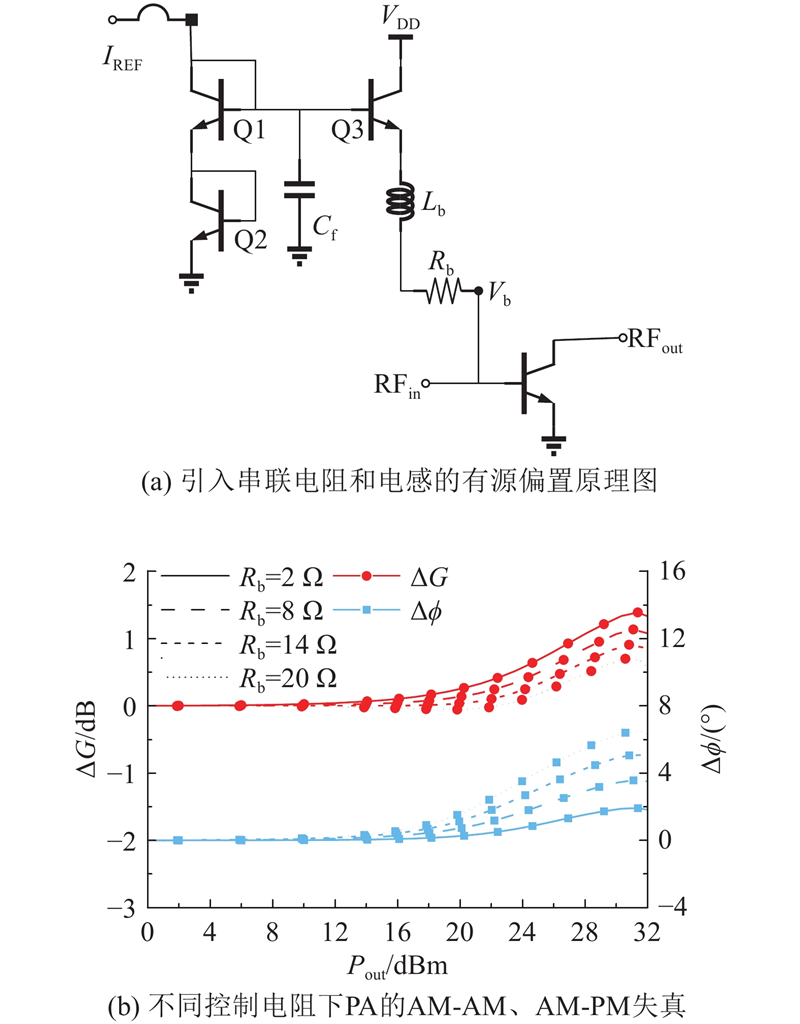

图 1

当输入功率增加时,由于旁路电容Cf的滤波作用,二极管连接的晶体管Q1、Q2将使VQ3b保持相对稳定,而Ib和VQ3be将分别增大和减小. 当VQ3be减小过多引起增益扩张时,可以通过增大Rb进行补偿,或者通过增大Lb抑制Q3处的整流效应,从而控制IbRb和VQ3be的变化幅度,保持Vb的相对稳定. 如图1 (b)所示,Rb可以有效减少AM-AM失真,同时也会增大AM-PM失真. 电阻加大到一定程度后,会出现中功率增益压缩而高功率增益扩张的现象,因此确定Rb大小需要多方面的衡量. Lb对线性度的影响与Rb类似,但是幅度更小. 此外,Lb的引入减小了射频信号的泄露,能够略微提高放大器增益. 在多级放大器中,各级偏置的VDD通常是共用的,Lb与Cf共同作用,可以进一步减小各级放大器之间的射频串扰.

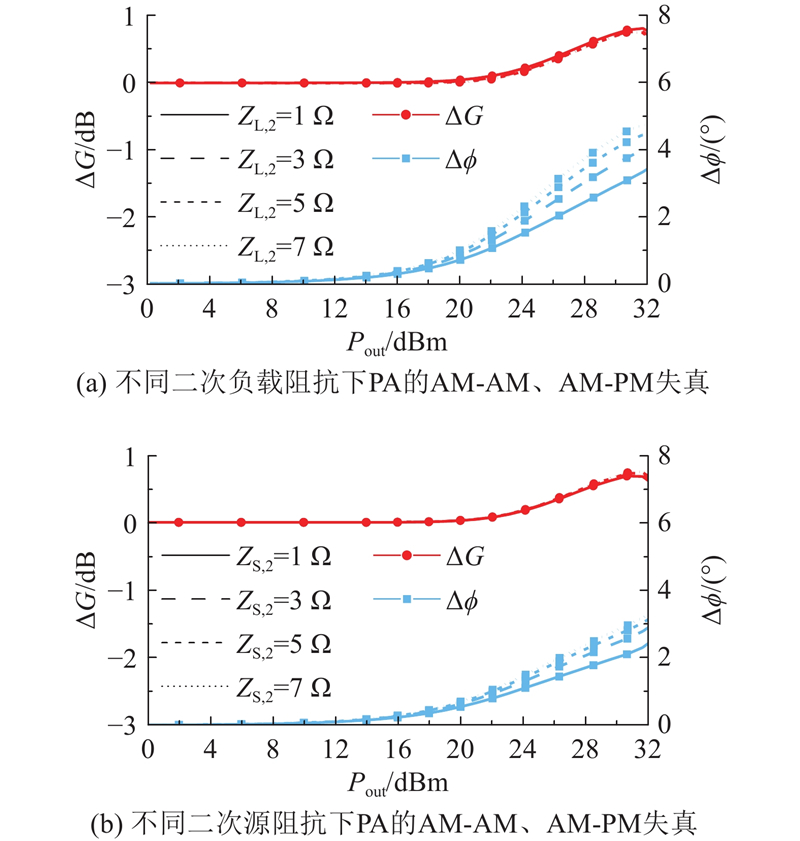

尽管有源偏置电路能在高输出功率时保持晶体管的偏置电压,使PA增益不至于太早压缩,但是为了兼顾效率,放大器在大功率情况下仍会进入AB类甚至深AB类工作状态. 此时AB类放大器的输出信号将会包含大量的谐波分量,这是引起信号失真的重要因素. 对于工作在深AB类模式的功率放大器来说,二次谐波电流是所有谐波中最强的,因此对二次谐波进行抑制是优化功率放大器线性度的有效方法[16-17]. 以由24个尺寸为3 μm×30 μm×2的HBT组成的单级共源功率放大器为例. 使用有源偏置负载,令基波负载阻抗ZL,为6+j×0不变,当二次谐波负载阻抗ZL,2从7 Ω逐渐降低到1 Ω时,如图2 (a)所示,AM-AM不变而AM-PM失真在30 dBm处由4.6°降至2.9°. 二次谐波的抑制可以提高基波信号功率在射频输出功率中的占比,因此降低ZL,2后,功率附加效率(power added efficiency, PAE)也提高了2.6个百分点. 除了在负载处进行二次谐波短路处理,在晶体管基极处进行二次谐波抑制也对降低AM-PM失真有一定效果. 输出阻抗不变,当二次谐波源阻抗ZS,2从7 Ω逐渐降低到1 Ω时,如图2 (b)所示,AM-AM不变而AM-PM失真在30 dBm处由2.9°进一步降至2°.

图 2

图 2 二次谐波控制对功率放大器线性度的影响

Fig.2 Effect of second harmonic control on power amplifier linearity

LC串联谐振到地是常见的在指定频率形成低阻抗的方式之一,在设计谐振电路时需要平衡好谐振的带宽和深度,带宽和深度主要由电容容值、电感感值和电感的品质因子Q值决定. 将LC串联电路等效为理想电感电容和寄生电阻R串联,Q为电感在基波处的感抗与寄生电阻之比,ω0为工作频带的中心频率,二次谐波阻抗Z2和基波阻抗ZF分别表示为

工作频带内任一频率ω1处对应的二次谐波阻抗为

令D=2ω1−2ω02 / ω1,

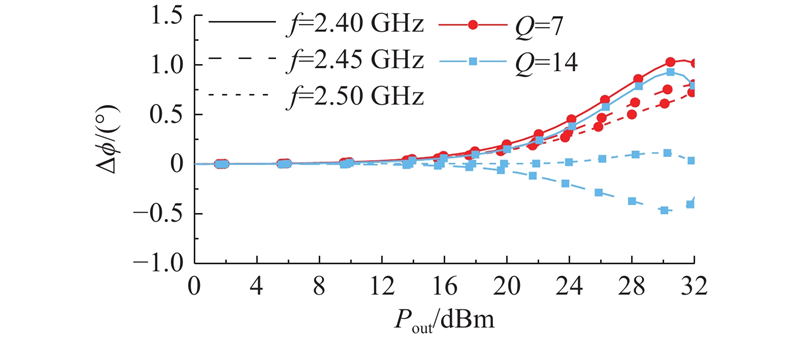

从式(5)可以看出,Q值越高,L越小,则R越小,那么LC谐振频点处对应的二次谐波阻抗Z2的幅值就会越小. 当L过于小时,串联谐振电路的基波阻抗ZF将接近Z2,意味着谐振电路在基波处提供了一个近似短路,对基频信号影响太大. 式(5)说明频带边缘的阻抗幅值与中心频率阻抗幅值之比与Q值正相关,图2显示,无论是二次负载阻抗还是二次源阻抗,阻抗越小,AM-PM 对阻抗变化越敏感,表明高Q值虽然能使中心频点的AM-PM进一步降低,也将增大AM-PM随频率变化的幅度. 当工作频带为2.4~2.5 GHz时,D/ω0约为0.081,若Q=7,那么边缘频点和中心频点对应的二次谐波阻抗幅值之比约为1.15,若Q=14,这一比值就会达到1.51,此时即使只考虑功率级源端的LC谐振,AM-PM也已经随频率出现明显变化,如图3所示. 因此想要在整个频带内使AM-PM得到有效且一致的降低,LC谐振电路的Q值不能太高,在有限Q值下尽量减小L,尤其是当管芯面积较大、输入输出阻抗较小时,匹配能接受更小的到地阻抗.

图 3

图 3 LC谐振电路中电感品质因子对调幅至调相的影响

Fig.3 Effect of quality factor on amplitude-phase in LC resonant circuit

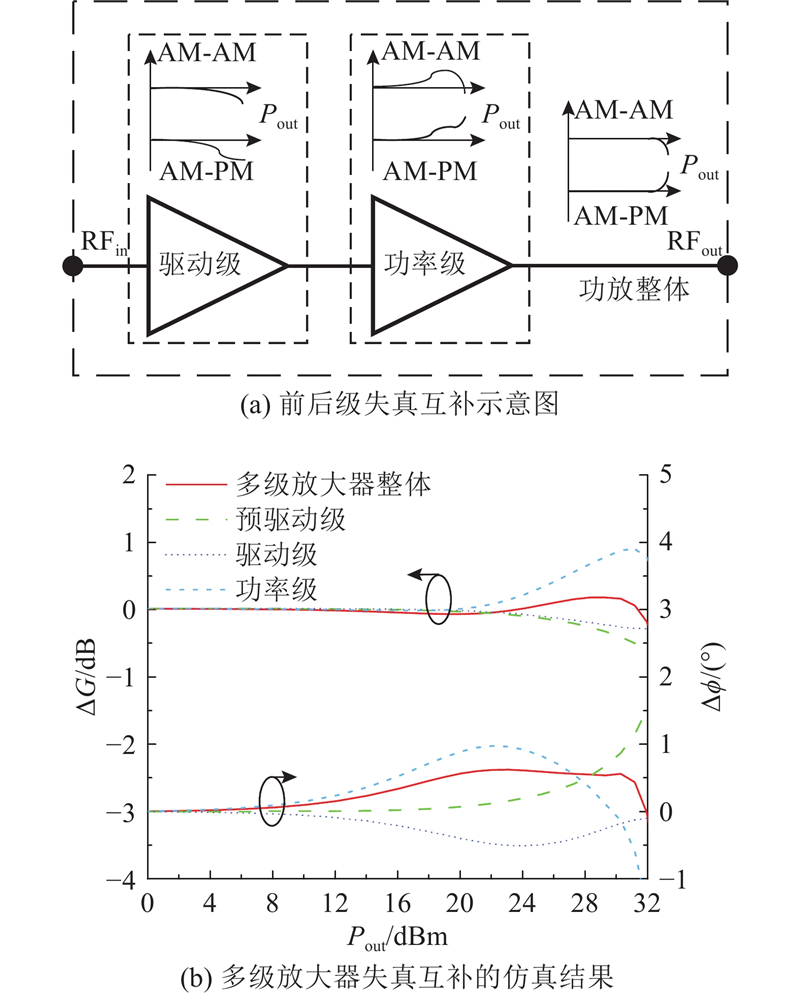

在多级放大器中,功率级的晶体管尺寸大,受制于静态电流和工作效率的要求,高功率输出时须进入深AB类工作状态. 就本研究使用的GaAs HBT工艺而言,在2.4 GHz频段,即使考虑级间匹配的插损,采用共源结构的功率级也可以实现大于10 dB的增益,因此驱动级的输出功率可以比功率级小10 dBm,晶体管尺寸可以是功率级的1/4甚至1/8. 如果是三级放大器,预驱动级的输出功率可以比功率级小20 dBm,尺寸在1/20左右就能充分推动功率级. 由于驱动级的尺寸较小,可以通过调整偏置使晶体管进入AB类工作的功率点延后,显著改变AM-AM、AM-PM失真的幅度,并且可以通过相反的失真响应来对功率级进行补偿,从而让多级功率放大器的整体线性度进一步得到优化,如图4 (a)所示. 在利用前级进行补偿时,偏置须结合具体的晶体管尺寸进行相应调节,当驱动级的最大输出功率留有余量时,驱动级失真较大的功率区间不被使用,因此补偿幅度相对较小;反之补偿就较大,对整体线性度的影响就越大. 当驱动级的补偿有限时,可以进一步添加预驱动级实现更有效的补偿. 如图4 (b)所示为多级互补的仿真实现,通过预驱动级和驱动级的共同补偿,整体PA的AM-AM失真由功率级的0.85dB降至0.15dB,AM-PM由1°降至0.6°,同时实现了较低的失真和较高的增益. 功率级为了保证足够的饱和输出,偏置电阻和负载阻抗都较小,主要对AM-PM失真进行优化,保留一定的AM-AM上翘. 预驱动级由于管芯面积小且有充足的饱和输出功率上的余量,设计了较高偏置电流和镇流电阻,预留一定的增益压缩,负载阻抗主要偏向减小AM-PM失真选择,减弱偏置电阻增大对AM-PM失真的影响. 驱动级与预驱动级的效果类似,为了充分推动功率级,对AM-AM的补偿效果较弱. 由于版图结构更简单,前两级设计LC串联谐振降低二次源阻抗,功率级为了管芯中各晶体管阻抗更加统一,晶体管基极处只加入较小的到地电容,在设计输出匹配时对二次负载阻抗进行控制,使得三级的AM-PM失真都控制在较低的水平.

图 4

图 4 多级放大器中调幅至调幅、调幅至调相失真的前后级互补

Fig.4 Complementation of amplitude-amplitude and amplitude-phase distortions in multistage amplifier

1.2. 输出匹配

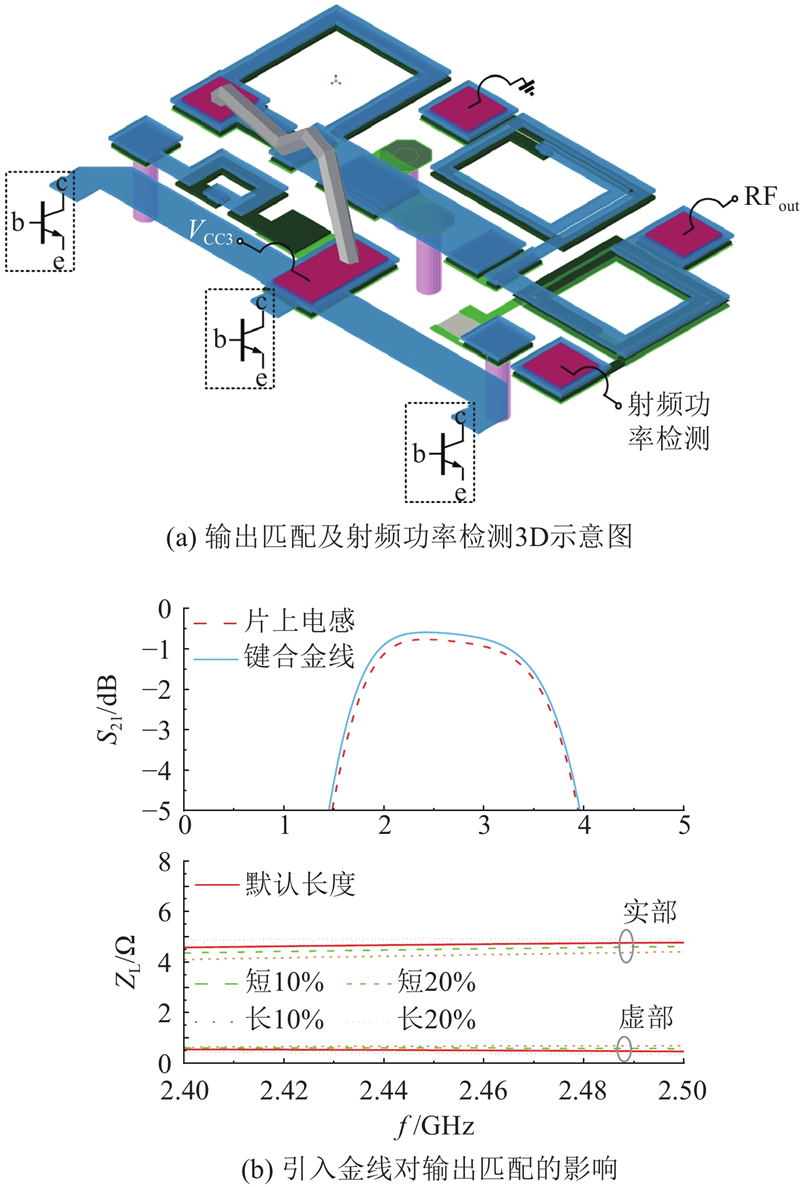

本研究使用的GaAs HBT工艺采用三层金属互联,MET1为薄金属,方块电阻为0.026 0 Ω;MET2和MET3为厚金属,方块电阻为0.006 5 Ω. 输出匹配的结构如图5 (a)所示,为了使功率级各个晶体管的负载阻抗接近,先用宽度为55 μm的MET3进行功率合成;利用LC谐振提供二次谐波短路,再用两阶L形匹配在基波提供所需负载阻抗并形成一定的带通滤波效果;在PA输出端以直接耦合的方式实现耦合系数为15 dB的射频功率检测. 为了减小耦合器对输出匹配的影响,用第三层厚金属在匹配的输出端添加一段宽走线,再通过一二层金属串联绕线在第三层金属正下方进行射频耦合. 将耦合器一端通过50 Ω电阻与地孔相连,以调整射频耦合的输出阻抗. 为了在有限面积内尽量减小输出匹配的损耗,分别在直流供电处和两阶LC匹配的电感处引入键合金线. 由于寄生电容和寄生电阻都相对较小,金线可以等效为高Q值的电感. 就本设计使用的三层互联金属而言,即使是两层厚金属并联绕制的电感,在2.4 GHz的Q值也难以达到25,ADS软件的EM仿真结果显示,各种长度金线的Q值基本超过40. 如图5 (b)所示,匹配结构不变,在把部分Q=20的电感等效换成金线后,输出匹配的插损Loss从0.77 dB降至0.59 dB. 若单功率级的效率为η,则加上输出匹配后功率级的效率为

图 5

图 5 输出匹配3D示意图与仿真结果

Fig.5 3D layout diagram and simulation results of output matching network

考虑到功率级的增益,功率级的效率与PAE基本相等. 如果单功率级的最大PAE为50%,当输出匹配的插损从0.77 dB降至0.59 dB后,功率级整体的PAE将从41.9%提高到43.6%.

本设计的功率级最大输出功率不超过33 dBm,额定供电电压为5 V,考虑到高功率时的效率,功率级最大工作电流不超过1 A. 当金线的直径为0.0254 mm时,金线足以承受超过1 A的电流,并且金线本身的电热效应可以忽略[18]. 当形状不变时,金线的寄生电感主要由水平长度决定[19]. 本研究在利用金线进行匹配设计时,充分考虑了实际打线过程中金线长度不一致的问题. 功率级直流供电上的金线主要作为馈电电感,不参与匹配,因此长度越长对阻抗的影响越小. 在本设计中,当供电金线长度大于1 000 μm时,供电金线对阻抗的影响可以忽略,考虑到金线一端在芯片中央,实际芯片外的金线长度只需要大于600 μm,这在常见封装中容易实现. 对于串联电感部分的金线,两端PAD位置固定,因此水平长度固定,提供的电感感值也就相对稳定. 到地电感部分的金线落点相对不固定,但是此电感要求的感值较大,金线只提供了一半的感值,金线长度变化对输出匹配的影响较小. 如图5 (b)所示,当这3根金线的长度同时变化10%时,输出匹配提供的负载阻抗实部和虚部分别只上下浮动了0.15 Ω和0.09 Ω,当变化达到20%时,阻抗的实部和虚部也只上下浮动了0.32 Ω和0.15 Ω. 相较于减少的匹配插损和芯片面积,金线长度浮动带来的阻抗变化是可以接受的.

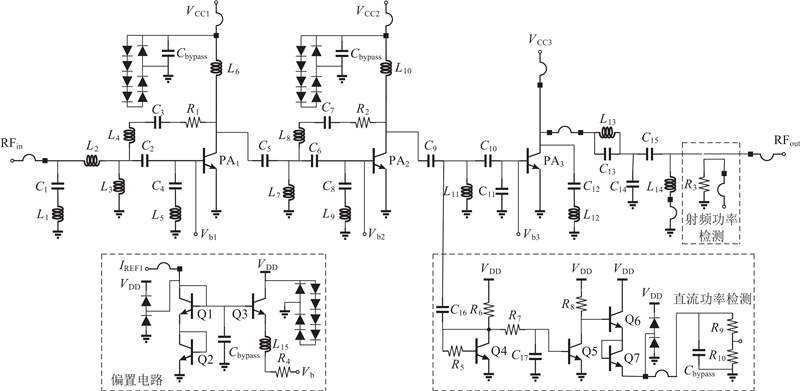

1.3. 整体电路设计

PA原理图如图6所示,为了在实现高线性度时仍有足够的增益,放大器采用三级共源结构,并在前两级引入负反馈以保持稳定. 反馈回路在提高稳定性的同时也能通过调节增益优化前后级失真互补的幅度,还会调节驱动级的输入输出阻抗从而简化匹配结构. 放大器额定工作电压为5 V,各级的晶体管发射极面积之比为1∶4∶12,静态电流分别为26、60、187 mA,以保证功率级能被充分推动并使驱动级形成相反的失真曲线. 放大器使用低寄生电感的晶圆通孔(through-wafer vias,TWVs)提供可靠的接地连接.

图 6

由于前两级输出阻抗较高,金线的寄生电感不足以直接作为扼流电感,为此引入旁路电容形成交流地并在匹配中加入到地电感,使直流供电从到地电感引入. 为了避免前级集电极电压和后级基极偏置电压相互干扰,须引入隔直电容,因此2个级间匹配都采用两阶高通L形匹配网络. 考虑到输入隔直电容和高频的带外滚降,输入匹配采用两阶带通L形匹配网络,并将到地电容等效替换成在3.3 GHz谐振的串联到地LC电路,进一步降低高频的带外增益,同时改善整体的增益平坦度. 使用ADS软件对所有匹配结构进行整体电磁仿真,包括金线和TWVs.电路在二三级的级间匹配处引出一部分信号进行直流功率检测设计,使电路可以给出与输出功率正相关的电压信号,实现更加精确的输出功率控制并简化外围电路设计. 射频信号通过电容C16后使二极管连接的晶体管Q4产生整流效应,使通过电阻R6的电流增大,Q5的基极偏压也随之降低,流过Q5和R8的电流降低,Q6的基极电压升高,带动输出电压升高,通过片外的旁路电容和分压电阻,得到指定动态范围的纹波较小的功率检测电压. 其中电容C16的容值较小,以减少功率检测电路对级间匹配的影响,在检测电压输出前加入二极管连接的晶体管Q7,起到温度补偿和工艺角补偿的作用.

2. 测试结果与分析

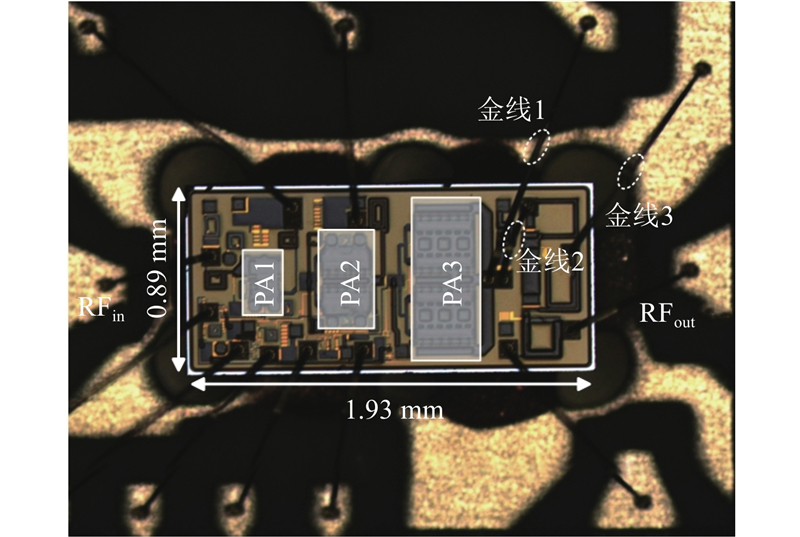

功率放大器基于GaAs HBT工艺进行设计与流片加工,芯片面积为1.93 mm×0.89 mm,芯片通过TWVs直接接地,其余连接由键合金线实现. 如图7所示为打线后的芯片显微镜照片,影响输出匹配的金线1、2、3的长度在可接受的误差范围内.

图 7

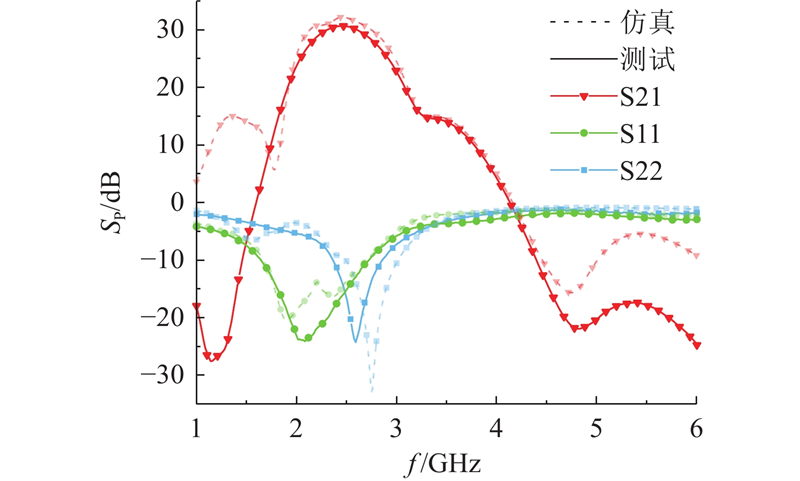

散射参数的仿测结果如图8所示. 当频率范围为2.4~2.5 GHz时,仿真的小信号增益S21=31.9~32.2 dB,输入回波损耗S11 < −13.6 dB,输出回波损耗S22 < −9.1 dB. 矢量网络分析仪测试得到的小信号增益S21=30.6~30.7 dB,输入回波损耗S11 < −15 dB,输出回波损耗S22 < −11.3 dB,与仿真结果比较吻合.

图 8

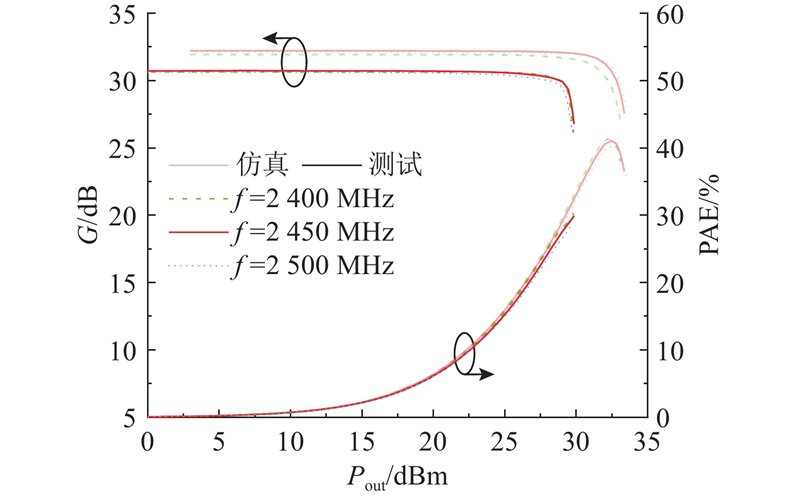

PA在连续波下的大信号仿测结果如图9所示,在中心频率为2.45 GHz处,仿真的P1dB和对应的PAE分别为32 dBm和40.6%,测试的P1dB和对应的PAE分别为29.2 dBm和26.4%,中心频率为2.4、2.5 GHz的曲线与2.45 GHz基本重合. 与仿真结果相比,测试得到的输出功率小于29 dBm时的AM-AM失真和PAE曲线基本相同,但是增益压缩更快,饱和功率小了3 dBm.

图 9

图 9 功率增益和功率附加效率随输出功率变化曲线

Fig.9 Curve of power gain and power added efficiency versus output power

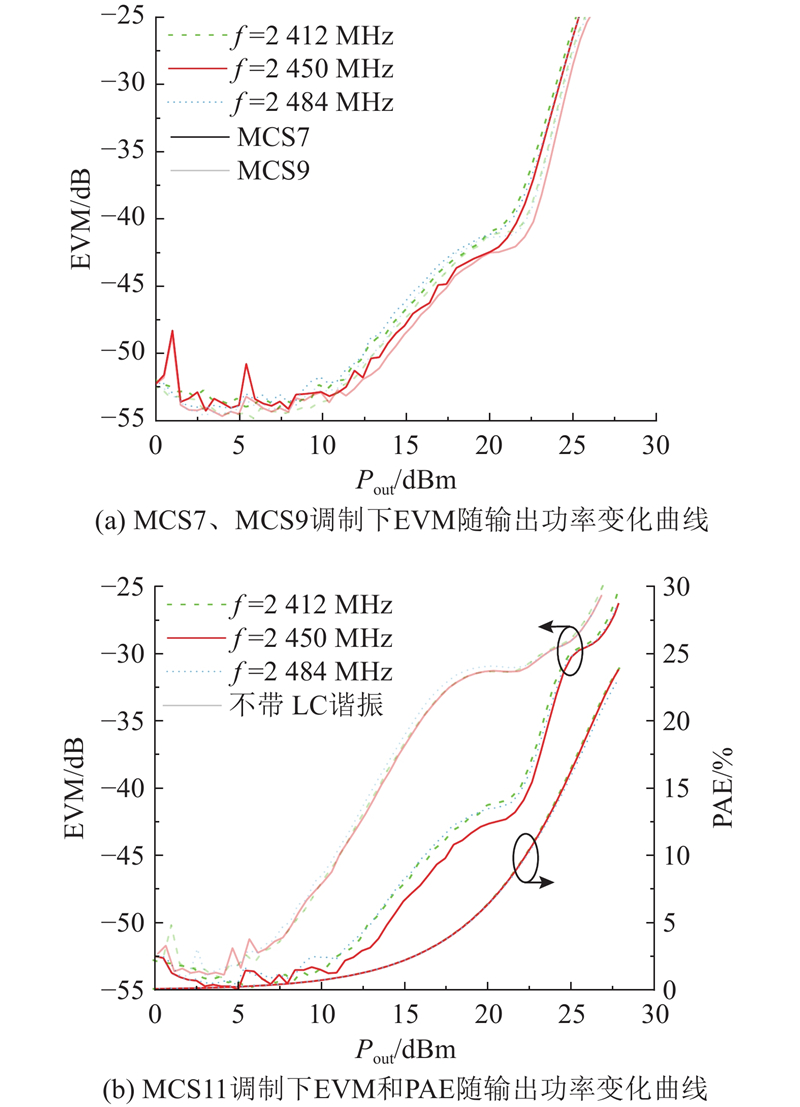

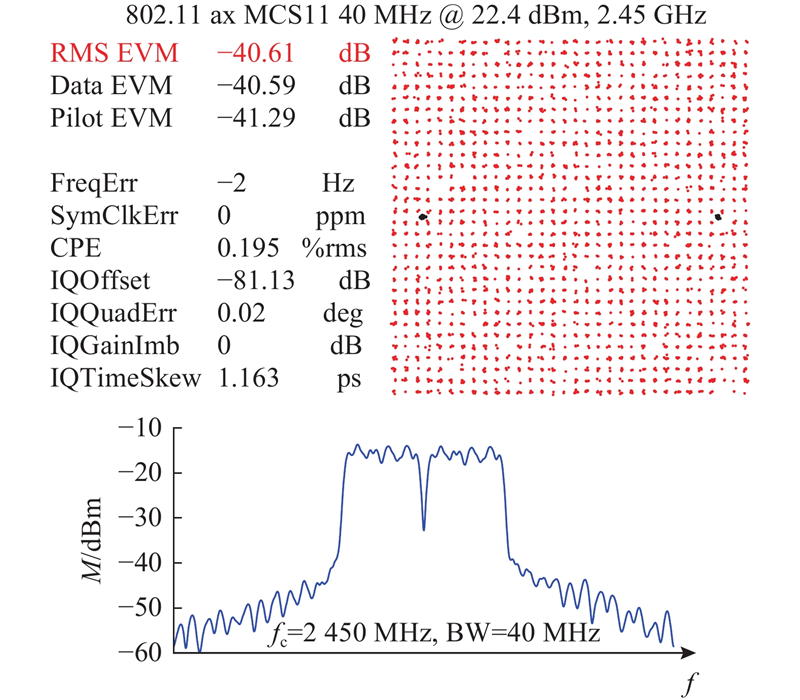

PA在调制信号下的大信号测试结果如图10所示,PA输入均为802.11ax标准的40 MHz测试信号,分别在f=2 412、2 450、2 484 MHz进行测试,当调制策略为MCS7时,满足EVM < −30 dB的最大输出功率为23.9~24.1 dBm;当调制策略为MCS9时,满足EVM < −35 dB的最大输出功率为23.3~23.6 dBm;当调制策略为MCS11时,满足EVM <−40 dB的最大输出功率为21.7~22.4 dBm,对应PAE为9.1%~10.2%. 输入信号为MCS11调制时,PA在2.45 GHz输出22.4 dBm时的星座图和频谱图如图11所示. 输出匹配不带LC谐振进行二次谐波处理的MCS11测试结果见图10(b),该结果是将放大器主体部分与另一不带谐波处理的输出匹配相连测得. 在其他影响因素(如偏置、负载阻抗)相近的条件下,满足EVM < −40 dB的最大输出功率为13.1~13.3 dBm,比带LC谐振的测试结果小超过8 dBm. 只有当EVM要求低于−30 dB时,谐波处理前后的输出功率才比较接近.

图 10

图 11

图 11 MCS11调制下输出功率为22.4 dBm时的星座图和频谱图

Fig.11 Constellation and spectrum diagram at 22.4 dBm output power with MCS11 modulation

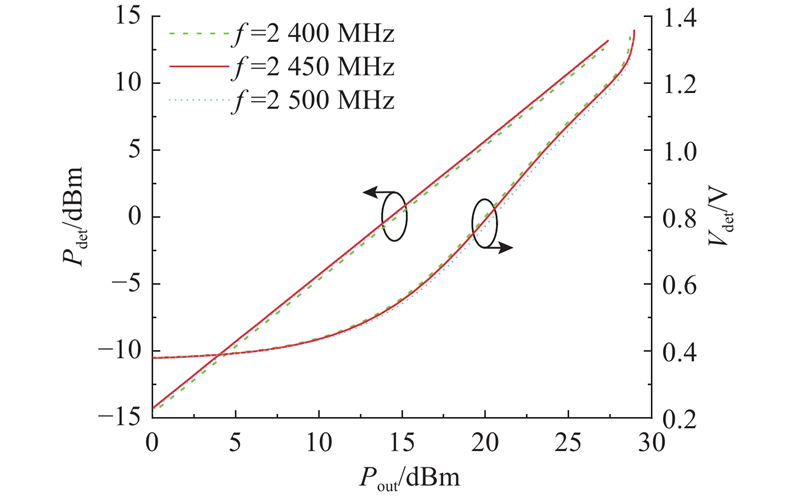

图 12

图 12 射频和直流功率检测随输出功率变化曲线

Fig.12 Curve of RF and DC power detection versus output power

表 1 高线性度功率放大器性能比较

Tab.1

3. 结 语

本研究采用GaAs HBT工艺设计高线性度、高功率放大器,利用有源偏置电路、二次谐波短路和多级失真互补优化线性度,通过键合金线减小输出匹配插损,集成了2种形式的功率检测,采用三级共源结构和负反馈以提供较高的增益并保持稳定. 相较于仅使用有源偏置的电路,所提设计可以在更小的回退功率下满足WI-Fi 6严格的EVM要求. 测试结果表明,在2.4~2.5 GHz频率范围,PA的小信号增益为30.6~30.7 dB,输出1dB压缩功率为29.2 dBm,在802.11ax标准、MCS11调制策略、40 MHz带宽的测试信号下,EVM小于−40 dB时的最大输出功率为21.7~22.4 dBm. 本设计中的PA具有良好的综合性能,可应用于Wi-Fi 6射频前端模块. 在下一步的工作中,计划对PA高功率下的电热效应进行建模,进一步提高PA的饱和功率和最大PAE.

参考文献

A fully integrated GaAs HBT power amplifier with enhanced efficiency for 5-GHz WLAN applications

[J].DOI:10.1587/elex.19.20220157 [本文引用: 2]

A carrier aggregation transmitter front end for 5-GHz WLAN 802.11ax application in 40-nm CMOS

[J].DOI:10.1109/TMTT.2019.2939311 [本文引用: 1]

Highly linear high-power 802.11ac/ax WLAN SiGe HBT power amplifiers with a compact 2nd-harmonic-shorted four-way transformer and a thermally compensating dynamic bias circuit

[J].DOI:10.1109/JSSC.2020.2993720 [本文引用: 2]

A fully integrated 27-dBm dual-band all-digital polar transmitter supporting 160 MHz for Wi-Fi 6 applications

[J].DOI:10.1109/JSSC.2020.3024973 [本文引用: 1]

PCS/W-CDMA dual-band MMIC power amplifier with a newly proposed linearizing bias circuit

[J].

High efficiency linear power amplifier for IEEE 802.11g WLAN applications

[J].DOI:10.1109/LMWC.2006.880702 [本文引用: 1]

用于IEEE 802.11 b/g/n WLAN的高线性度功率放大器

[J].

High linear power amplifier for IEEE 802.11 b/g/n WLAN applications

[J].

Power amplifier PAE and ruggedness optimization by second-harmonic control

[J].DOI:10.1109/JSSC.2003.815918 [本文引用: 1]

A C-band high-efficiency power amplifier MMIC with second-harmonic control in 0.25 μm GaN HEMT technology

[J].

Highly efficient power amplifier based on harmonic-controlled matching network

[J].DOI:10.1109/LMWC.2022.3196669 [本文引用: 1]

A fully integrated transformer-coupled power detector with 5 GHz RF PA for WLAN 802.11ac in 40 nm CMOS

[J].DOI:10.1109/JSSC.2015.2399458 [本文引用: 1]

A 5-GHz WLAN RF CMOS power amplifier with a parallel-cascoded configuration and an active feedback linearizer

[J].DOI:10.1109/TMTT.2017.2691766 [本文引用: 2]

A highly linear two-stage amplifier integrated circuit using InGaP/GaAs HBT

[J].DOI:10.1109/JSSC.2010.2061612 [本文引用: 1]

A 5.15–6.425 GHz stagger-tuning neutralized power amplifier using a continuous-mode harmonically tuned network

[J].DOI:10.1109/LMWC.2022.3168567 [本文引用: 2]

A floating-body transistor-based power amplifier for sub-6-GHz 5G applications in SOI CMOS 130-nm process

[J].

Thermal stability of emitter ballasted HBT’s

[J].DOI:10.1109/16.704359 [本文引用: 1]

The use of base ballasting to prevent the collapse of current gain in AlGaAs/GaAs heterojunction bipolar transistors

[J].

A highly efficient linear multimode multiband class-J power amplifier utilizing GaAs HBT for handset modules

[J].DOI:10.1109/TMTT.2020.3002161 [本文引用: 1]