面对狭窄的ESD设计窗口,要求ESD防护器件的导通电阻尽量低,同时需要一定的回滞,确保将ESD电压钳位在栅氧击穿的5.5 V以下. 传统VBO高速接口的IO管脚多采用普通二极管作为ESD防护器件[5]. 传统二极管的鲁棒性差,电压钳位能力弱. 本文针对VBO接口芯片的IO管脚,设计2种新型的ESD防护器件:栅二极管(Gdiode)与面积效率二极管触发SCR(ASCR). 对这2种器件在SMIC 40 nm及28 nm PS CMOS工艺下进行流片验证.

1. VBO接口电路ESD防护设计特点及失效分析

对业界普遍使用的一款VBO接口芯片进行失效分析,该VBO接口芯片的ESD防护电路如图1所示. 该芯片接口在I/O对VDD、I/O对VSS以及VSS/VDD之间均有ESD防护电路,其中差分高速IO输入端对VDD及VSS均采用两级二极管作为ESD防护,其中D1/D2用作一级防护,D3/D4作为二级防护,中间电容用于隔离直流,R用于防护由CDM引起的overshoot过冲,VDD对VSS之间采用RC触发NMOS防护. 对于纳米集成电路来说,栅氧是最脆弱的,输入信号是直接连接在差分放大器的2个栅上,因此很容易造成MOS管的栅氧击穿. 需要设计精细的ESD防护电路,将ESD电压钳位在5.5 V以下,这样栅氧不会击穿. 虽然二极管存在钳位能力差、鲁棒性低、器件面积大等问题,但是因为器件简单、适合作低压电路ESD防护,仍普遍采用[6-8].

图 1

为了进一步提升该VBO芯片的ESD防护能力,对该芯片进行失效分析,步骤如下.

1)对芯片进行IQC---由3D OM确认失效芯片外观是否异常.

2)测量芯片Ⅳ---利用半导体参数仪对失效pin进行电性测量.

3)Backside polish---利用研磨及化学法将样品封装部分去除,将晶背露出.

4)OBIRCH定位失效点---由OBIRCH机台对失效PIN组合进行热点定位.

如图2所示为该VBO芯片的失效位置分析图. 可以看出,在正向静电PS模式冲击下,电流需要经过D1正偏二极管和电源钳位电路到达VSS(如图1的路径1),或部分电流经过C-R-D3正偏二极管和电源钳位电路到达VSS,如图1的路径2. 失效分析表明:在PS模式下,电路失效主要是由于D1二极管鲁棒性低导致的烧毁,如图2(a)所示,因此需要提高ESD防护器件本身的鲁棒性. 在反向静电NS模式冲击下,电流经过D2正偏二极管, 如图1的路径3. 失效分析表明:在NS模式下,电路失效主要是由于正偏二极管电压钳位能力弱,导致差分放大的MOS管源漏击穿, 如图2(b)所示,需要改善ESD器件的电压钳位能力. 目前的ESD防护无法满足需求,需要设计更低导通电阻、更高钳位能力和更强鲁棒性的ESD防护器件.

图 2

2. 栅二极管的ESD防护设计

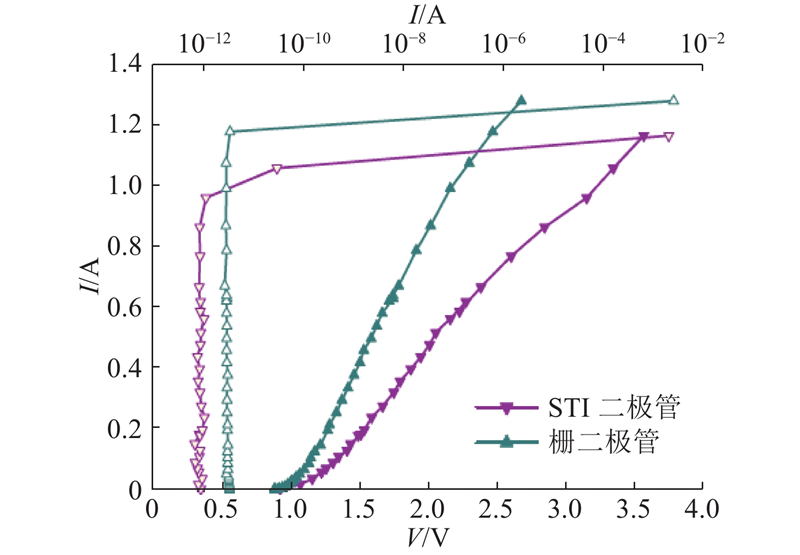

定义器件水平方向尺寸(X轴方向)为器件长度方向,垂直方向(Y轴方向)为器件高度,Y轴方向为器件宽度. 定义鲁棒性为ESD器件的失效电流It2与器件宽度W的比值. 该VBO接口芯片ESD设计窗口为1.2~5.5 V,为了改善VBO芯片的ESD防护电路性能,需要降低二极管的导通电阻,在相同电流下实现更小的钳位电压,增强器件鲁棒性. 针对传统二极管进行改进,提出栅二极管,2种二极管的横截面如图3(a)、(b)所示. 将如图3(a)所示的传统二极管的浅槽隔离(STI)替换成栅,形成栅二极管,如图3(b)所示. 2种二极管的P+/N+水平方向上的长度为1 μm,STI水平方向上的长度为0.5 μm,栅宽水平方向上的长度为0.5 μm. 2种二极管的宽度(Y轴方向)相同(W=60 μm),在SMIC 40 nm CMOS工艺下进行流片,测试结果如图4所示,传统浅槽隔离二极管和栅二极管的导通电阻分别为2.09和1.28 Ω. 可以看出,栅二极管的导通电阻相较于传统二极管大大减小. 传统二极管与栅二极管ESD鲁棒性分别为17.5和19.7 mA/μm(单位宽度下的失效电流),可见在SMIC 40 nm CMOS工艺下,相同尺寸下栅二极管不仅有较小的正向导通电阻,而且有较高的正向导通能力.

图 3

图 4

图 4 传统浅槽隔离二极管与栅二极管TLP曲线

Fig.4 TLP curves of traditional STI diode and gate diode

图 5

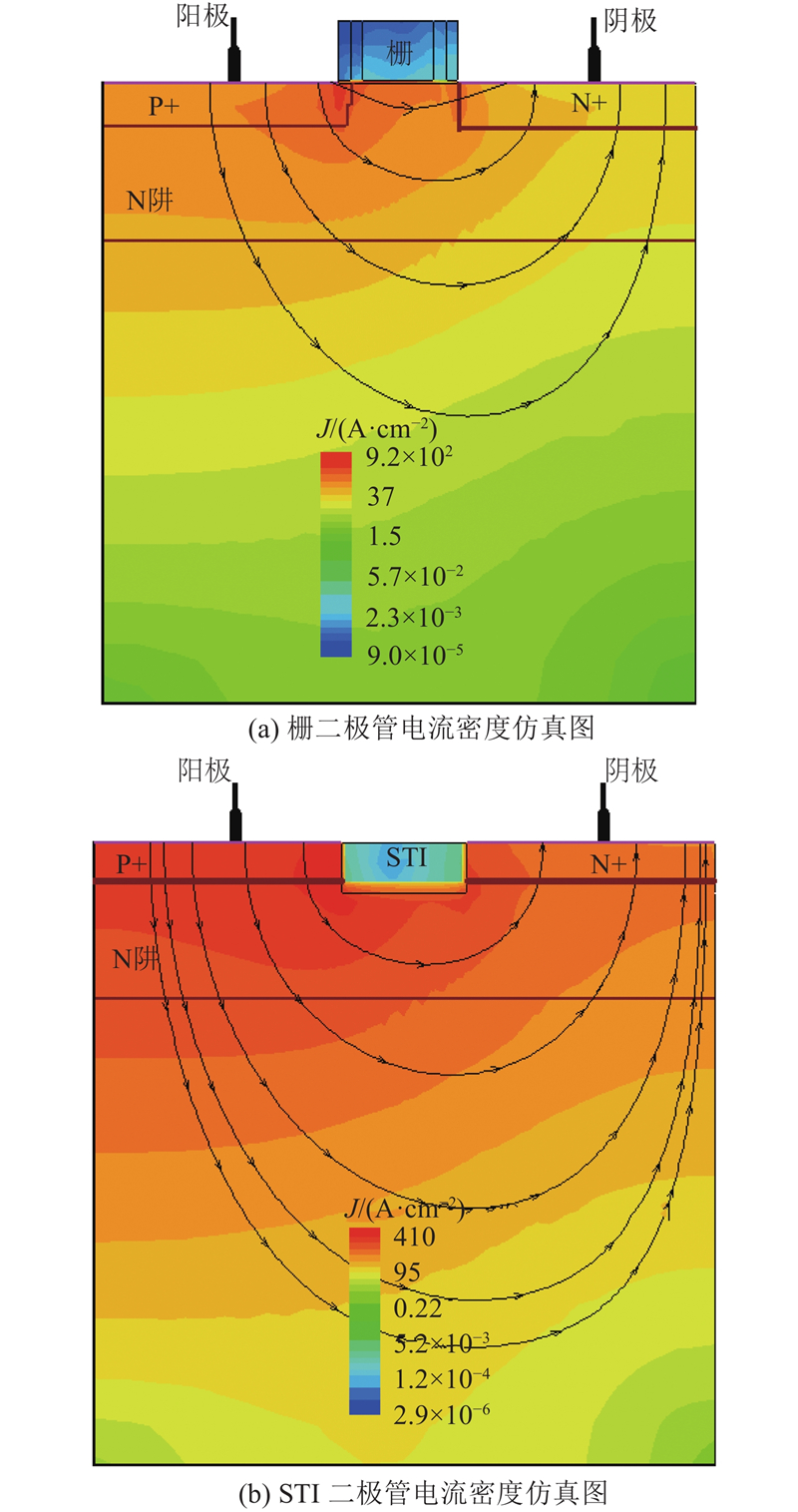

图 5 栅二极管与浅槽隔离二极管电流密度仿真图

Fig.5 Total current density of gate diode and STI diode

为了进一步改善栅二极管的性能,分别将栅二极管的栅接阳极、阴极和浮空,形成3种栅二极管:栅浮空二极管(GFDiode)、栅接阴极二极管(GSDiode)、栅上电二极管(GDDiode). 在SMIC 28 nm PS CMOS工艺下,对3种P+Nwell二极管(3种二极管的宽度相同且W=60 μm)进行流片验证. 测试结果如图6所示,GFDiode、GSDiode、GDDiode三者的导通电阻分别为2.87、3.3、2.46 Ω,三者的鲁棒性十分相似,都约为16 mA/μm.

图 6

图 6 GFDiode和GSDiode以及GDDiode TLP曲线

Fig.6 TLP curves of GFDiode GSDiode and GDDiode

分析图6的TLP测试数据可以发现,在3.3 V的反向直流电压下,GDDiode的漏电流小于GFDiode的漏电流小于GSdiode的漏电流. 这是因为当加反向电压时,GDDiode的栅极下方形成负电场,排斥自由电子,形成耗尽层. 总体的效果是N阱表面的施主型掺杂浓度减小,因此漏电流减小. 由此可知,在相同器件参数下,GDDiode在鲁棒性相同的前提下,正向导通时有最小的导通电阻,反向导通时有最小的漏电流,因此静电防护性能最理想. 由于栅氧层十分脆弱,在栅极加压很容易导致器件损坏,应该在栅极引出的Pad上加入保护电阻. 由于电阻加在Pad下方,不增加额外版图面积.

3. 面积效率二极管触发SCR设计

图 7

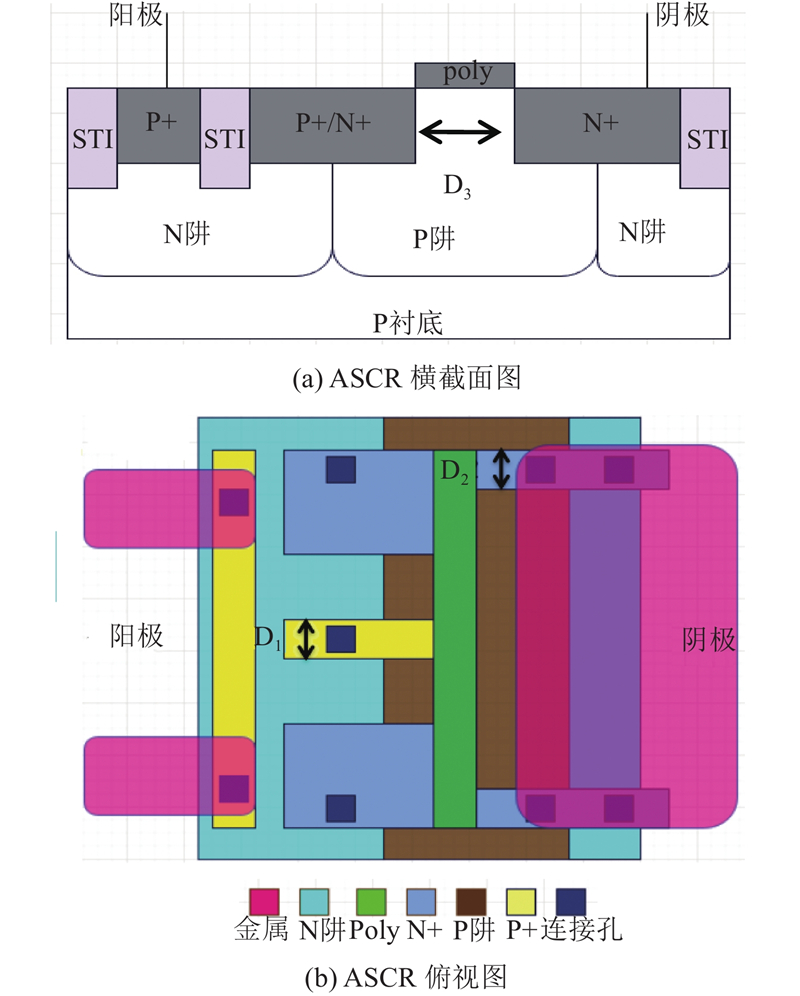

在当今的CMOS工艺下,垂直硅面的纵向器件参数一般都由工艺参数决定,所以留给版图层面的器件设计者只有长度(X轴方向)和宽度(Y轴方向)2个方向的参数可以控制. 在现有的大多数ESD防护器件设计中,一般只是控制器件长度方向上的参数,如掺杂类型、掺杂区的长度等,而宽度方向上的参数都一样. 完整的器件设计信息只需要一个横截面图加一个宽度数据,就能完全给出. 为了充分提高器件的面积利用率,可以考虑对器件宽度方向和长度方向2个维度同时进行参数设计. 基于上述设计方法,提出新型的面积效率二极管触发SCR(ASCR),在符合28 nm Core器件ESD窗口的前提下,显著提高常规DTSCR的面积效率,横截面和俯视图结构如图8(a)、(b)所示.

图 8

利用Sentaurus,对ASCR进行TCAD电流密度仿真,如图9(a)、(b)所示. 在ASCR触发初期,SCR结构未导通,器件整体电流密度小,二极管串结构首先开启,电流从阳极的P+注入区经过N阱流至N+注入区,之后沿着N+注入区上的金属连线流至P+注入区,然后由P+注入区流入P阱,最后从P阱上N+注入区流向阴极,TCAD电流密度仿真曲线如图9(a)所示. 随着电流的逐渐增大,N阱P阱雪崩击穿,电流从阳极P+注入区流入N阱,随后进入P阱,最后从P阱上N+注入区流向阴极,形成PNPN的正、反馈路径,SCR结构开启,器件完全导通,TCAD电流密度仿真曲线如图9(b)所示. 因为有上述的电流路径,可以在不增加面积的前提下充分利用宽度方向上的阱电阻,使得整体触发电压为2个二极管的导通电压与导通电流在宽度方向的阱电阻上产生的压降之和. 要达到某个相同的开启电压,需要的二极管数比常规二极管触发SCR少,因此减小了单个器件面积,提高了面积效率.

图 9

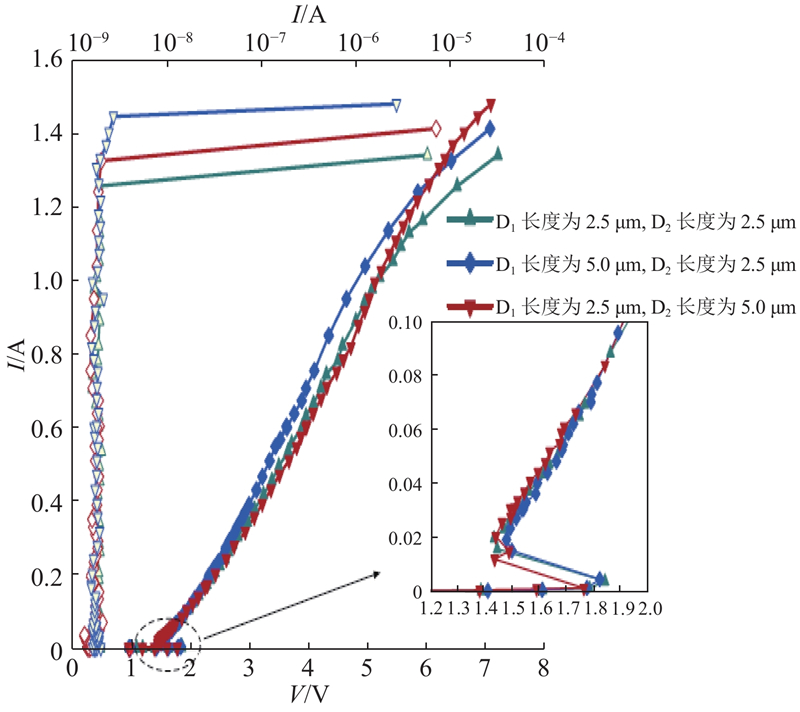

对该器件(W=30 μm,D1长度为5 μm,D2长度为5 μm,D3长度为0.15 μm,P+注入区长度为1 μm,P+/N+注入区长度为2 μm,N+注入区长度为2 μm,STI长度为0.5 μm,栅极长度为0.15 μm)在SMIC 28 nm PS CMOS工艺下进行流片验证,并在Barth 4002下进行10 ns上升沿和100 ns脉宽的TLP测试,得到数据曲线,如图10(a)所示. 如图10(b)所示为该器件在脉宽为5 ns,上升时间为0.2 ns的条件下测得的VF-TLP测试曲线;如图10(c)所示为该器件在VF-TLP脉冲电压为6 V的条件下的电压瞬态曲线. 从图10(a)可以看出,该器件的触发电压达到1.82 V,高于2个二极管串联的触发电压1.4 V,失效电流It2为1.45 A,ESD鲁棒性为48.1 mA/μm,明显优于二极管结构的ESD防护器件. 此外,该器件的维持电压约为1.55 V,回滞很小,很适合用作ESD防护;定义开启时间Ton=(N2−N1)×0.8,其中N2为瞬态曲线上的最大值对应的时间格点数,N1为电压刚开始进入钳位值时对应的时间格点数,Ton=(3.2−1.52)×0.8. 根据图10(c)计算可得,器件的开启时间约为1.344 ns,开启速度快,适合用作高速电路下的ESD防护.

图 10

图 10 ASCR TLP测试曲线以及VF-TLP测试曲线和VF-TLP瞬态电压曲线

Fig.10 TLP curve, VF-TLP curve and VF-TLP transient voltage curve of ASCR

图 11

图 11 不同D1和D2参数下ASCR TLP测试曲线

Fig.11 ASCR TLP test curve under different parameters of D1 and D2

表 1 不同高速接口电路ESD防护方案性能对比

Tab.1

从表1可以看出,ASCR相较于其他器件有着最小的面积和最高的鲁棒性,虽然开启时间稍大,但是满足28 nm CMOS工艺下高速电路对器件开启时间的要求. 1.82 V的低触发电压与48.1 mA/μm的高鲁棒性,满足了VBO接口电路的ESD窗口,节省了版图面积.

4. 结 语

针对VBO接口芯片的ESD防护,提出栅二极管与ASCR 2种结构,在SMIC 28 nm PS与40 nm CMOS工艺下进行流片验证. 栅二极管的ESD鲁棒性为19.7 mA/μm,导通电阻为1.28 Ω,相较于传统二极管,鲁棒性略有提升,导通电阻减小了38%. 栅二极管是最简单的二极管结构,电流路径短,因此栅二极管设计简单,开启速度极快,寄生电容较小,导通电阻小,这是该器件的优点,但是鲁棒性不是很高;由于二极管的触发电压为0.7 V,不满足VBO接口芯片的ESD设计窗口,因此常常需要将栅二极管串联使用,这是栅二极管的缺点. 面积效率二极管触发SCR的ESD鲁棒性为48.1 mA/μm,触发电压为1.82 V,高鲁棒性和满足ESD设计窗口的低触发电压是ASCR的优点. SCR路径的开启需要N阱P阱的雪崩击穿,因此ASCR的开启速度比栅二极管慢;由于该器件利用宽度方向上的阱电阻来增加触发电压,导通电阻较大,这是ASCR的缺点. 结合两者的优缺点,栅二极管适用于对开启速度要求很高、对鲁棒性要求不高的ESD电路防护,ASCR适合用于对鲁棒性要求很高、版图面积小但对开启速度要求不严格的ESD电路防护. 在后续的工作中,将进一步考察栅二极管与ASCR器件电容以及其在Finfet工艺下的ESD特性,满足Finfet工艺下高速电路对ESD防护器件的性能需求.

参考文献

Area-efficient and low-leakage diode string for on-chip ESD protection

[J].DOI:10.1109/TED.2015.2504493 [本文引用: 1]

Optimization on layout style of ESD protection diode for radio-frequency front-end and high-speed I/O interface circuits

[J].DOI:10.1109/TDMR.2010.2043433 [本文引用: 1]

A low-voltage triggering SCR for on-chip ESD protection at output and input pads

[J].DOI:10.1109/55.75685 [本文引用: 1]

Self-triggered stacked silicon-controlled rectifier structure (STSSCR) for on-chip electrostatic discharge (ESD) protection

[J].

Improved low-voltage-triggered SCR structure for RF-ESD protection

[J].DOI:10.1109/LED.2013.2265411 [本文引用: 3]

A systematic study of ESD protection co-design with high-speed and high-frequency ICs in 28 nm CMOS

[J].DOI:10.1109/TCSI.2016.2581839 [本文引用: 2]