2. 嘉兴学院 电子信息工程系, 浙江 嘉兴 314001;

3. 宁波大学 信息科学与工程学院, 浙江 宁波 315211

2. Department of Electronic Information Engineering, Jiaxing University, Jiaxing 314001, Zhejiang Province, China;

3. Faculty of Information Science and Engineering, Ningbo University, Ningbo 315211, Zhejiang Province, China

半导体集成电路技术不断突破工艺瓶颈向高集成度、高速度、低功耗方向发展.但随着特征尺寸的不断缩减, 作为主流CMOS技术中的MOSFET器件尺寸将达到其物理极限, 且量子效应的显现可能导致器件失效.因此, 科研工作者一方面通过创新半导体制造工艺使CMOS技术得以延续;另一方面也提出了各种可能取代MOSFET的新型电子器件, 诸如单电子晶体管(single-electron transistor, SET)、共振隧穿二极管(resonant tunneling diode, RTD)、量子细胞自动机(quantum-dot cellular automata, QCA)等[1-3].其中, SET工作时仅需一个或几个电子, 具有极低的功耗.而且该器件目前与CMOS工艺结合最为紧密, 被认为是制造新一代超低功耗、超高密度集成电路最具竞争力的新型纳米电子器件之一.因此, SET在数字逻辑电路方面的应用受到了广泛关注[1, 4-6].

阈值逻辑最初作为人工神经网络的基本单元——神经元而提出.阈值逻辑门因具有独特的优点而被广泛应用于神经网络、图形处理等领域.在逻辑函数分类和逻辑综合方面也有其独特的应用:一个阈值逻辑门可实现任意的线性可分离逻辑函数;用多个阈值逻辑门则可实现任意逻辑函数.但要实现不同的阈值函数(所有三变量逻辑函数中共有104个阈值函数)需设计大量不同结构的阈值逻辑门, 这势必限制了阈值逻辑门在逻辑综合中的推广应用.相对而言, 通用阈值逻辑门(universal threshold logic gate, UTLG)的功能则更为强大.尤其是三变量UTLG适合作为大规模集成电路的单元电路, 而且用一个三变量UTLG以及少量的传统逻辑门可以实现任意三变量逻辑函数[7-10].文献[8-10]分别提出了阈值逻辑门硬件电路的CMOS、RTD、QCA实现方案.本文提出基于SET的三变量UTLG实现方案及其应用, 为完善SET单元电路库并拓展其应用奠定基础.

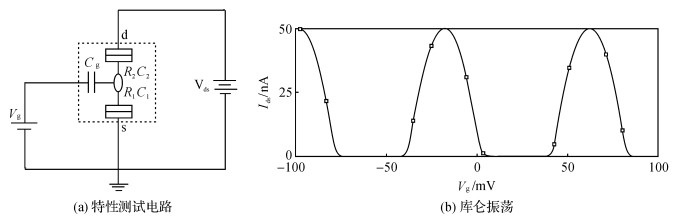

1 基础知识 1.1 SET的特性及互补型SET逻辑门典型的SET是由1个量子点(库仑岛)、2个串联的隧道结构组成的三端器件,图 1(a)虚线框内为SET的电路符号(椭圆代表库仑岛,带横线的矩形框表示隧道结).其中参数Cg为栅极g的耦合电容;与源极s相连的隧道结的电特性用隧穿电阻R1和隧穿电容C1表征;类似地,R2、C2分别代表与漏极d相连的隧道结的隧穿电阻和隧穿电容.值得注意的是:尽管管脚名称与MOS管相同,但其工作机理却截然不同,SET是基于库仑阻塞、单电子隧穿等量子现象的.当漏源极外加合适的电压Vds时, 施加在栅极上的电压Vg通过耦合电容Cg向量子点感生电荷并操纵单个电子经由器件内的隧道结—量子点—隧道结输运, 从而形成漏源电流Ids.利用图 1(a)可测试SET端口的电特性.图 1(b)所示的库仑振荡现象是SET特有的性质之一,即固定偏压Vds、SET的Ids将随偏压Vg的变化周期性振荡.利用SET的通断特性可设计构造各种功能的SET逻辑电路, 如全加器、触发器等[1, 5-6].相移特性是SET的另一重要特性, 即库仑振荡特性曲线随背景电荷Q0的变化沿横轴Vg方向发生横向移动.当Q0>0时曲线左移, Q0 < 0时, 则曲线右移.若Q0取值恰当, 可使2个SET的库仑振荡曲线相位差180°, 从而使它们工作在互补的通断状态.比照CMOS相关概念, 相应的SET分别称为NSET和PSET.

|

图 1 SET特性测试电路及库仑振荡 Fig. 1 SET characteristic test circuit and Coulomb blockade oscillations |

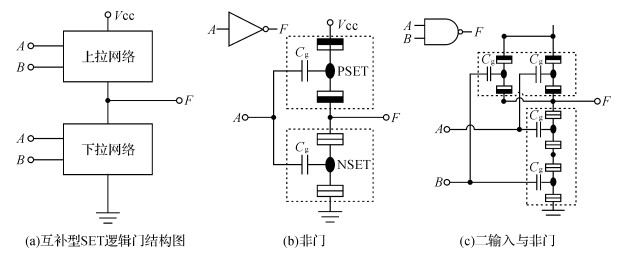

利用NSET和PSET, 基于SET逻辑电路设计可方便地沿用CMOS逻辑电路的设计思想.类似地, 互补型SET逻辑门可由2个网络组成, 即由PSET构成的上拉网络和由NSET构成的下拉网络(如图 2(a)所示).在构造SET基本逻辑门(如非门、与非门、或非门等)时, 对下拉网络中的NSET而言是“串与并或”, 而对于上拉网络中的PSET则为“并与串或”.图 2(b)为互补型SET非门电路;图 2(c)为互补型SET二输入与非门电路, 其上拉网络中是2个并联PSET,而下拉网络中是2个串联NSET.图 2中SET符号与图 1中的区别在于代表库仑岛的椭圆中填充了黑色(代表Q0不为0), 而NSET和PSET的区别在于PSET矩形框的一半被填充了黑色.文中对SET仿真时采用Lientschnig的SET-SPICE模型, PSET和NSET的参数设置除背景电荷外分别为Q0=+0.15 e/-0.15 e外, 其余参数取值相同:C1=C2=1 aF, Cg=2 aF, C0=0, R1=R2=105Ω, 仿真温度T=4.2 K[11].

|

图 2 互补型SET逻辑门及SET基本逻辑门结构图 Fig. 2 Representation of complementary SET logic gate and basic SET gates |

传统的逻辑电路设计均基于与或非逻辑,对于线性可分离的逻辑函数而言, 也可表示为阈值函数.n变量阈值逻辑函数f(x1~xn) =〈w1·x1+w2·x2+…+wn·xn〉t的定义为

| $ \left\{ \begin{array}{l} ({w_1}\cdot{x_1} + \cdots + {w_n}\cdot{x_n}) \ge t, f({x_1} \sim {x_n}) = 1, \\ ({w_1}\cdot{x_1} + \cdots + {w_n}\cdot{x_n}) < t, f({x_1} \sim {x_n}) = 0, \end{array} \right.{\rm{ }} $ | (1) |

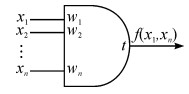

式(1) 中wi、t分别称为权、阈值, 输入变量xi∈{0, 1}.须注意的是,式(1) 中的·和+分别表示算术运算的乘法及求和, 而不是逻辑代数中的或运算及与运算.实现式(1) 运算的逻辑门称为阈值逻辑门(见图 3), 在神经网络中又称为感知器神经元.

|

图 3 阈值逻辑门 Fig. 3 Symbol of threshold logic gate |

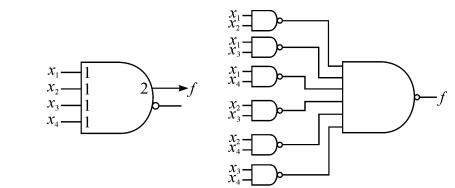

适合做集成电路门阵列的UTLG功能非常强大,在各种UTLG中具有4个输入端, 权wi=1(i∈{1, 2, 3, 4})和阈值t=2的带反相输出的UTLG更具应用价值[8-10].若输入端的取值为{x1, x2, x3, 0, 1}, 改变取值和输出端的接法,可实现全部256个三变量逻辑函数, 故常称为三变量UTLG.

2 通用阈值逻辑门的SET电路实现及其综合 2.1 三变量SET通用阈值逻辑门的电路实现根据阈值逻辑函数的定义,直接利用SET加法器及乘法器电路实现通用阈值逻辑门的电路结构十分复杂.由式(1) 及三变量UTLG的定义可列出其真值表, 化简得其函数表达式为

| $ \begin{array}{*{20}{l}} {f = {x_1} \cdot {x_2} + \underline {{x_1} \cdot {x_3} + {x_1} \cdot {x_4} + {x_2} \cdot {x_3} + {x_2} \cdot {x_4} + } }\\ {\;\;\;\;\;\;\;\underline {{x_3} \cdot {x_4} = \overline {{x_1} \cdot {x_2}} } \cdot \overline {{x_1} \cdot {x_3}} \cdot \overline {{x_1} \cdot {x_4}} \cdot \overline {{x_2} \cdot {x_3}} \cdot }\\ {\;\;\;\;\;\;\;\overline {{x_2} \cdot {x_4}} \cdot \overline {{x_3} \cdot {x_4}} ,} \end{array} $ | (2) |

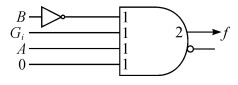

式(2) 中的+和·是传统逻辑代数中的或运算及与运算.图 4(a)给出了带反相输出的三变量UTLG的符号, 图 4(b)是实现该UTLG的门级逻辑设计, 即可由6个二输入SET与非门、1个六输入SET与非门构成(f的反相输出可再经一个非门得到).限于篇幅, 文中不再给出具体的SET电路.

|

图 4 带反相输出的三变量UTLG符号及逻辑设计 Fig. 4 Symbol and its logic design of three-variableUTLG with a complementary output |

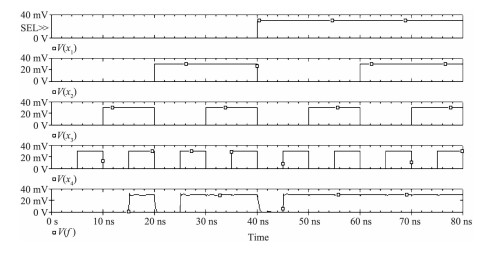

利用Pspice对三变量UTLG的SET电路进行仿真,可得如图 5所示的输入输出波形(信号的高低电平分别为30和0 mV), 反映所设计的SET UTLG逻辑功能正确.

|

图 5 基于SET的UTLG的仿真波形 Fig. 5 Simulation waveforms of UTLG based on SET |

利用UTLG进行逻辑综合有多种方法:如直接按定义的综合、谱技术综合等.但对于三变量逻辑函数, 最简便且便于用计算机编程实现的是查表设计法[7].由文献[7], 用SET的UTLG实现任意三变量逻辑函数的步骤如下:

(1) 由给定的逻辑函数写出对应的8进制代码, 查文献[7]之P分类表得到其P分类代码.

(2) 按P分类代码中的数字查文献[7]之P分类代表函数接线表,得对应的接线方案.

(3) 按P分类代码中的英文字母查文献[7]之接线顺序表, 确定最终输入、输出端接法.

设计实例证明了此综合方法的有效性.限于篇幅, 仅举一例说明.

例1 试用所设计的SET UTLG实现全比较器

由全比较器表达式可知,其最小项系数为011010100, 对应8进制代码为324.查文献[7]之P分类表得其分类代码为C216.根据P分类代码的数字216查文献[7]之P分类代码函数接线表,得接线方案为x1x2x30, 即UTLG的4个输入端应接入GiAB0(Gi表示Gi需经一个非门再接入UTLG的输入端).最后,查文献[7]之接线顺序表, 由分类代码C216的英文字母C可知,其接线顺序应从x1x2x3改为x3x1x2, 即GiAB0改为BGiA0.据此可得图 6所示的全比较器逻辑结构:由1个SET的UTLG门以及1个非门构成.

|

图 6 基于UTLG的全比较器逻辑设计 Fig. 6 Logic structure of full comparator based on UTLG |

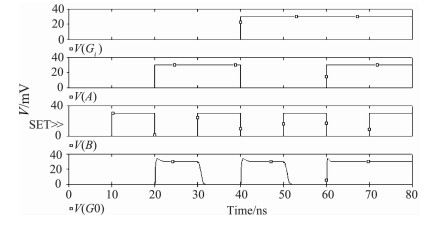

用Pspice对图 6相应的SET电路进行模拟, 所得波形如图 7所示.仿真结果反映了所设计的全比较器逻辑功能完全正确.

|

图 7 基于SET的UTLG全比较器电路仿真波形 Fig. 7 Simulation waveforms of SET based UTLGfull comparator |

SET作为一种新型量子器件,将来可能取代MOSFET.基于SET独特的优点以及具有类似互补MOSFET的NSET和PSET结构, 沿用CMOS逻辑电路的设计思想, 提出用互补型SET逻辑门实现双输出UTLG.该逻辑门功能强大, 利用一个UTLG及少量的门电路就可实现全部256个三变量逻辑函数.通过实例说明了利用查表设计法进行UTLG综合的过程.用Pspice对所设计SET的UTLG以及基于该UTLG的全比较器电路进行模拟仿真, 验证了该设计的正确性.如前所述, UTLG亦可作为感知器神经元, 但其在神经网络等领域中的应用尚待进一步研究.

| [1] | LIKHAREV K K. Single-electron devices and their application[J]. Proceedings of the IEEE, 1999, 87(4): 606–632. DOI:10.1109/5.752518 |

| [2] | CHOI S, JEONG Y, LEE J, et al. A novel high-speed multiplexing IC based on resonant tunneling diodes[J]. IEEE Transactions on Nanotechnology, 2009, 8(4): 482–486. DOI:10.1109/TNANO.2009.2013462 |

| [3] | LENT C S, TOUGAW P D, BERNSTEIN G H, et al. Quantum cellular automata[J]. Nanotechnology, 1993, 4(1): 49–57. DOI:10.1088/0957-4484/4/1/004 |

| [4] | MAHAPATRA S, VAISH V, WASSHUBER C, et al. Analytical modeling of single electron transistor for hybrid CMOS-SET analog IC design[J]. IEEE Transactions on Electron Devices, 2004, 51(11): 1772–1782. DOI:10.1109/TED.2004.837369 |

| [5] |

孙铁署, 蔡理. 一种基于互补型单电子晶体管的全加器电路设计[J].

电子器件, 2005, 28(2): 365–369.

SUN T S, CAI L. A full adder realization with complementary single-electrontransistors[J]. Chinese Journal of Electron Devices, 2005, 28(2): 365–369. |

| [6] |

章专, 魏齐良, 申屠粟民. 基于R-SET结构的逻辑门电路和触发器设计[J].

浙江大学学报:理学版, 2013, 40(3): 272–275.

ZHANG Z, WEI Q L, SHENTU S M. Design of logic gate and flip-flop based on resistance single-electron transistor structure[J]. Journal of Zhejiang University:Science Edition, 2013, 40(3): 272–275. |

| [7] |

肖林荣, 陈冠军, 历晓华, 等. 基于三变量双输出通用阈值逻辑门的逻辑函数查表综合[J].

科技通报, 2005, 21(6): 746–751.

XIAO L R, CHEN G J, LI X H, et al. Tabular design based on three-variable universal-threshold-logic gates with a complementary output[J]. Bulletin of Science and Technology, 2005, 21(6): 746–751. |

| [8] |

胡昌兴, 陈楷雄, 王大能. 基于电流型CMOS电路的阈值逻辑门[J].

杭州大学学报:自然科学版, 1997, 24(2): 133–137.

HU C X, CHEN X X, WANG D N. Threshold logic gates based on current-mode CMOS circuits[J]. Journal of Hangzhou University:Natural Science Edition, 1997, 24(2): 133–137. |

| [9] | YI W, SHEN J Z. Novel universal threshold logic gate based on RTD and its application[J]. Microelectronics Journal, 2011, 42(6): 851–854. DOI:10.1016/j.mejo.2011.04.005 |

| [10] |

肖林荣, 陈偕雄, 应时彦. 基于量子细胞自动机的三变量通用阈值逻辑门电路实现[J].

浙江大学学报:理学版, 2010, 37(5): 546–550.

XIAO L R, CHEN X X, YING S Y. Implementation of three-variable universal-threshold-logic gates using quantum-dot cellular automata[J]. Journal of Zhejiang University:Science Edition, 2010, 37(5): 546–550. |

| [11] |

许翔, 应时彦, 肖林荣. 基于PSpice的单电子器件模型创建及其应用[J].

半导体技术, 2015, 40(4): 284–288.

XU X, YING S Y, XIAO L R. Creation and application of single electron transistor model based on PSpice[J]. Semiconductor Technology, 2015, 40(4): 284–288. |