2. 杭州电子科技大学 教育部射频电路与系统重点实验室,浙江 杭州 310018;

3. 中国电子科技集团公司第41研究所,山东 青岛 255666

2. Key Laboratory of RF Circuits and Systems, Ministry of Education, Hangzhou Dianzi University, Hangzhou 310018, China;

3. The 41st Institute of China Electronics Technology Group Corporation, Qingdao 266555, China

毫米波频段具有丰富且纯净的频谱信息,在100 GHz以上,未使用频段依然占了很大比例,这些频段可以提供相对大的带宽;此外,毫米波具有波长短、穿透能力强和非离子化等特点,为高速、海量数据传输通信系统、非侵入式医疗电子、毫米波成像安检等设备的开发奠定了基础;随着低成本CMOS工艺的不断发展,CMOS晶体管的截止频率不断提高,基于CMOS工艺的毫米波电路成为目前研究领域内的热点[1-5]. 然而,由于CMOS工艺中的MOSFET具有本征增益较低、衬底损耗大和工艺设计要求严苛等特点,设计毫米波频段的电路依然存在一定的挑战和难度.

压控振荡器(voltage control oscillator,VCO)作为毫米波前端的核心电路模块之一,实现了直流信号到交流信号的转化. 基于65 nm CMOS工艺,Zhang等[6]提出了一种采用交叉耦合单元的LC-VCO,通过将基波信号四倍频的方式产生85~127 GHz的输出信号,采用开关电感和开关电容相结合的方式实现频率调谐,频率调谐范围为 42 GHz,输出功率为–15 ~ –23 dBm,该电路的工作频率偏频10 MHz时对应的相位噪声为–108 ~ –102 dBc/Hz. 基于130 nm CMOS工艺,Holisaz等[7]设计了一款LC-VCO,该电路采用源回退负阻单元维持电路稳定振荡,并将基波信号二倍频后输出112.8 ~ 115.2 GHz的信号,电路采用变容管调谐,实现了2.4 GHz的频率调谐范围,对应基波信号偏频10 MHz的最小相位噪声为–113.6 dBc/Hz. 基于65 nm CMOS工艺,Shang等[8]将4个LC-VCO的振荡信号二倍频后,通过零相移耦合器同相相加,实现了输出信号频率范围为127~140 GHz的信号源,当电路输出频率为132 GHz时,偏频25 MHz时对应的相位噪声为–104.9 dBc/Hz. Huang等[9]采用交叉耦合结构产生基波信号并输出其三倍频信号,提出了一个工作在129~159 GHz的LC-VCO,电路采用变容管调谐,频率调谐范围为30 GHz,最大输出功率为–8 dBm,该VCO的基波信号在偏频1 MHz时的平均相位噪声是 –99.6 dBc/Hz. 基于65 nm低功耗CMOS工艺,Volkaerts等[10]提出了一种工作频率为113.4~122.6 GHz的基波VCO,该电路通过交叉耦合电路实现负阻,采用变容管实现频率调谐,频率调谐范围为9.2 GHz,当电路工作频率为118.3 GHz时,偏频1 MHz时对应的相位噪声为–83.9 dBc/Hz. 从采用倍频方式实现的D波段VCO[6-9]和基波VCO[10]的对比结果来看,采用倍频方式实现的VCO具有较宽的调谐范围,且可以产生接近或者大于工艺最大振荡频率的信号. 然而,基波VCO在相位噪声方面优于通过倍频方式实现的VCO,更加适用于高性能通信系统.

电路工作频率达到D波段后,寄生电容和栅极电阻致使MOS管栅跨导降低,影响电路起振. 本研究电路使用的NMOS管的截止频率为176 GHz,栅跨导相应降低,使得设计工作在D波段的基波VCO具有很大的难度与挑战. 同时工作在D波段的无源器件,如电感、电容等器件的品质因子降低,导致VCO的相位噪声降低. 变容管的品质因子降低,不仅会影响整个VCO电路的调谐范围、相位噪声,还会影响VCO电路的输出功率[11].

本文设计一款基波VCO,有别于上述的VCO,该电路将负阻单元的寄生电容(即交叉耦合对管及其尾电流源管的寄生电容)作为LC谐振网络的电容,并通过调节尾电流管的偏置电压改变MOS管的寄生电容,进而实现频率调谐,从而省略VCO中可变电容的使用,改善VCO的相位噪声,同时降低交叉耦合单元对负阻的要求,使电路易于起振并且维持振荡. 通过这种方式增加了基波VCO电路工作频率接近工艺截止频率的设计成功率及实用性. 文中提出的电路采用65 nm CMOS工艺进行加工,并通过测试验证电路方案的可行性,该电路适用于毫米波通信、成像及检测等应用场合. 本文提出的电路芯片面积为405×440 μm2. 同时,提出电路的拓扑结构,并对无源器件的设计、电路设计进行分析,给出振荡器电路的信号频率、输出功率、调谐范围的测试结果和相位噪声的测试结果.

1 电路拓扑结构版图的寄生参数对硅基毫米波集成电路的影响显著增加,在电路设计中需要充分考虑版图连线和GSG焊盘的寄生效应. 在设计VCO时,将电感、变压器按模块分析设计,并在输出Buffer匹配时,将GSG焊盘与变压器、传输线协同设计实现匹配,以避免因输出匹配的失配而导致VCO输出功率低的问题.

本文提出的VCO拓扑结构如图1所示. La和Lb为连接点标识,表示差分电感、VCO负阻单元和输出Buffer之间相互连接. 该电路的负阻单元由交叉耦合对管M1、M2和尾电流源管M3共同构成,维持电路的稳定振荡,并通过控制尾电流源管M3的栅极偏置电压Vq实现振荡器电路输出频率的调谐. 与此同时,负阻单元的寄生电容Ctank与用户自定义设计的差分电感共同构成LC谐振槽. VCO的输出Buffer采用差分Cascode结构,以减小负载效应对VCO的影响,保证电路正常工作. 采用片上变压器 (Balun)、传输线 (TL)、GSG焊盘共同实现电路Buffer到50 Ω的阻抗变换.

|

图 1 压控振荡器(VCO)拓扑结构图 Fig. 1 Topology of voltage control oscillator(VCO) |

硅基毫米波频段无源元件的趋肤效应、邻近效应凸显,衬底损耗增加,使得电路设计中无源元件与有源元件的协同设计变得尤为重要.

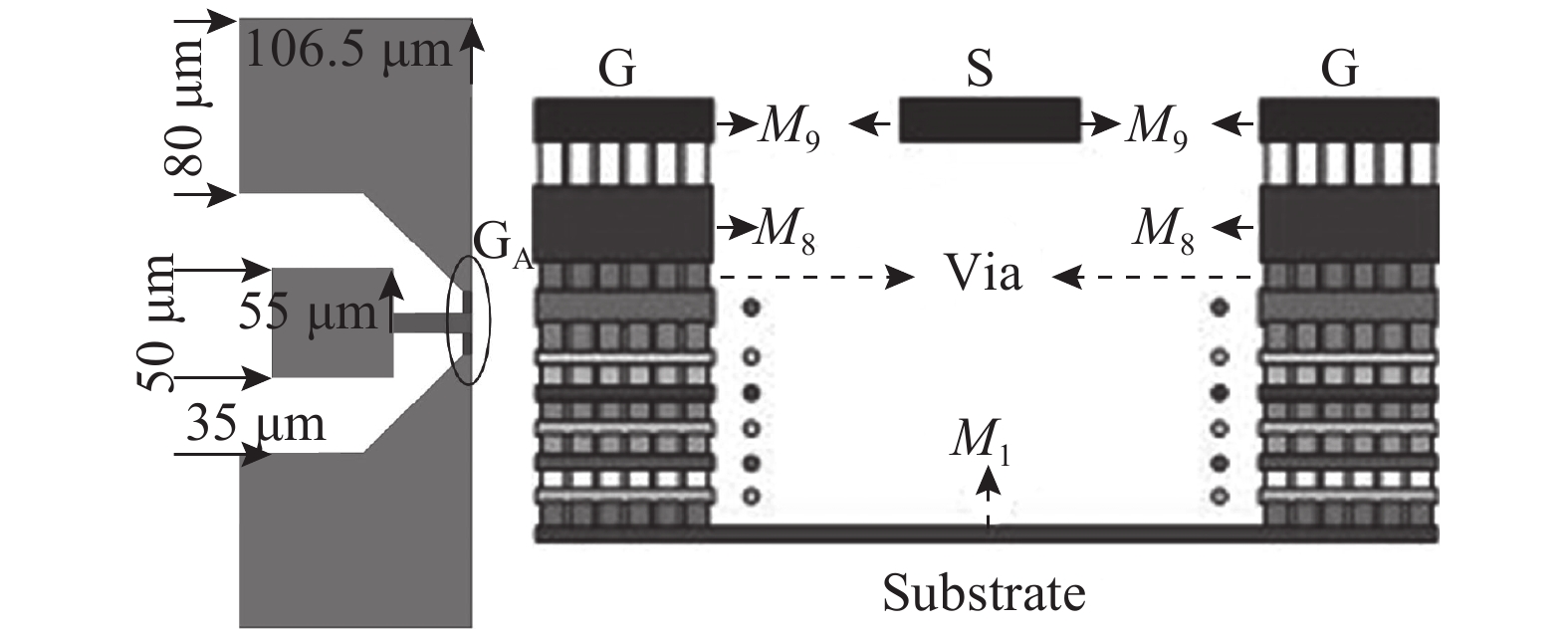

2.1 GSG测试PAD的设计与分析GSG焊盘上的寄生电感、信号焊盘与地焊盘之间的(边沿)电容会影响毫米波电路的匹配[12],导致所设计的电路匹配偏离设计的目标. 因此,本文设计的GSG焊盘,从以下3方面考虑及实现:1)减小信号焊盘与金属地之间的垂直电容和信号焊盘与地焊盘之间的边缘电容;2)在满足工艺规则要求前提下,减小地焊盘上的电阻和电感;3)减小信号在所设计GSG焊盘上的传输损耗.

GSG测试焊盘俯视图和截面图如图2所示. GA表示2个地焊盘之间的间距,G表示地焊盘,S表示信号焊盘,M1、M8、M9分别表示电路加工工艺提供的第一层、第八层、第九层金属,Via表示金属之间的过孔,Substrate表示工艺衬底. 地焊盘采用“格子”的方式布线,满足了工艺规则对金属布线的要求,同时减小了地焊盘上引入的寄生电阻和电感. 以减小信号焊盘与地焊盘之间的边缘电容为目标,所设计的信号焊盘的尺寸为50×55 μm2,小于地焊盘的尺寸(80×106.5 μm2). 同时,信号焊盘的金属下方没有使用金属地,减小了信号焊盘与金属地之间的电容. GSG焊盘中的2个地焊盘在图2标注GA处,采用工艺提供的最低层金属M1相连,实现了GSG地焊盘同电位. 此外,通过优化图2中GA标注处信号线与地焊盘之间的间距,可减少所设计GSG焊盘的信号传输损耗.

|

图 2 GSG焊盘俯视、截面及尺寸标注示意图 Fig. 2 Top view and cross-section view of Ground-Signal-Groud(GSG) PAD and its dimension |

通过全电磁场仿真来评估GSG焊盘的传输性能,考虑电路在片测试时,探针通常会压在GSG焊盘中心位置,因此在仿真时,仿真端子加在以信号焊盘中心为参考点的GSG焊盘的各个焊盘中心,同时采用共面波导端口模式,以保证GSG焊盘仿真与测试的一致性. GSG焊盘电磁仿真示意图及仿真后的S参数SP随频率f的变化如图3所示. 其中P1和P2表示加载在GSG焊盘上的仿真端子,S11、S22表示端口反射参数,S21表示正向传输参数,S12表示反向传输参数. 由图中S参数曲线分析得知,该GSG焊盘在110~170 GHz范围内的传输损耗小于1.8 dB,输入/输出端口的反射系数小于–18 dB.

|

图 3 GSG焊盘仿真端口加载位置示意图及S参数 Fig. 3 Located port position used in simulation for GSG PAD and S-parameter model of transformer |

根据Leeson公式[13],如式(1)所示,分析得出VCO的相位噪声与电路中各元件的Q值密切相关. 电路中的LC谐振网络的品质因子会影响VCO的相位噪声.

| $\begin{split} L&\left( {\Delta \omega } \right) =\\ &10 \cdot \log \;\left\{ {\displaystyle\frac{{2Fkt}}{{{P_{\rm{sig}}}}}} \cdot \left[ {1 + {{\left( {\displaystyle\frac{{{\omega _0}}}{{2Q\Delta \omega }}} \right)}^2}} \right] \cdot {\frac{{\Delta {\omega _{1_{{\large/}}{f^3}}}}}{{|\Delta \omega |}}} \right\}\,.\end{split}$ | (1) |

式中:△ω为偏离振荡频率的偏移量;△ω1/f 3表示(△ω)–3区和(△ω)–2区的分界点,等于振荡电路中有源器件的1/f的角频率[13];F为负阻电路在(△ω)–2区对相位噪声的贡献,是一个实验参数;k为玻尔兹曼常数;t为环境温度;ω0为振荡频率;Psig为输出信号在ω0处的功率;Q为LC谐振回路的品质因子.

鉴于文中VCO的LC谐振网络中的电容采用了负阻单元的寄生电容,高Q值电感的设计显得尤为重要. 片上电感的损耗是影响电感Q值的主要因素,而损耗机制包括金属损耗和衬底损耗. 文中设计电感时,采用差分端口仿真,主要以减少损耗、提高Q值为优化目标. 采用导纳(Y)参量计算电感的感值,品质因子及电阻:

| $ {L_{\rm s}} = \displaystyle\frac{{{\mathop{\rm Im}\nolimits} \;({Y^{ - 1}})}}{\omega },\;\;{R_{\rm s}} = {\mathop{\rm Re}\nolimits} \;({Y^{ - 1}}),\;\;{Q_{\rm s}} = \displaystyle\frac{{{\mathop{\rm Im}\nolimits} \;({Y^{ - 1}})}}{{{\mathop{\rm Re}\nolimits} \;({Y^{ - 1}})}} . $ | (2) |

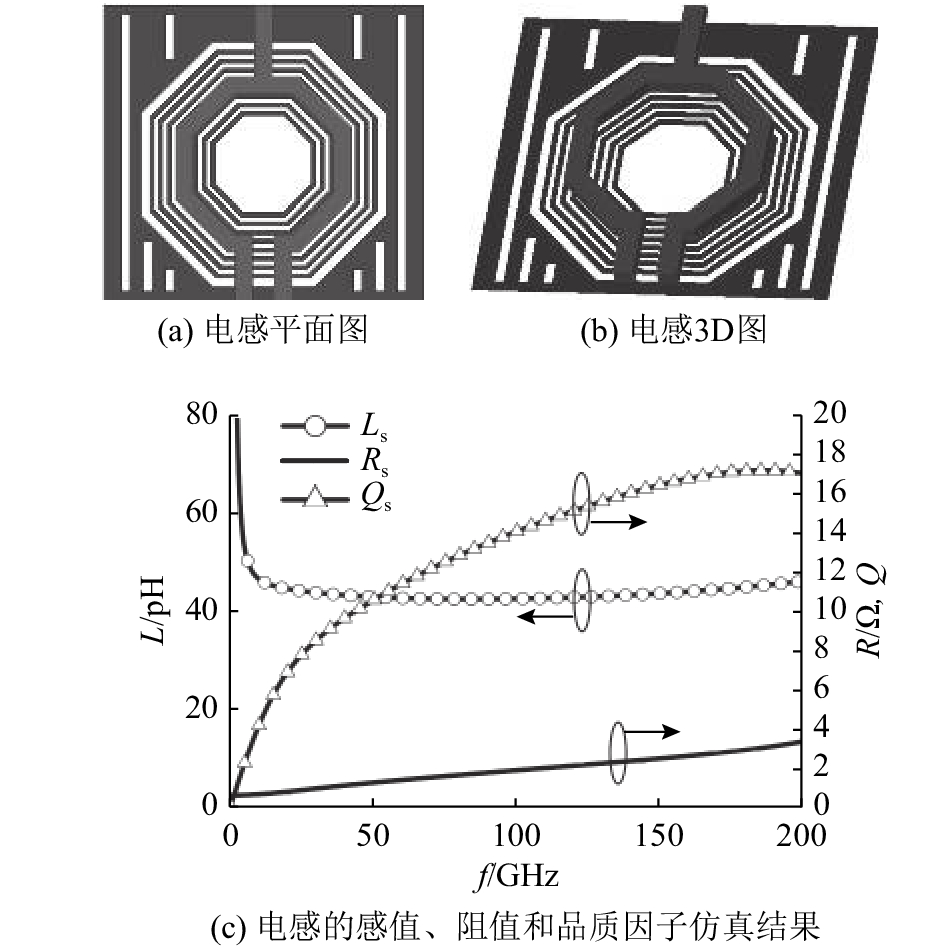

所设计电感的平面图与3D图如图4所示. 电感采用工艺中的厚金属(3.3 μm)设计以减少金属损耗. 理论上,增加金属线宽可以减少金属损耗,实际上增加线宽会使寄生电容相应增大,从而导致电感的自谐振频率降低,以致电感在电路中的应用受限. 因此,在保证电感品质因子的同时,通过优化电感的金属宽度确保电感的自谐振频率远远大于工作频率.

|

图 4 电感平面图、3D图及感值、阻值和品质因子仿真结果 Fig. 4 Planar layout of inductor with PGS, 3D layout of inductor with PGS and simulated results of inductance, resistance and quality factor |

采用工艺中的低层金属(M1)设计电感的回路地,减少衬底损耗. 这种回路地如图4所示,采用金属环和不规则金属共同构成电感的回路地. 该回路地降低了衬底涡旋电流对电感品质因子的影响. 同时,由楞次定律可知,电感上的变化电场会在金属环上感生电流,而金属环之间亦会感生电流. 由于金属环之间的感生电流方向相反,形成了相互减弱的磁场,从而减弱了回路地对电感的影响,改善了电感的品质因子. 此外,该回路地可以同时为电路的有源单元提供地通路.

感值L、电阻R、品质因子Q与频率f的关系如图4所示,该电感感值在文中电路的工作频率范围内大约为44 pH. 当工作频率为127.2 GHz时,电感的Q值为15.5. 电阻为2.22 Ω. 在0~200 GHz频率范围内,电感没有出现谐振现象.

变压器可以实现单端信号与差分信号的相互转换,具有阻抗匹配功能,同时变压器具有紧凑的结构,利于版图布局布线,因此在毫米波电路中倍受青睐. 文中设计了片上变压器,参与了VCO输出Buffer的匹配,并将输出的差分信号转为单端信号以方便测试. 片上变压器的集总参数模型如图5所示.

|

图 5 变压器的集总参数模型 Fig. 5 Transformer’s lumped parameter model |

图5中Li和Ls分别表示变压器初级/次级线圈的电感,Mu表示变压器的初级线圈与次级线圈之间的互感,相应的表达式及磁耦合系数k,初级/次级线圈的品质因子Qi和Qs的表达式如下:

| $ \begin{aligned}&{L_{\rm i}} = \displaystyle\frac{{{\mathop{\rm Im}\nolimits}\;({Z_{\rm i}})}}{\omega },\;{L_{\rm s}} = \displaystyle\frac{{{\mathop{\rm Im}\nolimits}\; ({Z_{\rm s}})}}{\omega },\\&M = \displaystyle\frac{{{\mathop{\rm Im}\nolimits}\; ({Z_{\rm {is}}})}}{\omega },\;k = \displaystyle\frac{M}{{\sqrt {{L_{\rm i}} \times {L_{\rm s}}} }},\\&{Q_{\rm i}} = \displaystyle\frac{{{\mathop{\rm Im}\nolimits} \; ({Z_{\rm i}})}}{{{\mathop{\rm Re}\nolimits} \, ({Z_{\rm i}})}},\;{Q_{\rm s}} = \displaystyle\frac{{{\mathop{\rm Im}\nolimits} \;({Z_{\rm s}})}}{{{\mathop{\rm Re}\nolimits} ({Z_{\rm s}})}}.\end{aligned} $ | (3) |

变压器次级线圈的一端接在信号焊盘上,另外一端接地,使其在信号通路上又具有ESD保护功能. 片上变压器的平面图及3D图如图6所示,采用工艺的顶层厚金属铜(3.3 μm)和次顶层金属铜(0.8 μm)设计叠层结构的片上变压器;在电路设计过程中,结合图5中变压器的模型及式(3),优化线圈金属宽度及线圈内径,评估变压器的耦合、品质因子、电感和互感情况,并与GSG焊盘同时实现了VCO电路输出Buffer到50 Ω的阻抗匹配. 文中变压器的线圈金属宽度为8 μm. 同时采用低层金属(M1)设计浮栅屏蔽结构来减小衬底涡旋电流及流入衬底的电流对变压器线圈的影响,降低变压器线圈的损耗,改善变压器的品质因子.

|

图 6 带浮栅结构的变压器的平面图和3D图 Fig. 6 Planar layout of transformer with floating strip barand 3D layout of transformer with floating strip bar |

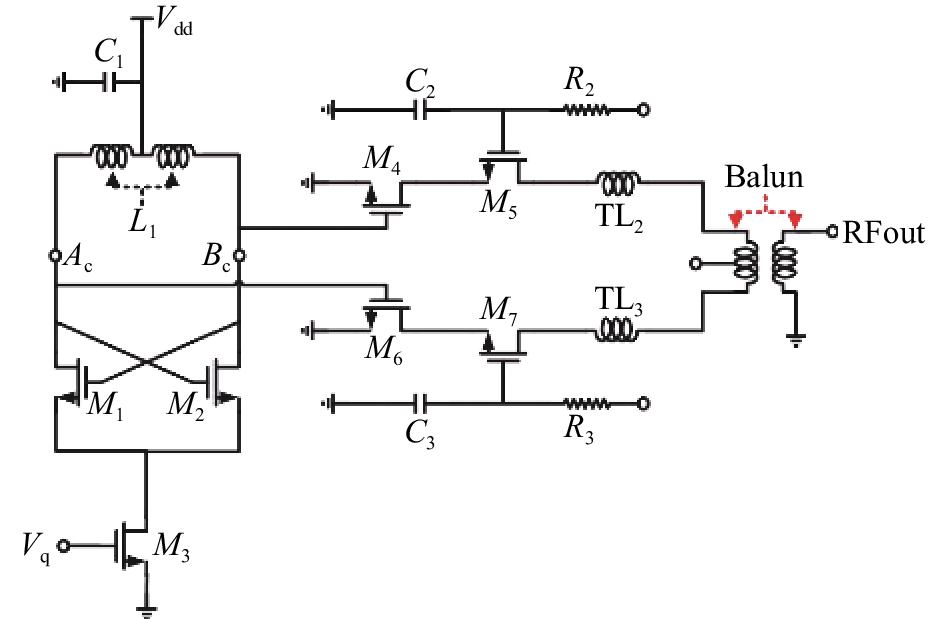

VCO的电路原理图如图7所示,其中M1、M2、M3共同组成了该电路的负阻单元,维持稳定输出信号,通过调节加在M3上的偏压Vq可以控制VCO输出频率. 电感L1与从Ac、Bc两点看进去寄生电容共同组成了LC谐振网络. M4、M5、M6、M7共同构成了VCO的输出Buffer,该Buffer采用共源. 共栅结构,以减小负载电阻对VCO的负阻单元的影响,确保VCO正常工作. 输出Buffer采用自偏置方式为共栅MOSFET提供偏压。通过电阻R2和R3对晶体管M5和M7自偏置方式为MOSFET提供偏压,VCO的负阻单元和输出Buffer之间直接相连,省略了级间耦合电容,规避了因引入电容而导致的电路工作频率的减小,同时VCO的电源Vdd可为共源MOSFET提供直流偏压,降低了电路版图的设计难度. 传输线TL2、TL3和变压器(Balun)共同实现了VCO电路的输出匹配;此外,变压器实现了差分转单端的功能,省略了隔直电容和扼流电感的使用;同时采用变压器中心抽头作为电源接口,方便了电路版图的布局与布线. VCO电路产生的信号通过RFout端口输出.

|

图 7 VCO电路原理图 Fig. 7 Circuit principle schematic of VCO |

如图7所示,LC谐振槽电路中的电容是从Ac、Bc两点看进去寄生电容. 图8(a)为负阻单元寄生电容示意图;其中CSG、CGD、CDS、CDB、CSB分别表示MOSFET的栅-源、栅-漏、漏-源、漏-衬底、源-衬底电容,并用脚号1、2、3区分相应的MOSFET的寄生电容.

为方便计算,将图8负阻单元寄生电容示意图中带有寄生电容的负阻单元电路等效为图中负阻单元寄生电容等效电路图. M1和M2的管子尺寸相同,寄生电容相同,因此在计算中用CSG1、CGD1、CDS1、CDB1、CSB1表示M1和M2的寄生电容.

根据图8(b)负阻单元寄生电容的等效电路计算,LC谐振网络的寄生电容:

| $ {C_{{\rm{tank}}}} = \displaystyle\frac{1}{2} \times \left( {{C_{{\rm{load}}}} + {C_{{\rm{DG1}}}} + {C_{{\rm{DB1}}}} + {C_{\rm{t}}}} \right) \,,$ | (4) |

| $ {C_{\rm{t}}} = \displaystyle\frac{{{C_{{\rm{DS1}}}} \times \left( {{C_{{\rm{DG3}}}} + {C_{{\rm{SG3}}}}} \right) \times \left( {2 \times {C_{{\rm{SB1}}}} + {C_{{\rm{DS3}}}} + {C_{{\rm{DB3}}}} + {C_{{\rm{DG3}}}} \times {C_{{\rm{SG3}}}}} \right)}}{{\left( {{C_{{\rm{DG3}}}} + {C_{{\rm{SG3}}}}} \right) \times \left( {2 \times {C_{{\rm{SB1}}}} + 2 \times {C_{{\rm{DS1}}}} + {C_{{\rm{DS3}}}} + {C_{{\rm{DB3}}}} + {C_{{\rm{DG3}}}} \times {C_{{\rm{SG3}}}}} \right)}} \,.$ |

因此,文中VCO的谐振频率为

| $ {f_{{\rm{osc}}}} = \displaystyle\frac{1}{{\sqrt {{L_{{\rm{tank}}}} \times {C_{{\rm{tank}}}}} }} .$ | (5) |

式中:Ltank为电路中使用的电感.

|

图 8 VCO电路负阻单元寄生电容示意图及其等效电路图 Fig. 8 Schematic of negative resistance cell of VCO including |

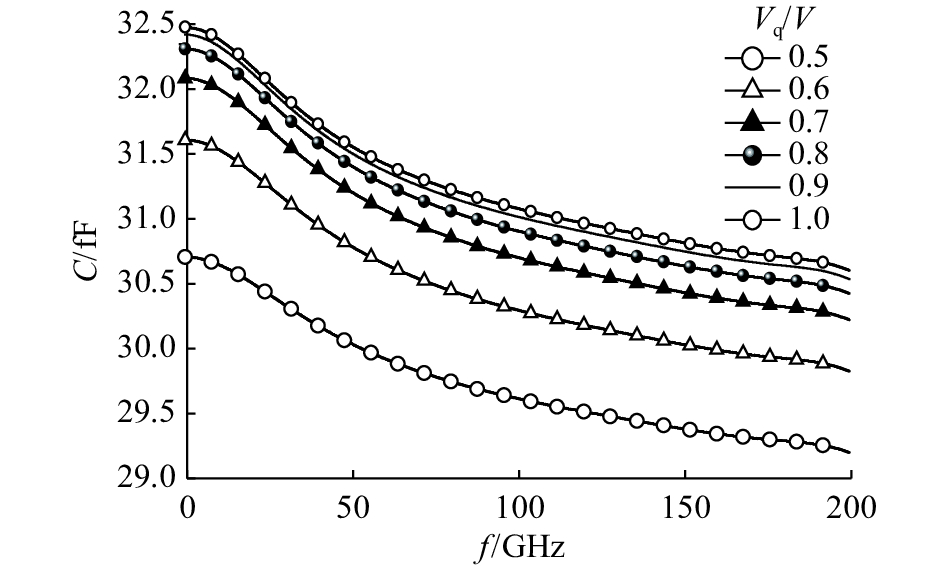

加在尾电流源管栅极上偏压的变化,会改变VCO负阻单元各个MOSFET的漏极与源极之间的电压,从而改变由MOSFET的漏/源与衬底形成的结电容变化,即CDB、CSB的变化,由式(4)和(6)可知,VCO的频率因加在尾电流源管栅极上偏压的改变产生了变化,实现了VCO振荡频率控制. 以0.1 V的步进改变尾电流管栅极上的偏压Vq,电容值C随频率f变化的曲线如图9所示.

|

图 9 负阻单元寄生电容尾电流源管栅极电压变化的仿真结果 Fig. 9 Simulated results of parasitic capacitance of negative cell vary as voltage applied to gate of tail current MOSFET |

所设计的VCO采用65 nm CMOS工艺进行加工,芯片照片如图10所示. 电路版图设计充分考虑了对称性,并对版图进行了优化. GSG测试焊盘、电感、传输线和片上变压器与有源电路的协同设计,使得电路版图变得更加紧凑. 电路中的电感、传输线均采用工艺中的顶层厚金属铜作为信号线;变压器采用叠层结构,初/次级线圈则分别采用顶层厚金属铜和次顶层金属铜. 电路信号通路及直流通路上均采用ESD保护. 包含GSG测试焊盘及所有的直流焊盘,该电路芯片的大小为405×440 μm2.

|

图 10 VCO芯片照片 Fig. 10 Photograph of VCO chip |

VCO采用在片测试,测试框图如图11所示,测试中采用的频谱仪为中国电子科技集团公司第四十一研究所自主研发的A4051F,该频谱仪由频谱仪主机和扩频模块共同组成. 谐波混频器将被测的D波段信号转换成低频信号送至频谱仪主机进行处理,从而完成D波段测试,其功率校准到扩频模块端口.

|

图 11 VCO电路测试示意图 Fig. 11 Measured setup diagram of VCO |

频谱仪和GSG探针之间采用波导连接,该波导在D波段的损耗为2.5 dB;GSG探针采用Infinity WR 6.5波导探针,其在D波段的损耗为2 dB.

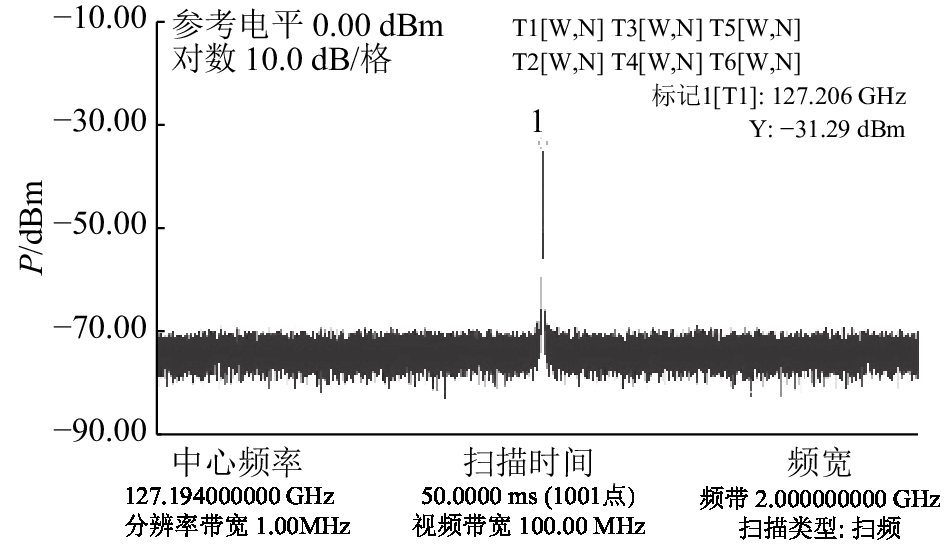

当Vdd供电1.4 V、Vdc供电1.6 V、Vq供电为0.8 V时电路的输出频率为127.2 GHz,输出信号频谱如图12所示. 结合波导及探针的损耗可知,该信号的输出功率为–26.8 dBm.

|

图 12 尾电流源管栅极电压为0.8 V时VCO输出频谱(测试) Fig. 12 Measured output spectrum of VCO when voltage applied to gate of tail current MOSFET is 0.8 V |

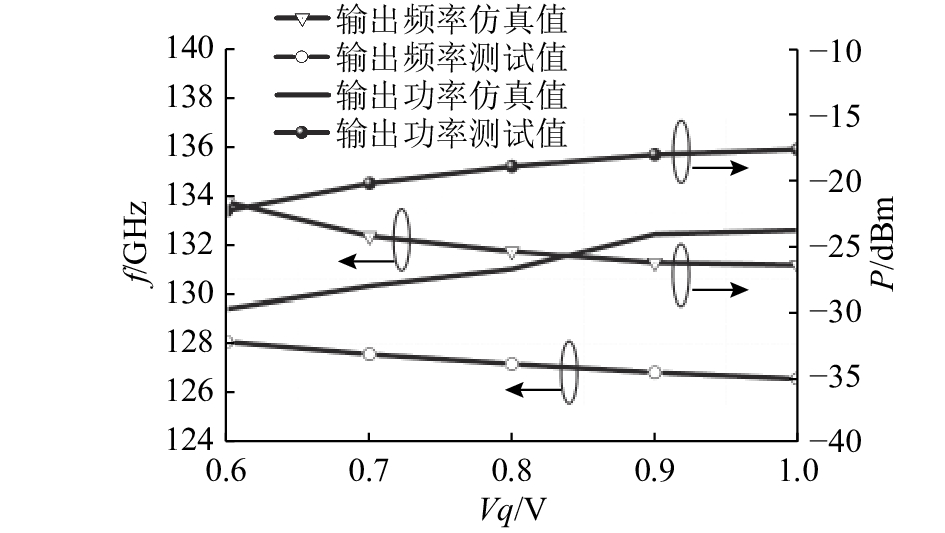

改变加在Vq上的偏压,图13给出了VCO的输出频率f和输出功率P随着控制电压Vq变化的测试与仿真结果. 从图中可以看出,输出频率随着加载在VCO负阻单元尾电流源管上栅极电压的变化而改变,实现了通过电压改变振荡电路输出频率的控制,同时通过实验证明了前文中对应电压改变Ctank的分析. 图13中亦显示了VCO的仿真结果,从对比结果来看,测试得到的频率小于仿真值. 以仿真频率值为基准,在整个调谐范围内,频率偏移最大百分比为4.34%,VCO调谐范围降低了1.1 GHz.

|

图 13 VCO输出频率/功率随尾电流源管栅极电压变化的测试与仿真图 Fig. 13 Measured and simulated output frequency and power of VCO vary as voltage applied to gate of tail current MOSFET |

造成频率偏移及调谐范围减小的主要原因如下:1)电路加工时,随机添加了填充金属以应对工艺中金属密度的要求,这些填充金属与无源器件的信号线之间形成的电容,在电磁仿真时不能完全考虑,从而导致仿真值与测试值存在差异;2)工艺库中提供的有源器件模型在电路设计频段为扩展模型,导致通过仿真得到的MOSFET电容值与实际测试值存在偏差,体现在VCO输出频率及调谐范围上的差异. 频率偏移会导致VCO输出匹配出现一定程度的失配,从而导致测试得到的输出功率减小. 如图13所示,与仿真值对比,在整个调谐范围内,测试的输出功率减小了5~7.9 dBm.

由于缺少测试相位噪声的仪器,文中基于VCO频率偏移的分析,对VCO电路建模并仿真,使电路工作在测试频点上,并仿真衡量了VCO的相位噪声,如图14所示. 图中给出了VCO对应不同输出频率f时相位噪声(phase noise,PN)偏频分别为1 MHz和10 MHz的仿真结果. 由图中仿真结果可知,电路在偏频为1 MHz时的相位噪声大于–76 dBc/Hz.

|

图 14 VCO在偏频为1、10 M时相位噪声随尾电流源管栅极电压变化仿真图 Fig. 14 Simulated phase noise of VCO vary as voltage applied to gate of tail current MOSFET when frequency offset are 1 M and 10 M |

表1列出了近几年报道的D波段的VCO及本文电路的各项指标. 其中,

| $ {\rm{Fo{M^T}} }= {\rm{PN}} - 20\,\log\; \left(\displaystyle\frac{{{f_0}}}{{\Delta f}} \times \displaystyle\frac{{\rm{FTR}}}{{10}}\right) + 10\,\log\; \left(\displaystyle\frac{{{P_{\rm{DC}}}}} {{1P_{\rm ref}}}\right) \,.$ | (6) |

式中:PN10、PN1分别表示偏频为10 MHz、1 MHz时的相位噪声,f0为振荡电路中心频率,FTR表示频率调谐范围,PDC表示直流功耗. Pout表示VCO电路的输出功率,Pref=1 mW,为一个参照量,A表示VCO电路的芯片面积,FoMT(figures of merit)用来综合评价VCO的性能.

| 表 1 D波段VCO电路的性能比较 Table 1 Performance comparison of published D-band fundamental VCO |

从与表中的基波VCO[10]对比可以看到,文中提出的基波振荡频率高,但VCO电路功耗较之偏大,导致了FoMT值并非最优,该功耗包含了VCO自身功耗和输出Buffer电路功耗,分别为11.2 mW和20.0 mW,输出Buffer占了VCO电路功耗的64.1%,这主要因为电路设计时为了减小输出Buffer电路带给VCO的阻性负载和增加电路的钝性,输出Buffer电路与VCO电路中的负阻单元直接连接,从而导致VCO的供电电压Vdd直接加载在输出Buffer电路的栅极上,从而导致功耗偏大. 由于在设计中使用了传输线、变压器等片上器件,本文所提电路面积比表中其他电路的面积小.

5 结 语基于65 nm CMOS工艺,研究并设计了一款基波压控振荡器. 采用交叉耦合差分对管作为振荡器的负阻单元维持电路稳定输出信号,通过调节负阻单元尾电流晶体管的偏压实现振荡器的频率调谐. 电路实现了输出信号频率为126.6~128.1 GHz、调谐范围为1.5 GHz的压控振荡器电路. 当电路工作频率为127.2 GHz时,测试得到的输出功率为–26.8 dBm,仿真得到的在1 MHz处的最小相位噪声为–86.3 dBc/Hz. 芯片面积为405 μm×440 μm.

所设计的压控振荡器适用于毫米波成像、检测及高速通信等应用场合,可为对应的领域提供毫米波信号,并为毫米波信号源、毫米波频率综合器等系统电路的研究与设计奠定了基础.

| [1] |

XU Z W, GU Q J, WU Y C, et al. D-band CMOS transmitter and receiver for multi-giga bit/sec wireless data link[C] // IEEE Custom Integrated Circuits Conference (CICC). San Jose: IEEE, 2010:1–4. http://ieeexplore.ieee.org/document/5617617/

|

| [2] |

DEFERM N, REYNAERT P R. A 120 GHz fully integrated 10 Gb/s short-range star-QAM wireless transmitter with on-chip bond wire antenna in 45 nm low power CMOS[J]. IEEE Journal of Solid-State Circuits (JSSC), 2014, 49(7): 1606-1616. DOI:10.1109/JSSC.2014.2319250 |

| [3] |

MOSTAJERAN A, CATHELIN A, AFSHARI E,. A 170 GHz fully integrated single-chip FMCW imaging radar with 3D imaging capability[J]. IEEE Journal of Solid-State Circuits (JSSC), 2017, 52(10): 2721-2734. DOI:10.1109/JSSC.2017.2725963 |

| [4] |

SENGUPTA K, HAJIMIRI A. Sub-THz beam-forming using near-field coupling of distributed active radiator arrays [C] // IEEE Radio Frequency Integrated Circuits Symposium (RFIC). Baltimore: IEEE, 2011:1–4. https://chic.caltech.edu/wp-content/uploads/2013/05/Sengupta_Radio-Freq-Integ-Cir-Sym_Jun2011.pdf

|

| [5] |

WANG Z, CHIANG P Y, NAZARI P, et al. A CMOS 210-GHz fundamental transceiver with OOK modulation[J]. IEEE Journal of Solid-State Circuits (JSSC), 2014, 49(3): 564-580. DOI:10.1109/JSSC.2013.2297415 |

| [6] |

ZHANG J, SHARMA N, CHOI W, et al. 85-to-127 GHz CMOS signal generation using a quadrature VCO with passive coupling and broadband harmonic combining for rotational spectroscopy[J]. IEEE Journal of Solid-State Circuits (JSSC), 2015, 50(6): 1361-1371. DOI:10.1109/JSSC.2015.2416312 |

| [7] |

HOLISAZ H, SAFAVI-NAEINI S. A low noise D-band VCO with a wide bandwidth and a steady output power[J]. IEEE Microwave and Wireless Components Letters (MWCL), 2015, 25(11): 742-744. DOI:10.1109/LMWC.2015.2481083 |

| [8] |

SHANG Y, YU H, LINAG Y, et al. Millimeter-wave sources at 60 and 140 GHz by magnetic plasmon waveguide based in phase coupled oscillator network in 65-nm CMOS[J]. IEEE Transactions on Microwave Theory and Techniques (TMTT), 2016, 64(5): 1560-1571. DOI:10.1109/TMTT.2016.2544308 |

| [9] |

HUANG P C, TSAI M D, VENDELIN G D, et al. A low-power 114-GHz push-push CMOS VCO using LC source degeneration[J]. IEEE Journal of Solid-State Circuits (JSSC), 2007, 42(6): 1230-1239. DOI:10.1109/JSSC.2007.897136 |

| [10] |

VOLKAERTS W, STEYAERT M, REYNAERT P. 118 GHz fundamental VCO with 7.8% tuning range in 65 nm CMOS [C] // IEEE Radio Frequency Integrated Circuits Symposium (RFIC). Baltimore: IEEE, 2011:1–4. http://ieeexplore.ieee.org/document/5940642/

|

| [11] |

ADNAN M, AFSHARI E. A 105-GHz VCO with 9.5% tuning range and 2.8-mW peak output power in a 65-nm bulk CMOS process[J]. IEEE Transactions on Microwave Theory and Techniques (TMTT), 2014, 62(4): 753-762. DOI:10.1109/TMTT.2014.2309940 |

| [12] |

LIU J, YU Z P, SUN L L. A broadband model over 1-220 GHz for GSG pad structures in RF CMOS[J]. IEEE Electron Device Letters (EDL), 2014, 35(7): 696-698. DOI:10.1109/LED.2014.2322366 |

| [13] |

LEESON D. A simple model of feedback oscillator noise spectrum[J]. Proceedings of IEEE, 1996, 54: 329-330. |