随着集成电路以及医疗检测技术的不断进步, 各类疾病患者越来越多的使用穿戴式医疗设备对自身的健康和病情状况进行实时监控[1-6].通常这类穿戴式设备都使用微型电池供电, 体积和设备空间严重限制了电池容量.为了延长设备工作时长, 就必须对其中的集成电路芯片进行低功耗设计.此外, 为了提取微弱的生物电信号, 芯片还需要具有足够低的等效输入噪声, 才能在模数转换时获得较高的信噪比输出.作为芯片中模拟信号与数字信号的桥梁, 模数转换器设计面临着低功耗、高精度的设计挑战.

在Sigma-Delta模数转换器中, 跨导放大器(transconduntor operational amplifier, OTA)是电路的主要功耗来源.为了实现低功耗的跨导放大器, 工程师们提出了多种电路解决方案.Pun等[7-9]提出了体驱动OTA和数字辅助型OTA.体驱动OTA较小的等效输出跨导, 使得该电路的噪声性能较差, 且只能应用在信号带宽有限的设计中.数字辅助型OTA中增加的数字校准电路, 在降低噪声的同时增加了多余的功耗.文献[10]中的比较器型OTA虽然采用电流源消除了反馈回路中的不稳定点, 但该电路无法在较低的电源电压环境下工作.为了克服这些设计困难, 本文采用反向器作为积分器中的放大器电路[11-12].在极低的电源电压下, 实现Sigma-Delta调制器, 完成低功耗、高精度的模数转换功能.

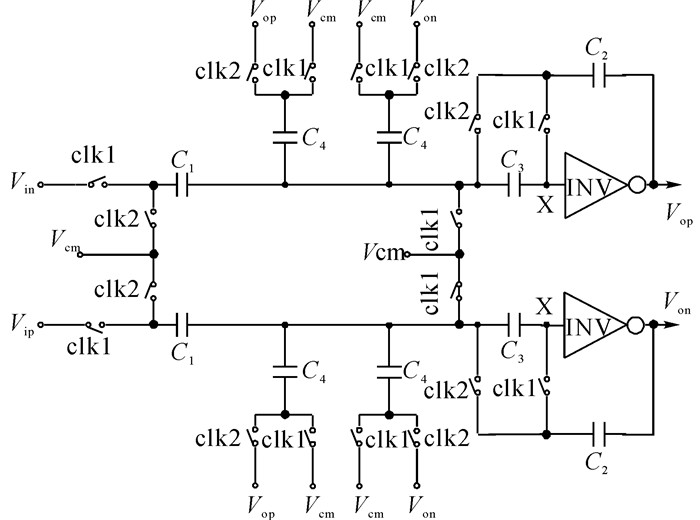

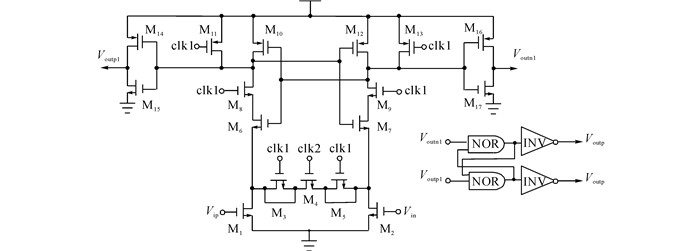

1 电路原理本研究采用带有自调零机制的伪差分反相器积分器, 如图 1所示[13].该电路由两相非交叠时钟clk1和clk2进行控制, 分为采样相和积分相2个状态.当clk1为高电平时, 积分器进行采样操作, 输入信号被采样至采样电容C1上.同时共模电压Vcm和反向器的输入失调电压分别被采样到补偿电容C3的左、右极板中;当clk2为高电平时, 积分器进行积分操作, 点X的电压仍然保持为反向器的失调电压, 又因为电容C3的电荷保持不变, 所以在其左极板形成共模的虚地点, 这样就消除了反向器失调电压无法形成虚地点的问题.

|

图 1 带有自调零机制的伪差分反相器积分器 Fig. 1 Auto-zeroing Pseudo-differential inverter-based integrator |

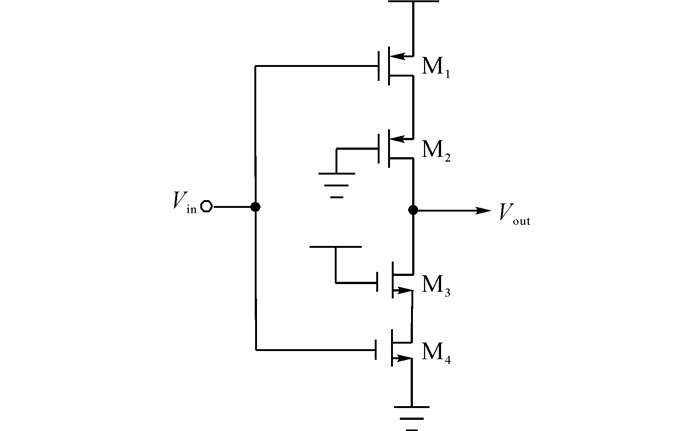

在积分器中, 放大器的直流增益决定了电荷转移的精度, 而单位增益带宽则决定了工作速度.生物电信号的带宽通常在赫兹级, 对放大器的带宽约束较小.为了增大直流增益, 选择共源共栅反相器结构进行设计, 其电路如图 2所示.

|

图 2 共源共栅反相器 Fig. 2 Cascode inverter |

在低电源电压时, 将晶体管偏置在亚阈值区, 可以获得最大的直流增益.但由于共源共栅反相器在电源到地的通路上层叠了4个晶体管, 使得等效放大器的输出摆幅受到限制, 也一定程度上缩小了输出信号的动态范围.

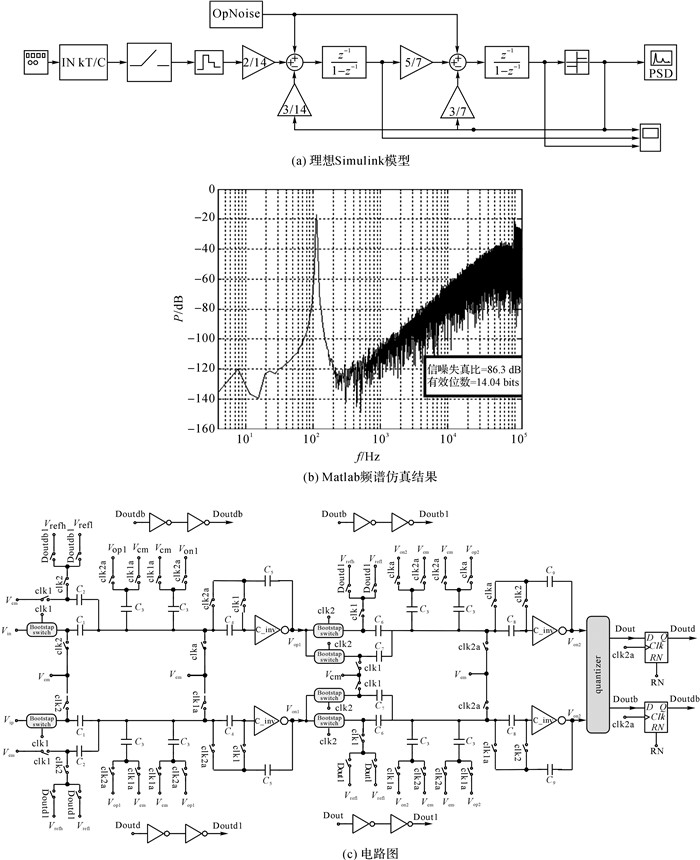

2 电路设计本文设计的二阶14 bit/500 Hz Sigma-Delta调制器的理想Simulink模型和电路如图 3所示.调制器电路采用稳定的二阶反馈结构.根据图 4中的行为级仿真结果, 为了获得14 bit精度, 在采用256倍过采样率时, 反相器直流增益需要达到46 dB(200倍).图 4中,f为频率,P为功率.与传统OTA结构的积分器相比, 本文主要是通过使用反向器替代OTA进行设计.同时为了消除反相器失调电压对输出精度的影响, 增加了自调零失调消除机制, 从而实现与采用OTA结构相当的信噪比输出.该机制使差分积分电路仅引入2个开关和2个自调零电容, 增加了一部分芯片面积, 但没有增加额外的功耗开销.采样电容、积分电容和失调补偿电容值如表 1所示.

|

图 3 二阶14 bit/500 Hz Sigma-Delta调制器 Fig. 3 Second 14 bit/500 Hz Sigma-Delta modulator |

|

图 4 栅压自举开关电路 Fig. 4 Bootstrap switch circuit |

| 表 1 Sigma-Delta积分器中的电容值 Table 1 Integrator capacitor value of Sigma-Delta modulator |

参考高电平Vrefh和低电平Vrefl分别设置为电源和地, 即理想量化范围为600 mV.clk1和clk2为非交叠的两相时钟, clk1a和clk2a分别为clk1和clk2的延迟关断时钟, 目的是为降低电荷的注入效应.为了在低至0.6 V电源电压时, 保持开关栅漏电压恒定, 提高导通阻抗在输入范围内的平坦性, 降低采样开关引入的谐波失真, 输入开关选择栅压自举开关进行设计.

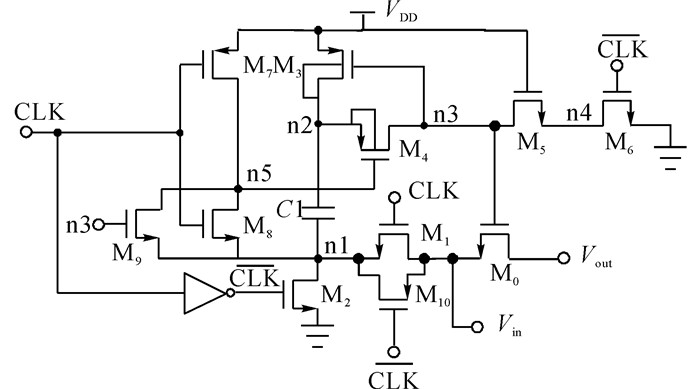

栅压自举开关电路[14]如图 4所示, 其原理在于通过在开关晶体管M0的栅-源两端加入恒定直流电压, 使其在输入信号变化时, 导通电阻仍能保持恒定值.具体工作方式为:当CLK为低时, NMOS管M2导通, 将电容C1的下极板连接至地电位.同时NMOS晶体管M5和M6导通, 关闭开关晶体管M0, 并将n3节点连接至地电位, 使PMOS晶体管M3导通, 将C1的上极板连接至电源VDD, 完成对C1的充电.M1和M10组成的虚拟开关管, 此时也关闭, 使得输入信号Vin与内部结点隔离;当CLK为高时, NMOS晶体管M2截止, 虚拟开关管导通, 将电容C1的下极板连接至M0的源极;同时NMOS晶体管M8导通, 将M4的栅极拉低到地电位, 使其导通, 从而将电容C1的上极板连接至M0的栅极, 最终将电源电压VDD加载在M0的栅-源两极, 实现控制电压的恒定性.

量化器采用高速动态比较器结构, 电路如图 5所示.冗余晶体管M3和M5在时钟clk1控制下将量化器进行复位, 消除残余电荷, 保证了比较精度.

|

图 5 量化器电路 Fig. 5 Quantizer circuit |

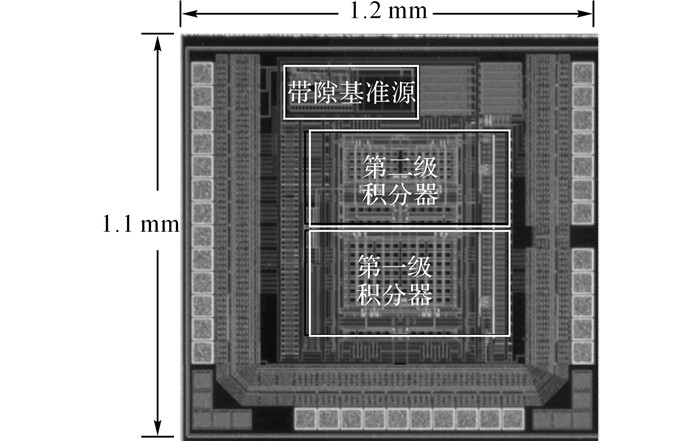

本次设计的Sigma-Delta调制器电路采用SMIC 0.13 μm 1P8M混合信号工艺流片实现, 电源电压0.6 V.包含输入、输出单元的芯片照片如图 6所示, 整体面积为1.32 mm, 其中核心电路面积为0.72 mm.

|

图 6 Sigma-Delta调制器芯片照片 Fig. 6 Photograph of Sigma-Delta modulator |

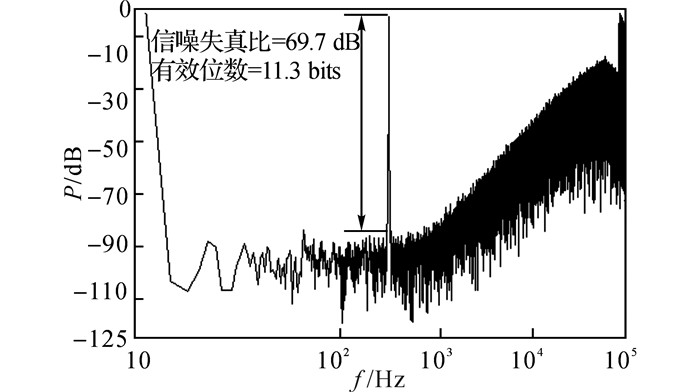

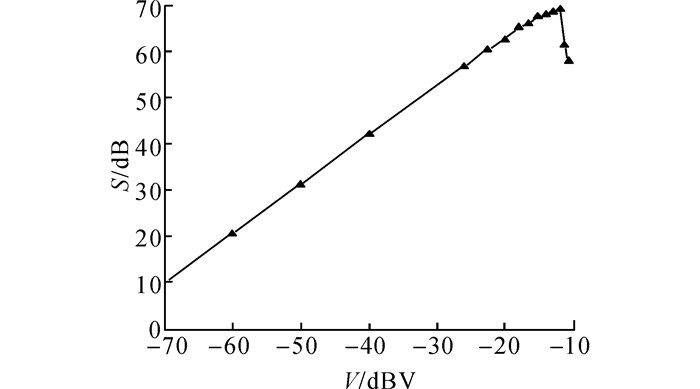

完成流片后首先对输出信号频谱进行信噪比测试.当电源电压0.6 V, 输入信号频率400 Hz, 差分峰峰值幅度500 mV时, 输出信号功率谱如图 7所示.可以看到输出最大信噪失真比69.7 dB, 有效精度11.3 bit, 表明Sigma-Delta调制器在低电源电压时仍达到了较高的输出信号精度.输出信噪失真比与输入信号幅度的关系如图 8所示, 表明该电路保持了接近500 mV的输入量化范围.图中,V为输入信号幅度,S为输出信噪失真比.

|

图 7 Sigma-Delta调制器电路FFT频谱分析结果 Fig. 7 FFT spectrum results of Sigma-Delta modulator |

|

图 8 输出信噪失真比与输入信号幅度的关系 Fig. 8 Relationship of SNDR and input amplitude |

最后固定输入频率为400 Hz, 输入信号峰峰值为500 mV, 改变电源电压, 在0.6~0.8 V的范围内测试输出信号频谱.在该电压范围内, Sigma-Delta调制器保持了稳定的输出信噪失真比, 维持在70 dB附近, 不会受到电源电压变化的影响.在0.6 V时功耗仅有5.07 μW.与传统OTA结构的积分器相比, 采用反相器结构的二阶Sigma-Delta调制器功耗可下降80%左右;但由于采用了自调零失调消除机制, 输出信号比与传统结构相当;不足之处在于基于反向器的Sigma-Delta调制器带宽受到极大限制, 只能满足信号带宽为赫兹量级的应用;且鲁棒性和抗工艺角变化能力较弱.

将本文电路测试结果与以往发表论文中反相器型二阶Sigma-Delta调制器的结果进行比较, 结果如表 2所示.本文设计的电路在中等电源电压环境下, 相对较小的信号带宽之内, 获得了最高的输出信噪比和最低的功耗, 性能优秀, 与文献[15-18]中的学术成果具有极高的可比性.

| 表 2 电路测试性能比较 Table 2 Comparison of circuit measurement performance |

针对低功耗、高精度模数转换在穿戴式医疗设备中的应用, 本文采用SMIC 0.13 μm 1P8M混合信号工艺设计了一种基于共源共栅反相器的低功耗14 bit/500 Hz Sigma-Delta调制器电路.该电路采用二阶反馈型调制器结构.在0.6 V的低电源电压环境下, 该电路首先采用栅压自举开关完成了高精度的输入信号采样.为了降低调制器中积分器的功耗, 采用共源共栅反相器取代传统Sigma-Delta调制器中的OTA进行设计, 极大地降低了电路功耗.电路测试结果表明, 在时钟频率256 kHz, 信号带宽500 Hz内, Sigma-Delta调制器输出信号最大信噪失真比为69.7 dB, 有效精度为11.3 bit, 功耗仅有5.07 μW.该电路与参考文献中的电路测试结果相比具有最高的信噪失真比和最低的功率消耗, 整体性能具有极高的可比性.

| [1] |

WANG Y C, KE K R, QIN W H, et al. A low power low noise analog front end for portable healthcare system[J]. Journal of Semiconductors, 2015, 36(10): 105008-7. DOI:10.1088/1674-4926/36/10/105008 |

| [2] |

MAO Y Q, GAO T Q, XU X D, et al. A fully integrated CMOS super-regenerative wake-up receiver for EEG applications[J]. Journal of Semiconductors, 2016, 37(9): 095001-6. DOI:10.1088/1674-4926/37/9/095001 |

| [3] |

XIAO G L, QIN Y L, XU W L, et al. Demonstration of a fully differential VGA chip with small THD for ECG acquisition system[J]. Journal of Semiconductors, 2015, 36(10): 105005-6. DOI:10.1088/1674-4926/36/10/105005 |

| [4] |

DUAN J H, LAN C, XU W L, et al. An OTA-C filter for ECG acquisition systems with highly linear range and less passband attenuation[J]. Journal of Semiconductors, 2015, 36(5): 055006-6. DOI:10.1088/1674-4926/36/5/055006 |

| [5] |

DAI L, LIU W K, LU Y, et al. A 410μW, 70 dB SNR high performance analog front-end for portable audioapplication[J]. Journal of Semiconductors, 2014, 35(10): 105013-6. DOI:10.1088/1674-4926/35/10/105013 |

| [6] |

PU X F, WAN L, ZHANG H, et al. A low-power portable ECG sensor interface with dry electrodes[J]. Journal of Semiconductors, 2013, 34(5): 055002-6. DOI:10.1088/1674-4926/34/5/055002 |

| [7] |

PUN K P, CHATTERJEE S, KINGET P. A 0.5-V 74-dB SNDR 25kHz CT Sigma-Delta modulator withreturn-to-open DAC[J]. IEEE Journal of Solid-StateCircuits, 2007, 42(3): 496-507. DOI:10.1109/JSSC.2006.891716 |

| [8] |

MURMANN B, BOSER B. A 12-bit 75-MS/s pipelined ADC using open-loop residue amplification[J]. IEEE Journal of Solid-State Circuits, 2003, 38(12): 2040-2050. DOI:10.1109/JSSC.2003.819167 |

| [9] |

SIGRAGUSA E, GALTON I. A digitally enhanced 1.8-V 15-bit 40-MSample/s CMOS pipelined ADC[J]. IEEE Journal of Solid-State Circuits, 2004, 39(12): 2126-2138. DOI:10.1109/JSSC.2004.836230 |

| [10] |

FIORENZA J K, SEPKE T, HOLLOWAY P, et al. Comparator-based switch-capacitor circuits for scaled CMOS technologies[J]. IEEE Journal of Solid-State Circuits, 2006, 41(12): 2658-2668. DOI:10.1109/JSSC.2006.884330 |

| [11] |

CHAE Y, HAN G. A low power sigma-delta modulator using class-C inverter[C]//2007 IEEE Symposium on Vlsi Circuits. Kyoto: IEEE, 2007: 240-241. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4342734

|

| [12] |

CHAE Y, LEE I, HAN G. A 0. 7-V 36-μW 85dB-DR audio Sigma-Delta modulator using class-C inverter[C]//2008 IEEE Solid-State Circuits Conference. San Francisco: IEEE, 2008: 490-491. http://www.mendeley.com/research/07v-36mu-w-85dbdr-audio-delta-sigma-modulator-using-classc-inverter/

|

| [13] |

CHAE Y, HAN G. Low voltage, low power, inverter-based switch-capacitor delta-sigma modulator[J]. IEEE Journal of Solid-State Circuits, 2009, 44(2): 458-471. DOI:10.1109/JSSC.2008.2010973 |

| [14] |

ANDREW M, GRAY P R. A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter[J]. Journal of Solid-State Circuits, 1999, 34(5): 599-603. DOI:10.1109/4.760369 |

| [15] |

ABIRI E, POUMOORI N. A 0.5-V 17μW second-order Delta-Sigma modulator based on a self-biased digital inverter in 0.13μm CMOS[J]. Journal of Basic and Applied Scientific Rearch, 2012, 2(4): 3476-3480. |

| [16] |

MICHAEL F, STEYAERT M. A 250 mV 7.5μW 61dB SNDR SC Sigma-Delta modulator using near-threshold-voltage-biased inverter amplifier in 130 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2012, 47(3): 709-721. DOI:10.1109/JSSC.2011.2179732 |

| [17] |

YANG Y, YANG Y, LU L, et al. Inverter-based second-order Sigma-Delta modulator for smart sensor[J]. Electronics letters, 2013, 49(7): 31-32. |

| [18] |

YOON Y, ROH H, ROH J. A true 0.4 V Delta-Sigma modulator using a mixed DDA integrator without clock boosted switches[J]. IEEE Transactions on Circuits and Systems-Ⅱ:Express Briefs, 2014, 61(4): 229-233. DOI:10.1109/TCSII.2014.2305214 |