以移动通信、互联网和智能终端等为代表的计算机和信息技术已在短短的几年间彻底改变了人类社会的生产和生活方式,人类已经进入到了大数据和智能科技时代.当下,从城市安防到社区监控,图像传感器已遍布城市的每个角落.数据时代不仅需要好的传感设备、海量存储和快速传播技术,还迫切需要对这些信息进行智能分类、识别和检索.让计算机能够像人类一样分析和理解真实世界中的图像一直是人类的梦想,然而现有的计算机图像理解技术无法满足这样的需求.

从2006年开始,深度学习(deep learning,DL)[1]技术开始受到学术界的广泛关注,在2012年举行的大规模图像识别挑战赛上,基于神经网络模型的AlexNet将传统图像识别错误率降低了41%,进而引发深度学习技术在工业界的研究热潮.当前基于深度学习的目标识别技术在图像识别[2]、语音识别[3]、自然语言处理等领域都取得了重大突破.深度学习由一系列神经网络模型组成,包括卷积神经网络(convolutional neural network,CNN)[4]、受限玻尔兹曼机(restricted Boltzmann machine,RBM)[5]、自动编码机[6]、循环神经网络(recurrent neural network,RNN)[7]等常用模型.其中基于卷积神经网络的深度学习模型是当前图像识别领域中的主力,在2012—2017年的大规模图像识别挑战赛(large scale visual recognition challenge,ILSVRC)中都取得了最佳识别率.高识别率同时带来了巨大的计算量,卷积神经网路模型中卷积层的计算量约占整个模型计算量的85%以上[8],因此,目前的许多研究大多是针对卷积神经网络的加速器,如GPU(graphic processing unit)[9-10]、FPGA(field programmable gated array)[11-12]、ASIC(application specific integrated circuit)[13-15]、向量DSP(digital signal processor)等.

向量处理器是一种具有多功能单元、多处理部件的新颖体系结构[16],其处理器内部包括面向流控处理和逻辑计算的标量处理部件和针对密集型大规模数据处理的向量处理部件,该向量处理部件内部集成了丰富的能够执行向量计算的向量处理单元,每个处理单元又具有若干个浮点乘加器和定点乘加器,支持单条指令完成浮点或定点的乘累加操作,能够提供强大的计算能力.然而针对新颖的微处理器结构,配套的软件开发工具也是一个重要的研究内容,如何通过软件编程的方式将多核向量处理器内部的所有硬件资源利用起来,发挥其多功能部件、多处理单元、充分利用各个层级的并行性,将不同的应用高效的映射是当前向量化程序面临的一大难题[17].

本文以二维矩阵卷积的计算为研究对象,面向多核向量处理器FT2000展开并行算法与性能优化研究.1)分析算法加速瓶颈并设计相应的并行方案;2)针对向量处理器的体系结构特点提出一种提高数据复用率的向量化实现方法;3)提出一种针对多核向量处理器的矩阵卷积并行实现方案;4)对比分析2种矩阵卷积计算模式对卷积实现性能的影响.

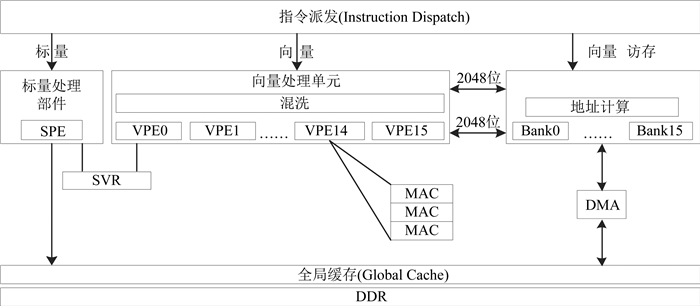

1 向量处理器体系结构与优化策略 1.1 微处理器体系结构FT2000是一种面向密集型浮点计算的12核向量处理器,单核结构如图 1所示,12核的单精度浮点性能达2.4TFLOPS,12个核是一个同构的微处理器核通过环形互联网络连接起来,单核内部集成向量处理单元和标量处理器单元,标量单元负责控制和逻辑计算,向量单元主要面向密集型计算,其包含16个向量处理单元,每个处理单元由若干浮点乘加单元和寄存器文件构成,所有的向量处理单元可以统一编址.此外,向量处理单元和标量处理单元可以通过共享寄存器进行数据交互,并且通过广播操作支持标量寄存器到向量寄存器的广播操作.向量处理单元可以同时发射11条指令,该执行包可以由若干条向量指令和若干条标量指令组成,指令派发部件可以对该执行包中的指令进行译码并指派到相应的功能单元去执行,标量处理单元具有本地标量存储体,主要存放需要标量来处理的数据,比如逻辑操作、地址计算等,因此,标量存储体空间较小,而向量处理单元主要存放需要进行大规模密集型计算的数据,因此,其存储体规模较大,标量存储体约96 KB,向量存储体约768 KB.环形互联网络上面的12个处理器核可以通过共享DDR的方式通过DMA操作进行DDR与核内数据的相互传输,同时DDR也支持全局缓存,方便多核间的数据共享与交互.

|

图 1 FT2000处理器体系结构 Fig. 1 Architecture of processor FT2000 |

(1) 循环展开.

循环展开是一种常用的程序优化方法,可以通过减少循环体的循环次数,减少分支执行时间来为流水线提供更多的并行机会,是手工汇编优化程序的主要方法.目前的编译器一般只对循环体很小的内循环进行展开,因此可能损失一些计算性能,尤其是对循环嵌套较多的循环体,编译器的优化效果不明显,因此可以通过手工汇编展开的方法来进行优化,由于CNN中的卷积计算具有多重循环体,对其核心代码采用手工汇编优化将大大提高程序执行效率.

(2) 指令级并行.

向量处理器有许多不同的功能单元,若能够利用其可以同时执行的特点,就可以大幅提高执行速度.现代处理器将指令操作划分为不同的阶段,每个阶段由不同的单元执行,这样多个操作就可以在处理器的多个单元上流水执行,流水线技术也是向量处理器优化的一个重点.此外,指令级并行还包括乱序执行、多发射、VLIW和分支预测等.

(3) 向量化并行.

向量化[18]是指一条向量指令可以同时操作向量寄存器中的多个元素,是一种数据并行模式,也是向量处理器提升性能的重要方法,如X86的SSE/AVX、ARM的NEON,都是基于SIMD模式.另一种数据并行的方式是SIMT,是GPU采用的向量化方法.本文优化主要采用SIMD.

(4) 缓存优化.

处理器的时钟频率和计算性能以超乎想象的速度增长,但是主存(DRAM)的访问速度的增长却缓慢的多,虽然Cache和预取能够减少平均访存时间,但仍不能从根本上解决问题,因此,在缓存优化过程中采用双Buffer机制,通过将计算时间和传输时间重叠,也可以大大提高程序的执行效率.

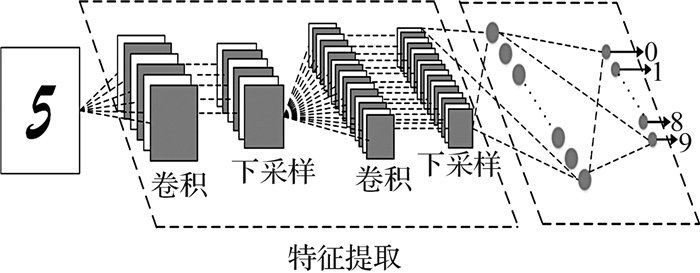

2 矩阵卷积算法介绍与分析 2.1 卷积神经网络的基本结构如图 2所示为一个典型CNN的基本结构,主要包括卷积层、池化层和全连接层,而其中卷积层的计算时间约占整个模型计算量的85%,因此加速CNN模型中的卷积计算成为当前神经网络加速的一个研究热点.

|

图 2 典型卷积神经网络结构 Fig. 2 Typical convolutional neural network (CNN) structure |

二维卷积常用于图像处理中,给定一个图像Xij(1≤i≤M, 1≤j≤N)和滤波器fij(1≤i≤m, 1≤j≤n),一般m<M, n<N,卷积的输出为

| $ {y_{ij}} = \sum\limits_{u = 1}^m {\sum\limits_{v = 1}^n {\left( {{f_{uv}}{x_{i - u + 1, j - v + 1}}} \right)} }, $ | (1) |

当前基于GPU的矩阵卷积实现主要有以下几种.

1) 将矩阵的卷积操作转化为矩阵乘法,然后通过使用已有的GPU矩阵乘法的优化算法进行计算,该方法需要将输入卷积矩阵D和卷积核F进行转化,由于该方法将D从四维数组转化为二维矩阵时数据规模变大,会占用较多的显存,且当卷积核越大,移动步长越小,显存的消耗就会越大.

2) 将输入特征图D和卷积核F首先进行FFT变换[19],将数据变换到频域空间,然后将变换之后的结果在频域进行点乘运算,最后将点乘的结果进行FFT逆变换回时域空间,该方法的优点是计算量与卷积核的大小无关,因此针对卷积核尺寸较大的卷积网络,FFT方法相比直接卷积方法在降低计算量方面具有明显的优势,其不足之处就是要付出增加存储开销的代价,因此当前基于FFT的方法并没有得到广泛的应用,主要是因为当前的卷积神经网络模型中采用的卷积核尺寸都比较小,因此FFT方法在降低计算量方面的优势没能得到很好的展现.

3) 基于cuDNN的矩阵卷积算法实现[20-21],cuDNN是NVIDIA公司针对GPU的众核架构高度优化的卷积神经网络加速库,主要针对矩阵卷积进行优化实现,其也是通过将卷积运算转化为矩阵乘法,不同的是转化后的二维输入特征图没有直接存储到显存里面,而是当需要这部分数据的时候,直接到D中索引对应的数据,并加载到GPU的显存里面进行计算,避免了占用额外显存的弊端.

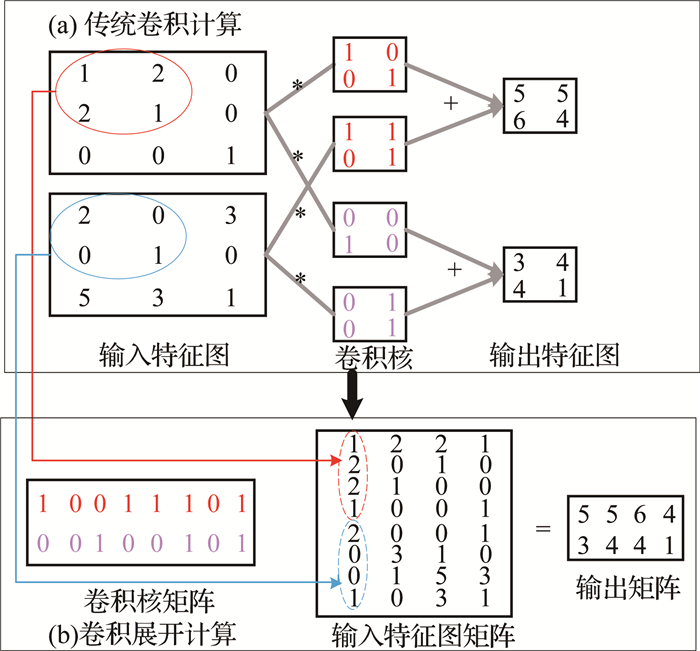

传统的二维矩阵卷积计算过程如图 3(a)所示,文献[19]中用到了另一种计算方法,即将卷积矩阵和卷积核矩阵展开成矩阵块的方式进而通过普通矩阵相乘的方式进行卷积计算,如图 3(b)所示,其计算过程如下.

|

图 3 二维矩阵卷积计算的2种方式 Fig. 3 Two calculation methods for two-dimensional matrix convolution |

1) 根据卷积核规模和移动步长,将对应的卷积矩阵相应的卷积块展开成列向量的形式,所有展开的列向量组成一个新的矩阵.

2) 将单个卷积核矩阵按行展开成一个行向量,所有展开的卷积核组成一个新的卷积核矩阵.

3) 将新的卷积矩阵和新的卷积核矩阵做普通矩阵与矩阵乘法,进而可以通过调用普通的BLAS(basic linear algebra subprograms)[23]函数库中的GEMM(general matrix multiplication)完成二维矩阵卷积的计算.

可以看出,图 3(b)所示的计算方法的优点是将小的卷积计算模块组成大规模的计算单元,可以充分利用大规模矩阵乘法带来的高计算效率.同样,该方法的缺点也非常明显,主要包括:1)在卷积计算前,需要将小规模卷积模块排列成大规模矩阵单元,而这些操作若不能并行执行,将带来不少计算开销. 2)对卷积矩阵进行有重复的展开增加了矩阵的规模,随着卷积矩阵规模的增加,采用这种有重复展开的方式会造成数据规模越来越大,而对嵌入式处理器来说,核内存储最为重要,因此该方法不易于对核内存储敏感的向量处理器来执行.

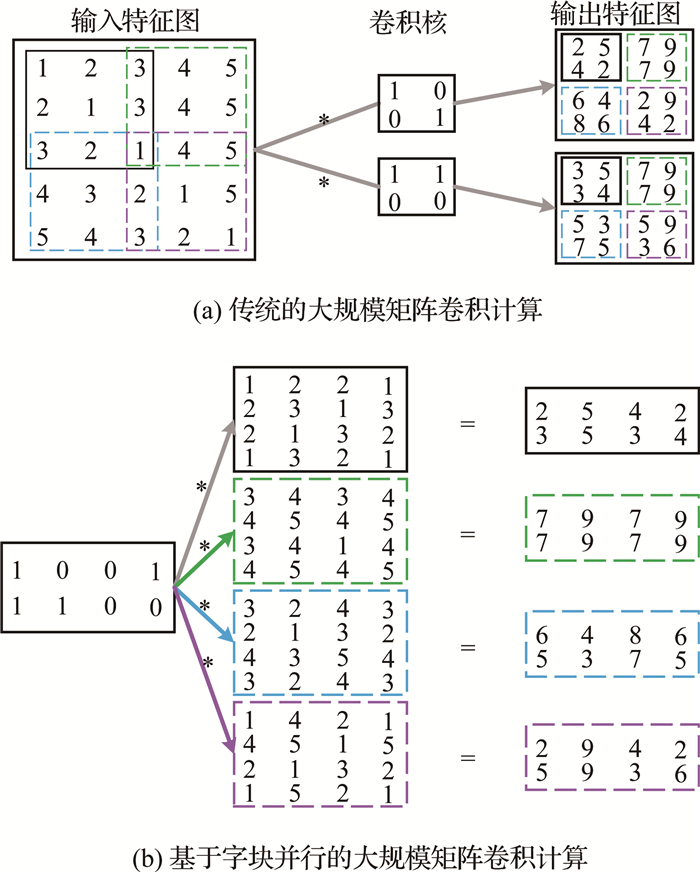

此外,针对大规模二维矩阵卷积,文献[19]提出了一种分块计算的方法,即将大规模的矩阵根据卷积核的尺寸划分成合理的规模,然后对每个划分好的卷积模块采用与图 3(b)类似的方法进行展开,进而可以通过多个卷积模块的并行执行,完成大规模二维卷积矩阵的计算.但该大规模二维矩阵卷积的分块方法,除了大大增加了卷积矩阵的数据存储量,还使得卷积计算的结果顺序上不连续,如图 4(b)所示,由于大部分二维卷积计算的结果需要作为后续操作的初始数据,比如CNN,因此该方法也不利于后续数据的处理.如图 4所示为文献[19]提出的一种针对大规模二维矩阵卷积进行分块计算的方法.

|

图 4 大规模矩阵卷积的子块并行方案 Fig. 4 Subblock parallel scheme for large scale matrix convolution |

FT2000是一款向量处理器,包含768KB的向量存储体AM和96KB的标量存储体SM,AM主要完成向量运算,SM主要完成相应的标量操作,一般来说卷积核矩阵的规模都比较小,当下主流CNN中的卷积核规模一般为3×3、5×5、7×7、11×11.且根据算法的需要,卷积核数据需要标量取,因此将卷积核数据置于SM,卷积矩阵置于AM,其向量化实现过程如下.

3.1 单核程序设计分析(1) 当卷积矩阵规模较小时,即卷积矩阵可以全部置于AM中,以单精度浮点数据为例,单个浮点数据为4 byte,设卷积矩阵为N×N的方阵,则N×N×4=768×1 024,AM中可以放置的最大卷积矩阵的规模为443×443,因此当需要计算的卷积矩阵规模大于443×443时,需要从片外加载数据.

下面以图 5为例说明基于向量处理器的矩阵卷积的实现方法.设卷积矩阵A为5×5,卷积核矩阵为2×2,滑动步长为1,边界扩充操作为0,其卷积结果第一行元素的计算过程如Cycle #0至Cycle #3所示.

|

(A:5×5;步长:1×1;kernel:2×2;pad:0) 图 5 FT2000矩阵卷积的算法映射 Fig. 5 Algorithm mapping of FT2000 matrix convolution |

Cycle #0:所有PEs加载卷积矩阵A的第一行元素(a0, 0,a0, 1,a0, 2,a0, 3和a0, 4),标量处理单元加载卷积核矩阵的第1行第1个元素(k0, 0),通过标向量广播将k0, 0广播至向量寄存器中,即对应的向量寄存器中的元素为k0, 0,k0, 0,k0, 0,k0, 0,k0, 0,通过向量处理器的乘加指令,每一个PE完成对应元素与卷积核k0, 0的乘法,并将乘法结果累加至对应的向量寄存器中.

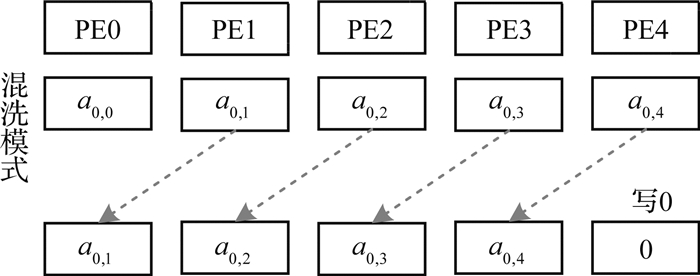

Cycle #1:通过配置特殊的混洗模式(如图 6所示)将Cycle #0中加载的行元素进行移位,完成移位后当前PEs所对应的元素为a0, 1,a0, 2,a0, 3,a0, 4,0,同时标量加载卷积核的第1行第2个素k0, 1,同样通过标向量广播至向量寄存器中,即为k0, 1,k0, 1,k0, 1,k0, 1,k0, 1,通过向量乘加指令,每一个PE完成对应元素与卷积核k0, 1的乘法,并将乘法结果累加至Cycle #0中的累加寄存器中.

|

图 6 FT2000移位的混洗模式 Fig. 6 Shift shuffle mode of FT2000 |

Cycle #2:所有PEs加载卷积矩阵A的第二行元素(a1, 0,a1, 1,a1, 2,a1, 3和a1, 4),标量处理单元加载卷积核矩阵的第2行第1个元素(k1, 0),通过标向量广播将k1, 0广播至向量寄存器中,即对应向量寄存器中的元素为k1, 0,k1, 0,k1, 0,k1, 0,k1, 0,通过向量处理器的乘加指令,每一个PE完成对应元素与卷积核k1, 0的乘法操作,并将乘法结果累加至Cycle #1中的累加寄存器中.

Cycle #3:采用Cycle #1中的混洗模式,将Cycle #2中取到的元素进行移位,完成移位后当前PEs所对应的元素为a1, 1,a1, 2,a1, 3,a1, 4,0,同时标量加载卷积核矩阵第2行第2个元素并广播至向量寄存器中,即为k1, 1,k1, 1,k1, 1,k1, 1,k1, 1,通过向量处理器的乘加指令,每一个PE完成对应元素与对应卷积核k1, 1的乘法操作,并将乘法结果累加至Cycle #2中的累加寄存器中.Cycle #3累加寄存器中的值即为卷积结果矩阵第一行的结果元素.

通过以上计算过程可以发现,采用本文提出的方法有以下几个优点:1)在进行卷积计算前不需要额外的开销将卷积矩阵进行展开;2)大幅减少了矩阵展开所带来的存储开销;3)可以充分复用已取到的数据,减少数据的访存量,进而节约计算时间,因为取数据比数据的计算要花费更多的节拍;4)通过流水线技术,理想情况下每拍可以同时计算结果矩阵的一行元素;5)不仅不需要将卷积矩阵进行展开,也避免了中科院计算所陈云霁等[15]提出的PEs阵列间数据的水平方向或垂直方向频繁的数据移动.

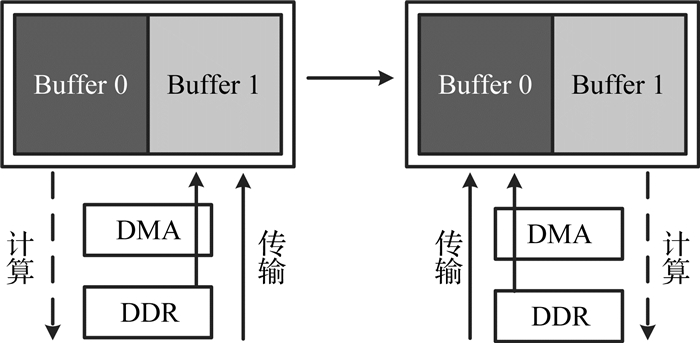

(2) 当卷积矩阵规模较大时,即N×N×4>768×1024时,卷积矩阵A的规模大于443×443时,由于AM一次不能加载整个卷积矩阵,为了提高卷积计算的速度,采用双Buffer机制,用“ping-pong”的方式进行数据传输,此时AM空间按地址划分为相等的两部分,分别为Buffer0和Buffer1,数据从DDR中通过DMA传输到核内AM中,假设从Buffer0开始计算,Buffer0计算的同时,Buffer1进行数据传输,当Buffer1开始计算时,Buffer0输出上一次的计算结果并启动新数据传输,采用双Buffer的机制可以将计算时间和传输时间重叠起来,提高算法的执行效率.如图 7所示为本文采用的双Buffer机制示意图.当处理大规模矩阵卷积时在采用双Buffer机制的同时,内核还是采用(1)中的向量化实现方法来处理.

|

图 7 FT2000双Buffer机制示意 Fig. 7 Double Buffer mechanism of FT2000 |

由于FT2000是一款12核高性能向量处理器,采用多核并行的技术实现高效的算法加速也是一个重要的研究内容.但是多核程序的设计与单核程序不同,需要考虑多方面的因素,比如如何进行多核的任务划分、算法是否有很强的相关性、多核的通信开销如何等等.考虑到二维矩阵卷积主要用于图像处理尤其是卷积神经网络中卷积层的计算,且卷积层的计算规模从5×5到1 000×1 000都存在,大部分都是卷积核规模较小的矩阵卷积计算,因此针对矩阵卷积的多核并行一般不会将单个卷积的计算分配给多核来完成,而是N个独立的卷积计算过程由N个核并行执行来完成卷积计算的多核并行.

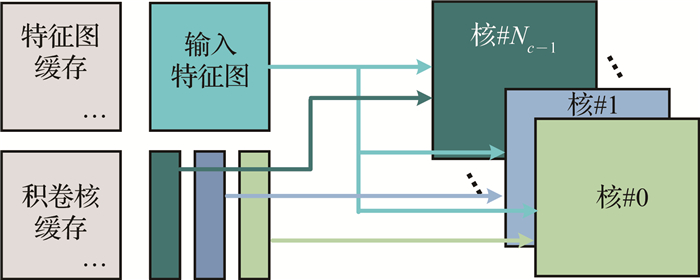

如图 8所示为FT2000的多核实现方案,从DDR中获得一幅输入特征图像,并广播至所有Nc个核共有,同时每个核单独加载自己的卷积核矩阵至标量存储体SM中,则多核程序中每个核的计算过程同3.1单核程序的计算一样.

|

图 8 矩阵卷积多核实现方案 Fig. 8 Multi-core implementation of matrix convolution |

本实验的对比平台有服务器级CPU-Intel(R) Xeon(R) CPU E5-2650,32核,64 GB内存,主频为2.6 GHZ,软件平台使用Linux CentOS6.2操作系统、使用C语言实现不同规模的矩阵卷积,基于GCC4.8.2编译器并使用最高级别优化(-O3)优化所有代码程序,测试时间由clock()函数进行统计;使用TI的高性能多核数字信号处理器TMS320C6678,8核,1.25 GHZ主频,每个核拥有32 KB的L1P和32 KB的L1D,并基于CCS5.5软件编程平台完成所有程序代码的测试与性能统计;飞腾平台使用类CCS的FT2000软件编程平台并完成FT2000向量程序代码的编写与性能统计.

4.2 算法加速比通过2.2节的分析可知,二维矩阵卷积是典型的计算密集型和访存密集型算法,而当前的CNN网络模型中矩阵卷积的计算又占据着整个模型计算量的85%以上,因此本实验选取2种计算模型进行分析.第一种,卷积矩阵不变,卷积核矩阵规模相应增加,记为模式1;第二种,卷积核矩阵不变,卷积矩阵规模相应增加,记为模式2.(本实验中所有数据采用双精度浮点,且都为方阵,即48×3表示48×48与3×3的卷积操作).

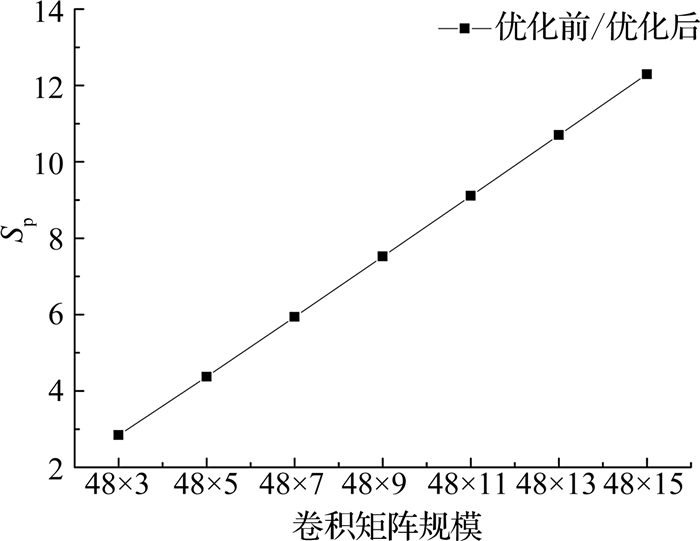

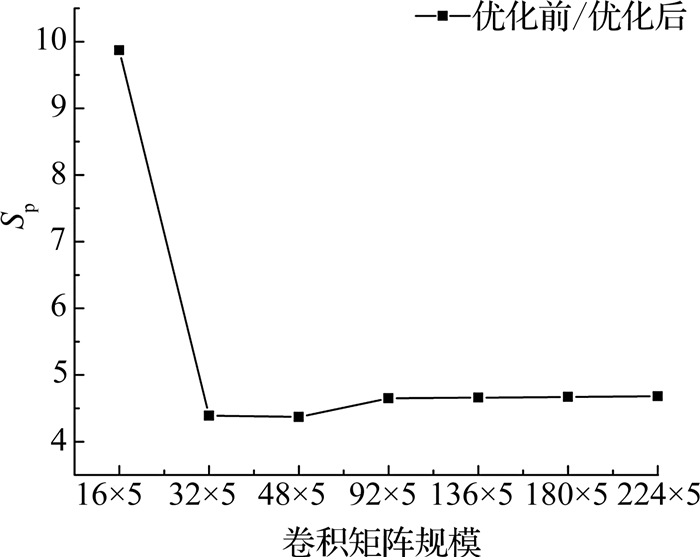

如图 9所示为基于卷积核规模变化的FT2000优化前与优化后的加速比折线图,SP为加速比.从图中可以看出,当卷积矩阵规模一定时,矩阵卷积计算的优化加速比随着卷积核规模的增加基本呈线性增加趋势.如图 10所示为基于卷积矩阵规模变化的FT2000优化前与优化后的加速比折线图.可以看出,当卷积核规模一定时,算法加速比随着卷积矩阵规模的增加先降低,后趋于稳定.

|

图 9 基于卷积核规模变化的FT2000优化加速比 Fig. 9 Optimized speed-up ratio of FT2000 with change of convolution kernel scale |

|

图 10 基于卷积矩阵变化的FT2000优化加速比 Fig. 10 Optimized speed-up ratio of FT2000 with change of matrix scale |

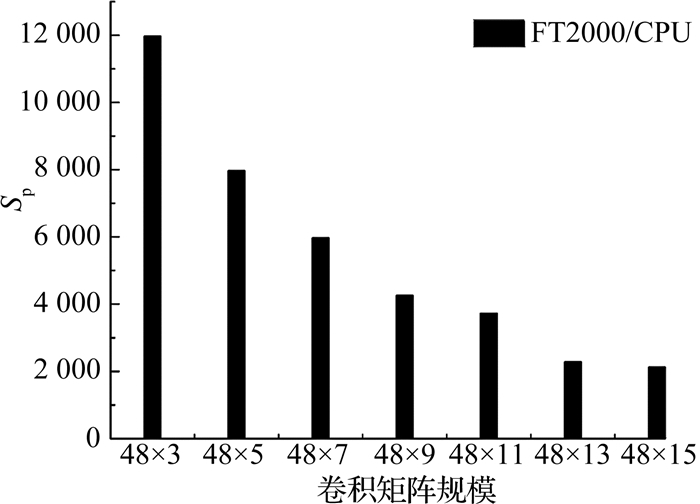

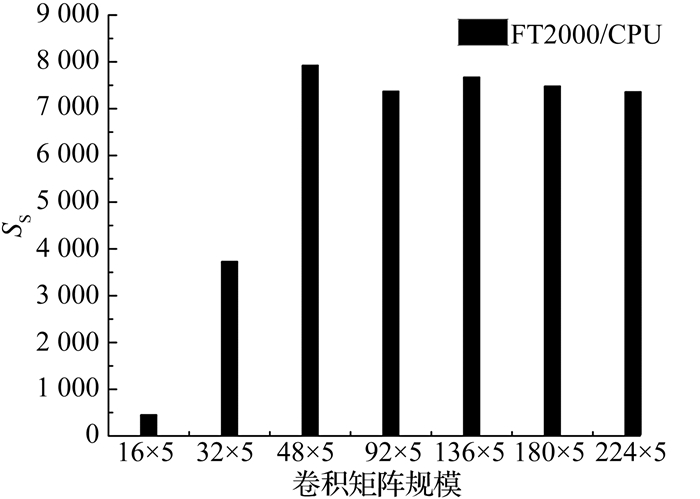

图 11统计了随着卷积核规模的变化,FT2000基于CPU的加速比,可以看出FT2000向量处理器相对于服务器级多核CPU取得了2132~11974倍不等的加速比.图 12为卷积核规模不变,随着卷积矩阵规模变化的FT2000基于CPU的加速比,同样取得了456~7925倍不等的加速比.这说明对于计算密集型的二维矩阵卷积FT2000向量处理器比多核CPU并行系统能够获得更好的性能.

|

图 11 基于卷积核规模变化的FT2000/CPU的加速比 Fig. 11 Speed-up ratio of FT2000/CPU with change of convolution kernel scale |

|

图 12 基于卷积矩阵变化的FT2000/CPU的加速比 Fig. 12 Speed-up ratio of FT2000/CPU with change of matrix scale |

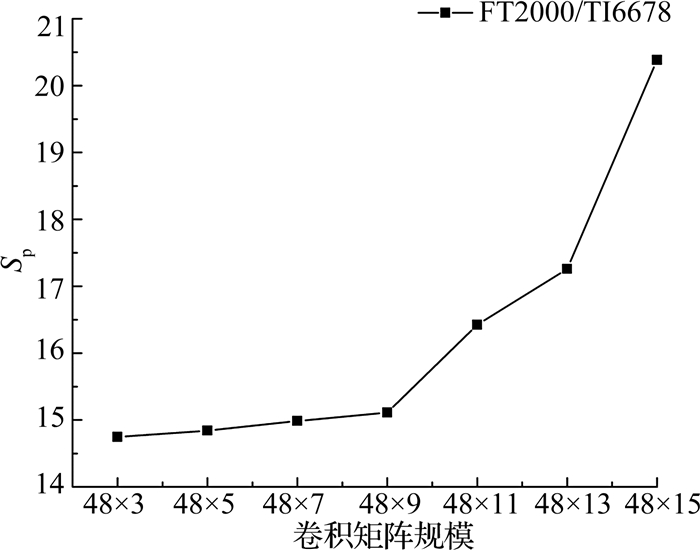

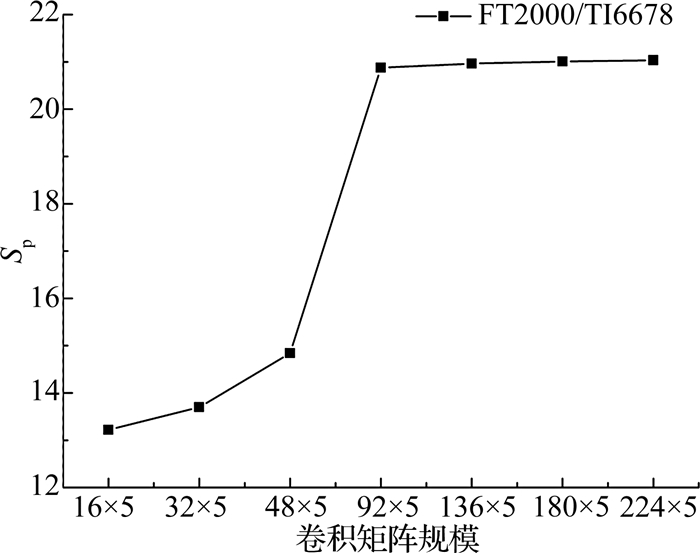

图 13、图 14针对2种计算模式,分别对比分析了FT2000平台基于TI6678取得的性能加速比情况.在图 13中,FT2000基于TI6678的加速比随着模式1计算规模的增加所取得的优势愈发明显,而图 14中,当模式2的计算规模增加到一定程度,其相对TI6678的加速比基本维持在20倍左右.可见,此2种计算模式,对程序的性能优化影响十分明显.

|

图 13 基于卷积核规模变化的FT2000/TI6678的加速比 Fig. 13 Optimized speed-up ratio of FT2000/ TI6678 with change of convolutional kernel scale |

|

图 14 基于卷积矩阵变化的FT2000/TI6678的加速比 Fig. 14 Optimized speed-up ratio of FT2000/ TI6678 with change of matrix scale |

图 9、图 10显示了2种不同的计算模式对算法优化加速比的影响,当卷积核规模增加时,加速比基本成线性增加,而当卷积矩阵规模增加时,加速比有所下降,并最终保持稳定,且加速比并不高,这主要是因为在该算法实现过程中,内核程序主要是通过卷积核的规模来控制循环大小,即当卷积核规模较小时,程序的最内层循环较小,无法通过软件流水的方式高度优化矩阵卷积计算,进而难以发挥向量处理器的计算优势,而图 9中之所以取得线性加速比,主要是因为卷积核的规模增加,进而核心循环可以通过软件流水等方式对实现代码进行高度优化,因此,卷积核的规模是影响本文算法实现性能的一个主要影响因素.

图 11中,随着卷积核计算规模的增加FT2000并没有取得线性的加速比,且有所下降,可能原因是随着矩阵计算规模的增加,CPU的多核及多线程发挥了作用,提高了卷积的计算效率.图 12中的加速比相对稳定,主要原因是卷积核规模较小,只有卷积矩阵规模的增加并不能充分发挥FT2000向量处理器的作用.而图 13中的计算模式1之所以能够取得较好的加速比,主要是因为FT2000算法优化中卷积核规模决定着内层循环的大小,内层循环越大,通过循环展开所取得的性能优势就愈发明显.图 14中之所以没有取得较好的加速比,其瓶颈仍在于卷积核规模过小,使得FT2000向量处理器没有完全发挥其性能优势.针对该计算瓶颈,下一步可考虑能否在不增加卷积矩阵规模的前提下,通过融合多个卷积核矩阵来提高FT2000向量处理器计算矩阵卷积的计算效率.

5 结语本文在对矩阵卷积计算深入分析的基础上,结合FT2000多核向量处理器的体系结构特点提出了一种减少访存、充分复用已取数据的二维矩阵卷积并行计算方法,并基于多核CPU和TI6678进行了性能对比和分析,取得了良好的加速比,实验结果显示:FT2000比CPU及TI6678具有更好的计算优势,相比CPU最高可加速11 974倍,相比TI6678可加速21倍.本文研究显示,二维矩阵卷积可在FT2000向量处理器上取得良好的性能,切实加速了矩阵卷积的计算过程,为今后国产FT2000高性能多核向量处理器用于卷积神经网络模型的移植作准备.

| [1] |

DENG L, YU D. Deep learning:methods and applications[J]. Foundations & Trends© in Signal Processing, 2014, 7(3): 197-387. |

| [2] |

WU M, CHEN L. Image recognition based on deep learning[C]//Chinese Automation Congress. Wuhan: IEEE, 2015. http://ieeexplore.ieee.org/document/7382560/

|

| [3] |

LI D, LI J Y, HUANG J T, et al. Recent advances in deep learning for speech research at Microsoft[C]//In the Proceedings of the 2013 IEEE International Conference on Acoustics, Speech and Signal Processing. Vancouver: IEEE, 2013: 8604-8608. http://ieeexplore.ieee.org/document/6639345/

|

| [4] |

KAVUKCUOGLU K, BOUREAU Y L, BOUREAU Y L, et al. Learning convolutional feature hierarchies for visual recognition[C]//International Conference on Neural Information Processing Systems. Vancouver: Curran Associates Inc. 2010: 1090-1098. http://dl.acm.org/citation.cfm?id=2997311

|

| [5] |

CHEN Z, WANG J, HE H, et al. A fast deep learning system using GPU[C]//Proceedings of International Symposium on Circuits and Systems. Melbourne: IEEE, 2014: 1552-1555. http://ieeexplore.ieee.org/document/6865444/

|

| [6] |

BOURLARD H, KAMP Y. Auto-association by multilayer-perceptrons and singular value decomposition[J]. Biological Cybernetics, 1988, 59(4/5): 291-294. |

| [7] |

YAJIE MIAO, MOHAMMAD GOWAYYED, AND FLORI-AN METZE. EESEN: End-to-end speech recognition using deep RNN models and WFST-based decoding[C]//Automatic Speech Recognition and Understanding. Scottsdale: IEEE, 2015: 167-174. http://arxiv.org/abs/1507.08240

|

| [8] |

LIU S, DU Z, TAO J, et al. Cambricon:an instruction-set architecture for neural networks[J]. ACM Sigarch Co-mputer Architecture News, 2016, 44(3): 393-405. DOI:10.1145/3007787 |

| [9] |

NASSE F, THURAU C, FINK G A. Face detection using GPU-based convolutional neural networks[C]//International Conference on Computer Analysis of Images and Patterns. Berlin Heidelberg: Springer, 2009: 83-90. http://www.springerlink.com/content/h00np133u6602613

|

| [10] |

POTLURI S, FASIH A, VUTUKURU L K, et al. CNN-based high performance computing for real time image-processing on GPU[C]//The Workshop on Nonlinear Dynamics & Synchronization & Int'l Symposium on Theoretical Electrical Engineering. Klagenfurt: IEEE, 2011: 1-7. http://link.springer.com/content/pdf/10.1007/978-3-642-24806-1_20.pdf

|

| [11] |

YU Q, WANG C, MA X, et al. A deep learning predic-tion process accelerator based FPGA[J]. Proceedings of the Annual ACM Symposium on Theory of Computing, 2015, 585-594. |

| [12] |

HEGDE G, SIDDHARTHA, RAMASAMY N, et al. Evaluating embedded FPGA accelerators for deep learning applications[C]//IEEE, International Symposium on Field Programmable Custom Computing Machines. Washington DC. : IEEE, 2016: 25. http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=7544737

|

| [13] |

CHEN T, DU Z, SUN N, et al. DianNao:a small-footprint high throughput accelerator for ubiquitous machine learning[J]. ACM Sigarch Computer Architecture News, 2014, 49(4): 269-284. |

| [14] |

LIU D, CHEN T, LIU S, et al. PuDianNao: a polyvalent machine learning accelerator[C]//Twentieth International Conference on Architectural Support for Programming Languages and Operating Systems. Istanbul: ACM, 2015: 369-381. http://dl.acm.org/citation.cfm?id=2694358

|

| [15] |

DU Z. ShiDianNao: shifting vision processing closer to the sensor[C]//ISCA'15 Proceedings of the, International Symposium on Computer Architecture. Portland: ISCA, 2015: 92-104. http://dl.acm.org/citation.cfm?id=2750389

|

| [16] |

刘仲, 田希, 陈磊. 支持原位计算的高效三角矩阵乘法向量化方法[J]. 国防科技大学学报, 2014, 6(36): 7-11. LIU Zhong, TIAN Xi, CHEN Lei. Efficient vectorization method of triangular matrix multiplication supporting in-place calculation[J]. Journal of National University of Defense Technology, 2014, 6(36): 7-11. |

| [17] |

刘仲, 陈跃跃, 陈海燕. 支持任意系数长度和数据类型的FIR滤波器向量化方法[J]. 电子学报, 2013, 2(41): 346-351. LIU Zhong, CHEN Yue-yue, CHEN Hai-yan. A vectorization of fir filter supporting arbitrary coefficients length and data types[J]. Acta Electronica Sinica, 2013, 2(41): 346-351. |

| [18] |

周海芳, 高畅, 方民权. 基于CUBLAS和CUDA的MNF并行算法设计与优化[J]. 湖南大学学报:自科版, 2017, 4(44): 147-156. ZHOU Hai-fang, GAO Chang, FANG Min-quan. Parallel algorithm design and performance optimization of maximum noise fraction rotation based on CUBLAS and CUDA[J]. Journal of Hunan University:Natural Sciences, 2017, 4(44): 147-156. |

| [19] |

LAVIN A, GRAY S. Fast algorithms for convolutional neural networks[J]. Computer Science, 2015, 4013-4021. |

| [20] |

ZAGORUYKO S, KOMODAKIS N. Learning to compare image patches via convolutional neural networks[C]//Computer Vision and Pattern Recognition. Boston: IEEE, 2015: 4353-4361. http://doi.ieeecomputersociety.org/10.1109/CVPR.2015.7299064

|

| [21] |

POTLURI S, FASIH A, VUTUKURU L K, et al. CNN based high performance computing for real time image processing on GPU[C]//Nonlinear Dynamics and Synchronization. Klagenfurt. : IEEE, 2011: 1-7. http://link.springer.com/content/pdf/10.1007/978-3-642-24806-1_20.pdf

|

| [22] |

CHELLAPILLA K, PURI S, SIMARD P. High performance convolutional neural networks for document processing[C]//Tenth International Workshop on Frontiers in Handwriting Recognition, La Baule: Suvisoft, 2006: inria-00112631. http://www.mendeley.com/catalog/high-performance-convolutional-neural-networks-document-processing/

|

| [23] |

DONGARRA J J. An extended set of FORTRAN basic linear algebra subprograms[J]. ACM Transactions on Mathematical Software, 1988, 14(1): 18-32. DOI:10.1145/42288.42292 |