密钥管理包括密钥的产生、装入、分配、存储、更新、吊销和销毁等内容.物理不可克隆函数(physical unclonable functions,PUFs)作为一种新兴的信息安全机制,为低成本密钥生成和存储机制提供了可能性.物理不可克隆函数从集成电路的物理特征中提取密钥,不需要存储器这样昂贵的硬件,由于制造过程中的差异不可控制,每一个器件的物理特性都不会被克隆或者复制,因此密钥生成不可预测,具有唯一性.与PUFs相比,传统的密钥存储方案大都基于非易失性寄存器(non-volatile memory,NVM),例如EEPROM、Flash等.EEPROM、Flash等存储机制的实现需要在传统CMOS工艺中加入浮栅晶体管.除此之外,基于NVM的密钥存储易受到物理攻击[1-2],需要加入价格较高的防护层或检测传感器确保安全性,这对成本要求较高的嵌入式设备提出了巨大挑战.在低成本设备中,如何确保密钥的完整性和安全性成为研究重点.

静态随机存取存储器(static random access memory, SRAM)单元上电后,初始值有2个稳定的状态:0或1,这种状态难以预测且不可复制,可以作为PUFs使用.受环境噪声和老化的影响,每次上电时SRAM PUFs的输出不稳定.为了得到稳定且高熵的密钥,使用辅助数据算法对SRAM上电初始值进行纠错及熵值压缩.使用SRAM PUFs有以下优点:1)SRAM在许多设计中是标准件,已应用到诸多系统中,设计者无需增加额外的硬件;2)SRAM有大量的空间,足以生成固定长度且高熵的密钥;3)SRAM上电时生成密钥,断电时密钥消失,保证了密钥的安全.

PUFs主要有以下2种实现方法:1)利用数字信号的传播延时,比如仲裁器PUFs[3]和环形振荡器PUFs[4];2)利用存储器单元结构的稳定性,比如SRAM PUFs[5-6]、Flash PUFs[7]和蝶形PUFs[8].SRAM PUFs由Guajardo等[5-6]提出,分别用于密钥生成、认证和随机数生成.辅助数据算法最早被称为模糊提取(fuzzy extractor)[9],用于从噪声数据中提取密钥.目前,SRAM PUFs的研究包括PUFs特性的基础研究,比如测量稳定性和唯一性[10];算法研究,比如使用软判决算法来提高算法效率,减少资源消耗[11-12];安全应用,比如为ARM TrustZone提供根信任[13].存在的问题如下:SRAM PUFs可靠性测量的目标是整块SRAM PUFs响应,相应的纠错算法根据整块SRAM PUFs响应的错误率而定;在密钥生成的过程中,使用的数据为SRAM PUFs响应的一部分,这就假定SRAM上电初始值中的错误均匀分布.对于密钥生成而言,在密钥生成过程中不能出现任何错误,否则会影响后续的加密解密操作,因此需要对SRAM PUFs响应错误率的空间分布进行分析研究,保证密钥生成的可靠性.

本文对多块SRAM芯片的内部错误分布进行统计分析,提出使用地址块选择算法和参数化辅助数据算法来处理错误分布不均的情况,对相关结论开展实验仿真.

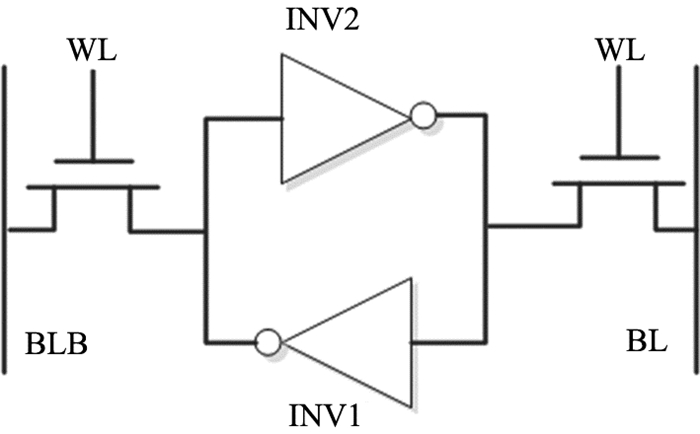

1 SRAM PUFs密钥生成结构 1.1 SRAM单元结构一个典型的SRAM单元包括6个晶体管,其中4个晶体管组成对称且交叉耦合的反相器,如图 1所示.该对称电路上电的先后顺序决定了SRAM单元的稳定状态,由于制造过程中的不可控因素,比如掺杂浓度的均匀性、晶体管沟道长宽比等,会造成SRAM单元之间的差异,这使得SRAM单元上电后的初始状态会偏0或者偏1,且不可预测.

|

图 1 SRAM单元的基本结构 Fig. 1 Fundamental structure of SRAM cell |

在理想状态下,如果只考虑SRAM单元内部制造的差异,那么SRAM PUFs的输出是稳定且唯一的;在外界环境影响下,比如电压偏差、工作的温度以及老化影响等等,部分SRAM单元的上电初始值会发生变化,因此将SRAM单元分为稳定偏置单元和不稳定偏置单元.稳定偏置单元是指交叉耦合的反相器高度不匹配,上电时SRAM单元偏0或者偏1.不稳定偏置单元是指交叉耦合反相器之间比较匹配,SRAM单元受外界环境的影响大,上电后不能确定SRAM单元状态.

1.2 辅助数据算法如表 1所示,SRAM PUFs用于密钥生成时分为以下2个过程.1)注册过程.在可信环境下,读取SRAM上电后的响应r,然后利用辅助数据算法生成辅助数据p和密钥k,辅助数据存储在器件的非易失性存储器中.辅助数据可以公开存储,不会揭露关于PUFs响应或者密钥的信息.2)重构过程.SRAM上电后,读取噪声响应r′,利用非易失性存储器中的辅助数据p以及SRAM上电产生的PUFs噪声响应r′生成码字c′,经过辅助数据算法的纠错模块后生成码字c;码字c利用辅助数据恢复原PUFs响应r,进而生成密钥k.如果此次测量的PUFs噪声响应r′和注册阶段测量的PUFs响应r接近,那么密钥会完整地恢复.

| 表 1 密钥生成过程 Table 1 Key generation process procedure |

辅助数据算法由模糊提取发展而来,用于解决以下2个问题.1)受噪声的影响,PUFs响应会发生错误;2)由于PUFs数据的相关性和算法本身的泄露,PUFs响应的熵并非最大.为了解决这两个问题,辅助数据算法包括纠错和熵值压缩两个部分.纠错模块使用辅助数据来纠正PUFs响应中的错误,在注册过程中使用纠错编码生成相关码字,在重构过程中使用纠错译码恢复码字;熵值压缩称为保密增强,用来增加密钥的熵,同时使密钥均匀分布.

辅助数据算法的核心是纠错,在SRAM PUFs的密钥生成过程中,使用BCH码对PUFs响应进行纠错.BCH码是纠正多个随机错误的线性循环分组码,纠错能力强,特别是中短码的性能接近理论值.BCH码包括3个参数:码长n、信息位k、纠错个数t;当码字长度一定时,k随着t而变化.二进制BCH中短码的纠错能力如表 2所示,可以看出,中短码下BCH码的最大纠错个数比例为20%~25%,SRAM PUFs的平均错误率一般小于15%,如果SRAM PUFs响应中错误均匀分布,那么使用BCH码进行纠错没有问题.此外,随着t的增加,BCH码译码结构的复杂度会持续增加,硬件资源的消耗也会大幅增加.

| 表 2 BCH中短码纠错能力 Table 2 Error-correcting capability of some BCH codes |

为了得到高可靠性和高熵值的密钥,使用可靠性和不可预测性来对SRAM PUFs的特性进行测量.

可靠性是指对于给定的器件,每次测量的PUFs响应与注册阶段测量的响应相似,在噪声影响下,PUFs电路能够正常工作.当同一个器件多次测量PUFs响应时,受噪声影响会出现一定范围的错误,因此PUFs的可靠性用错误率(bit error rate, BER)来量化,定义如下:

| $ {\rm{BER = HD}}\left( {y\prime ,y} \right){\rm{}}/n. $ | (1) |

式中:y′和y表示上电后的SRAM PUFs响应,n为响应的长度,HD为汉明距离(Hamming distance).

最大错误率用来统计SRAM PUFs响应中所有发生过错误的地址,定义如下:

| $ {\rm{BE}}{{\rm{R}}_{{\rm{max}}}} = {\rm{set }}\left( {{\rm{Addr}}\left( {y\prime, y} \right)} \right){\rm{}}/n. $ | (2) |

式中:Addr()指PUFs响应中错误发生的地址;set()指该集合内的地址不重复,即发生过错误的地址只统计一次,这样可以得到所有发生过错误的地址,从而得到一个最大错误率BERmax.

不可预测性指PUFs响应随机且不可预测,有足够的熵.对于SRAM单元来说,熵越小,表明该SRAM单元的稳定性越好,即该SRAM单元每次上电的初始值不变;熵越大,表明该SRAM单元的随机性越好,即该SRAM单元每次上电的初始值不确定.不可预测性用最小熵来测量,一个二进制源的输出为0或1,如果输出0的概率是p0,输出1的概率是p1,pmax是这两个概率中的最大值,那么最小熵的定义为

| $ {{\mathit{H}}_{{\rm{min}}}}{\rm{ = - lo}}{{\rm{g}}_{\rm{2}}}{\rm{}}\left( {{p_{{\rm{max}}}}} \right). $ | (3) |

假设SRAM的n个单元独立分布,可以得到总熵,定义为

| $ {\left( {{{\mathit{H}}_{{\rm{min}}}}} \right)_{{\rm{total}}}} = \sum\limits_{i = 1}^n {[-{\rm{lo}}{{\rm{g}}_{\rm{2}}}({p_{i{\rm{max}}}})].} $ | (4) |

选取WS62256LLPG-70和HY62256A LP-70两种SRAM芯片作为实验对象,由于篇幅限制,从2种芯片中各选取5片的测试结果进行说明.两种芯片容量都为256 kb,每块芯片测试次数为1 000次,测试温度为恒温25 ℃.为了消除SRAM单元存留电荷的影响,两次测试间设置15 min掉电时间.上位机软件采用C语言和MATLAB语言,运行环境为Window 7操作系统.

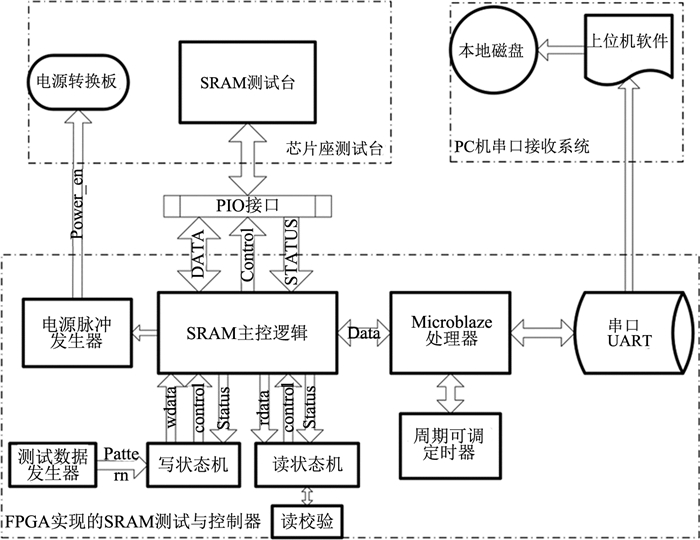

SRAM PUFs测试平台的搭建旨在探究SRAM PUFs的输出特性.SRAM PUFs测试平台的基本功能包括:SRAM PUFs的写入与读取测试、SRAM PUFs可控的间歇性供电以消除残留电荷的影响、间歇性供电时间的自主设定、读取次数的设定、测试数据通过SecureCRT软件写入PC端指定文件中.对于数据的处理,基本功能包括:SRAM PUFs输出序列中随机节点振荡次数的统计以及根据振荡次数划分的选择性输出.该FPGA平台的模块框图如图 2所示,该平台主要包括:SRAM PUFs芯片测试台,针对62 256 DIP SRAM;电源转换板,主要由三极管和电阻组成,完成对SRAM测试台可控制地间歇性供电;SRAM主控逻辑,用于完成对SRAM芯片的读写和供电;电源脉冲发生器,用于产生SRAM间歇性供电的使能信号;PIO接口,用于连接SRAM芯片的数据线、控制线以及地址线;测试数据发生器,结合写状态机可以完成SRAM芯片的任意写入测试;读校验与读状态机可以完成SRAM芯片的读取信息检测;Microblaze处理器,内部运行根据用户指令进行读写控制、序列数据处理与统计的C程序;周期可调定时器,根据用户指令完成计数;UART串口,完成与计算机的数据和指令传输;上位机软件,用于显示操作窗口和用户命令的输入.

|

图 2 SRAM PUFs测试平台 Fig. 2 SRAM PUFs test platform |

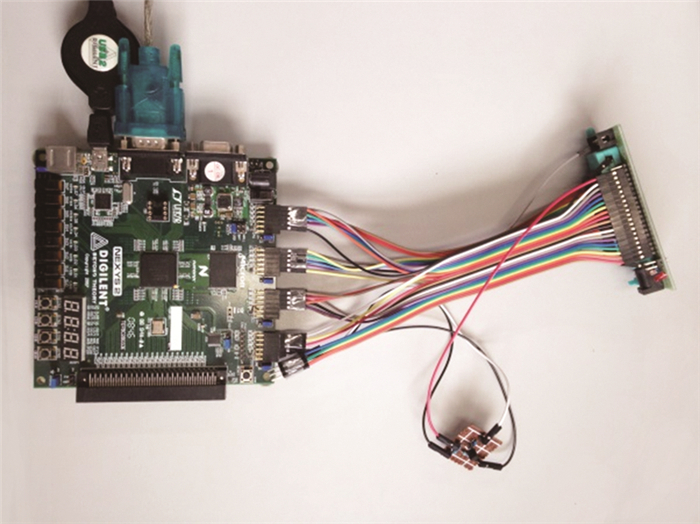

根据用户端上位机设置的测试次数与电脉冲时间间隔,对SRAM PUFs的节点特性进行测试,并将测试结果写入计算机指定的txt文件中.首先,用户通过键盘输入测试次数及电源脉冲时间间隔.测试次数越多,对于数据的分析结果越精确,本文将测试次数设定为1 000次.电源脉冲的时间间隔决定了对SRAM测试台的掉电时间,为了减小残留电荷对SRAM PUFs上电状态的影响,将时间间隔设定为15 min.上位机软件根据以上输入内容完成对Microblaze软核的功能指定,软核开始运行SRAM PUFs写测试功能.之后软核告知周期可调定时器计时周期并开始计时,计时结果将同步显示在FPGA板的数码管上.同时,启动SRAM主控逻辑.此时,主控逻辑不是立刻打开读状态机,而是检测周期可调定时器的计时情况.当完成一次指定计时时间后,SRAM主控逻辑打开读状态机.同时,电源脉冲发生器接收到定时器的信号,通过PIO接口使能电源转换板,电源转换板开始对SRAM测试台持续供电.读状态机将SRAM PUFs数据完整地读出并传送至软核.软核将数据整理为16进制数,通过Uart串口输出至上位机.上文所述的FPGA测试平台实物图如图 3所示.

|

图 3 SRAM PUFs测试平台实物图 Fig. 3 SRAM PUFs test platform in hardware |

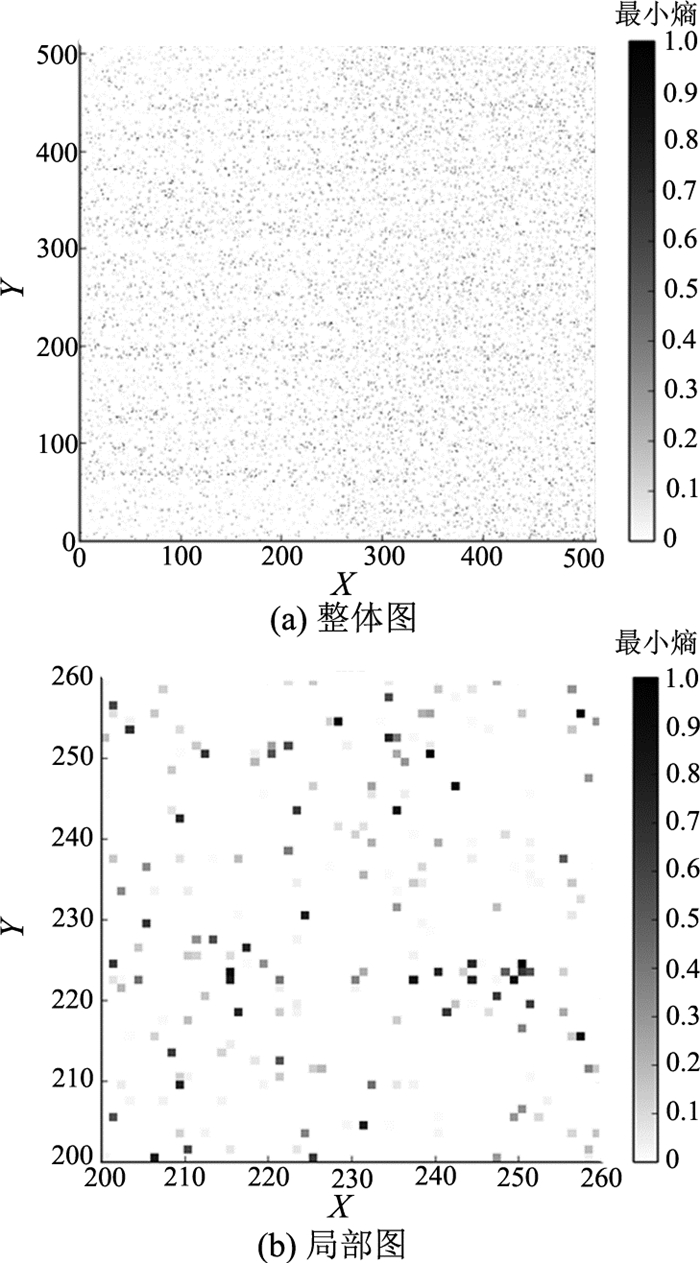

将SRAM PUFs响应排列成512×512的阵列,每一个SRAM单元用颜色的深浅来表示该单元的最小熵,白色表示该SRAM单元的最小熵为0,没有发生错误,即该单元在1 000次统计中一直为1或者0;黑色表示该SRAM单元的最小熵为1,即该单元不稳定,在1 000次统计中出现了500次0和500次1.HY1的最小熵统计结果如图 4所示.图中,X、Y为SRAM单元排列的个数.

|

图 4 HY1 1 000次SRAM上电初始值的最小熵统计结果 Fig. 4 Minimum entropy results of HY1 power-up values in 1 000 times |

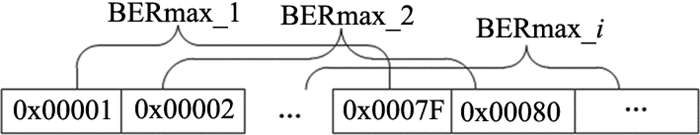

总体来看,发生错误的地址随机分布在SRAM PUFs响应中.为了能够准确地观察SRAM PUFs内部的错误分布,分别设定统计长度L为127、255和511,以SRAM首地址开始遍历整个SRAM PUFs响应,对指定长度L中的最大错误率进行统计,得到各芯片的内部错误率分布.L的长度与BCH码的部分码长一致,为后面的密钥生成提供参考,当L为127时,遍历方法如图 5所示.

|

图 5 L为127时遍历SRAM PUFs响应的方法 Fig. 5 Method of traverse SRAM PUFs response when L is 127 |

对SRAM PUFs内部的最大错误率进行统计分析,如图 6所示.1)在不同的L下,同一片芯片的错误分布相似;在同一统计长度L下,不同的芯片发生的错误分布差异明显.2) L内发生的最大错误在一定范围内,即使有些芯片出现连续地址的错误,但是比例很低,发生的概率极低.3)错误出现的地址非均匀分布在SRAM PUFs响应中,比如当L为127时,芯片WS1最大错误个位最小为0,最大为20.利用SRAM PUFs内部错误分布不均这个特点,可以将错误率低的SRAM PUFs数据块提取出来.

|

图 6 不同统计长度下各SRAM芯片的内部最大错误分布 Fig. 6 Internal error distribution of SRAM chips in different statistical length |

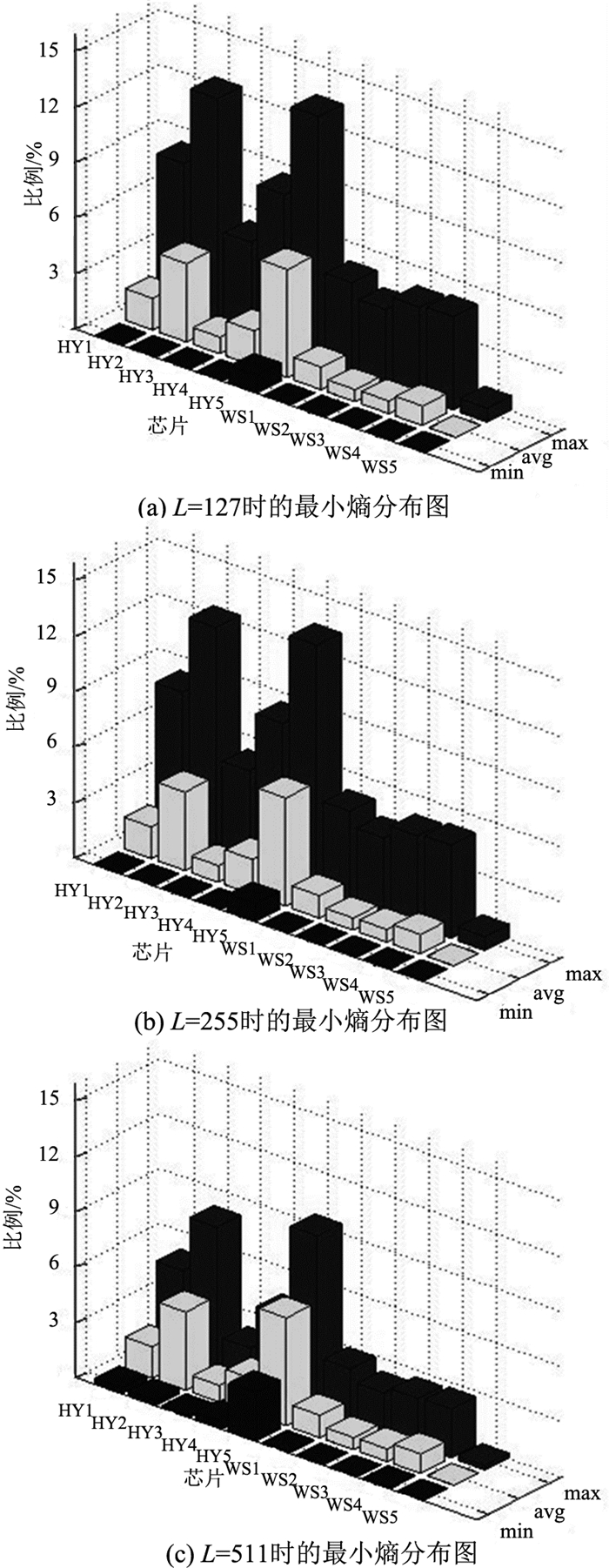

分别设定L为127、255和511,根据L遍历整个SRAM PUFs响应,对指定长度L中的最小熵进行统计,得到各芯片内部的最小熵(Hmin)L分布.不同L下各个芯片总熵的最小值、平均值和最大值如图 7所示.可知,最小熵在SRAM PUFs内部非均匀分布,比如当统计长度为127时,总熵的最小值为0,最大值所占比例为13.3%.此外,不同芯片之间的非均匀分布情况差异明显,各个芯片在不同L下的总熵比例的最大值不超过15%.

|

图 7 不同统计长度下各SRAM芯片的最小熵分布 Fig. 7 Min entropy distribution of SRAM chips in different statistical length |

从最大错误率BERmax和最小熵(Hmin)L的统计分布可以看出,SRAM PUFs中的错误非均匀分布.当使用纠错模块对SRAM PUFs进行纠错时,不能只看整块SRAM PUFs产生的平均错误率,还必须考虑密钥生成过程中使用的部分SRAM PUFs数据产生的错误率;否则错误率有可能大于平均错误率,无法生成正确的密钥.

3 新的密钥生成方法及实验结果 3.1 地址块选择算法由于SRAM PUFs内部错误分布不均,把错误率少的地址块从整个SRAM PUFs响应中提取出来,作为密钥生成的源PUFs数据,该过程称为地址块选择算法.首先确定统计开始的地址Add,并以Add为首地址统计长度L内的最大错误率,按照该方式遍历整个SRAM PUFs响应,得到m个数据对(Add, BERmax),其中m=n-L+1.根据设定的错误率BERinput,对m个数据对进行提取,使得到的BERmax < BERinput;然后记录保存各地址块的首地址,具体算法的过程如下.

算法1.地址块选择算法:利用SRAM PUFs内部错误分布不均,提取错误率低的地址块的首地址.

参数:

Addr:输入的开始地址

n:SRAM PUFs响应长度

L:统计长度

Calculate_BER():统计整个SRAM PUFs的最大错误率

Dic_Addr_BER:SRAM PUFs的错误率信息(Add, BER)

List_Key_Addr:保存所有符合条件的地址块的首地址列表

1, Dic_Addr_BER=Calculate_BER()

2, for addr in Dic_Addr_BER:

3, if Dic_Addr_BER[addr]>BERinput:

4, Dic_Addr_BER[addr]=-1

5, while Addr < n-L+1:

6, if Dic_Addr_BER[Addr]==-1:

7, Addr=Addr+1

8, else:

9, List_Key_Addr.append(Addr)

10, Addr=Addr+L

地址块选择算法有以下2个优点:1)只需要保存各个块的首地址,而不是保存符合条件的每一个SRAM单元的地址;2)该算法只存在密钥生成的注册过程,不影响重建过程.如果生成128比特密钥需要4 000比特SRAM PUFs响应,在L=255的情况下,本文算法只需保存16个首地址;如果选取单个SRAM单元,那么需要保存对应数据的所有4 000个地址,极大地增加了系统的复杂度和存储空间.

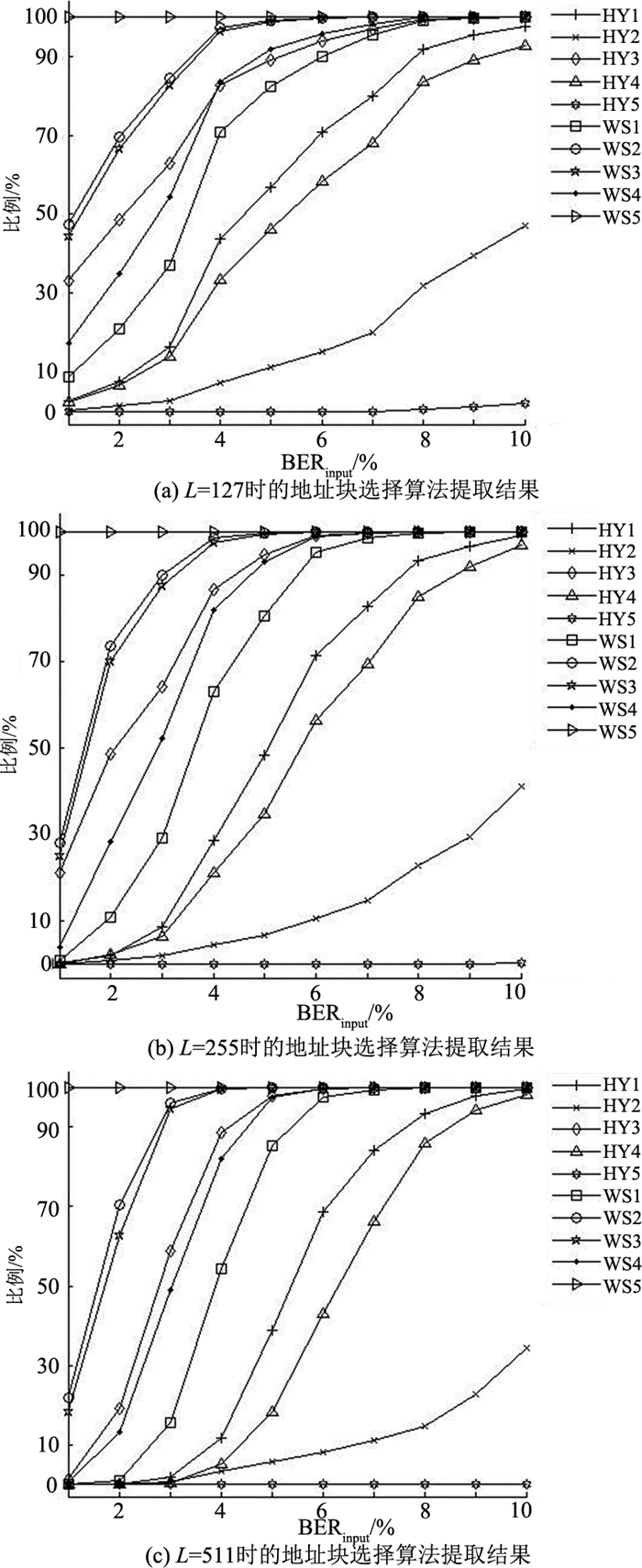

不同SRAM芯片的PUFs响应错误分布不同,使用地址块选择算法进行分析提取,可以得到不同设定错误率下用于密钥生成的SRAM PUFs响应的数量,如图 8所示.可以看出,不同统计长度下,同一块芯片得到的SRAM PUFs数据曲线相似;在同一统计长度下,不同芯片得到的SRAM PUFs数据差异明显,比如当设定错误率为5%时,HY2选取的数据为原PUFs数据数量的10%,WS1选取的数据达到原PUFs数据数量的80%.

|

图 8 地址块选择算法提取不同SRAM PUFs响应的数据 Fig. 8 Extracting data of different responses of SRAM PUFs using block address algorithm |

论述的密钥存储机制分为以下2个阶段.第一个阶段为注册阶段,配合芯片或系统的出厂测试进行SRAM初始地址筛选,并仅将该初始地址进行存储,供密钥生成阶段使用.在密钥生成阶段(即应用阶段),系统读取该初始地址进行密钥生成,提高可靠性.尽管该过程在一定程度上增加了芯片或系统的出厂测试成本,但是在对应用系统的密钥可靠性以及安全性有较大提升的前提下,对应用系统的制造成本影响较小,这对低成本信息安全机制具有重要意义.

3.2 参数化的辅助数据算法参数化辅助数据算法的思想是不改变SRAM PUFs的内部错误率,在纠错的过程中,通过加入参数寄存器的冗余数据,降低纠错模块中的错误率.

由3.1节的分析可知,大部分芯片在密钥提取的过程中使用地址块选择算法,可以得到足够多的SRAM PUFs数据.有些芯片的最大错误率较高,难以提取足够多的SRAM PUFs数据,比如HY5芯片,即使设定错误率为10%,选取的数据也不到原数据的5%.在这种情况下,使用参数化辅助数据算法,通过加入参数寄存器,和SRAM PUFs数据复接后一同进行纠错.

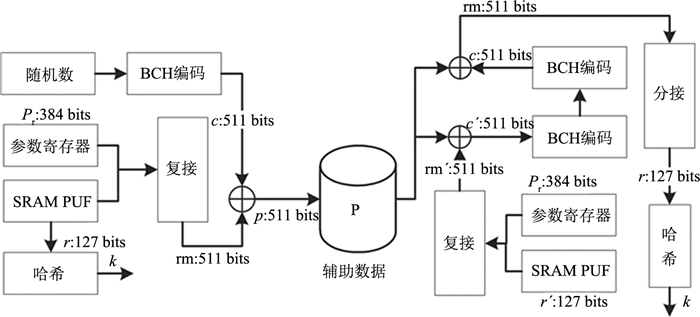

参数化辅助数据算法的实施框图如图 9所示.在注册过程中,SRAM PUFs响应r和参数寄存器中的数据pr复接成固定长度为N的数据rm,其中,N为BCH码的码长.随机比特编码成长度为N的BCH码,和rm异或后生成辅助数据p,放入非易失性存储器中保存.在重构过程中,从SRAM提取的噪声PUFs响应r′和辅助数据p异或得到码字c′,c′是包含SRAM PUFs错误的BCH码,经过译码后得到原来的信息,再经过相同的编码得到码字c,此时的码字c与注册时的码字完全相同,因此利用辅助数据p恢复原来的复接数据rm,复接数据rm经过分接得到正确的SRAM PUFs响应r,经过哈希可以得到准确无误的密钥k.从图 9可以看出,参数化辅助数据算法只降低纠错模块中的最大错误率,没有参与到熵值压缩过程中,因此不会对密钥的熵造成影响.

|

图 9 参数化辅助数据算法的实施框图 Fig. 9 Parametric helper data algorithm implementation diagram |

图 9的框图使用MATLAB软件仿真实现,包括BCH编码函数bchenc(),BCH译码函数bchdec();哈希函数使用Java接口中的java.security.MessageDigest.getInstance()实现,为SHA-256.步骤如下.1)设定参数,包括SRAM PUF长度len_r、辅助数据的长度len_pr和起始地址startAddr.此处len_r=127, len_pr=384,选定BCH(511, 295, 26)作为纠错码,可以纠正最大的错误率为5.08%.地址块选择算法记录了最大错误率为15%的地址Addr,startAddr从Addr中选择.2)注册过程.随机生成一组长度为295的数据random,编码为511位BCH码c.根据startAddr从本地读取一组SRAM PUF数据,与参数寄存器中的数据复接后,生成辅助数据p并保存到本地文件中,生成密钥k保存到当前环境变量.该注册过程只进行一次.3)重构过程.根据startAddr读取其他组的噪声SRAM PUF数据,与参数寄存器中的数据复接,参与密钥的重构,生成密钥kRec.4)比较验证.多组SRAM PUF数据需要多个重构过程,生成多个kRec,与注册过程中的k比较,相同则说明重构过程成功.

在软件仿真环境下,使用计时器tic/toc测试密钥的生成时间:在注册过程中,密钥生成的时间为128.84 ms;在密钥重构过程中,密钥生成的时间为139.35 ms.在实际应用中,一个密钥生命周期内注册过程只进行一次,因此该机制作为密钥生成器,一次密钥生成所需的时间为139.35 ms.

下面计算在加入参数寄存器后,纠错模块中最大错误率的变化.在无参数寄存器的情况下,每轮纠错中,原有的最大错误率定义为

| $ {\rm{BE}}{{\rm{R}}_{{\rm{before}}}}{\rm{ = }}\frac{{{\rm{Error}}}}{{\rm{L}}}{\rm{.}} $ | (5) |

加入参数寄存器之后的最大错误率定义如下:

| $ {\rm{BE}}{{\rm{R}}_{{\rm{after}}}}{\rm{ = }}\frac{{{\rm{Error}}}}{{{\rm{L}} + {P_{\rm{r}}}}}. $ | (6) |

减少的最大错误率可以表示为

| $ \begin{array}{l} {\rm{\Delta BER = BE}}{{\rm{R}}_{{\rm{before}}}}{\rm{ - BE}}{{\rm{R}}_{{\rm{after}}}}{\rm{ = }}\\ \frac{{{\rm{Error}} \times {P_{\rm{r}}}}}{{L \times \left( {L + {P_{\rm{r}}}} \right)}}{\rm{}}. \end{array} $ | (7) |

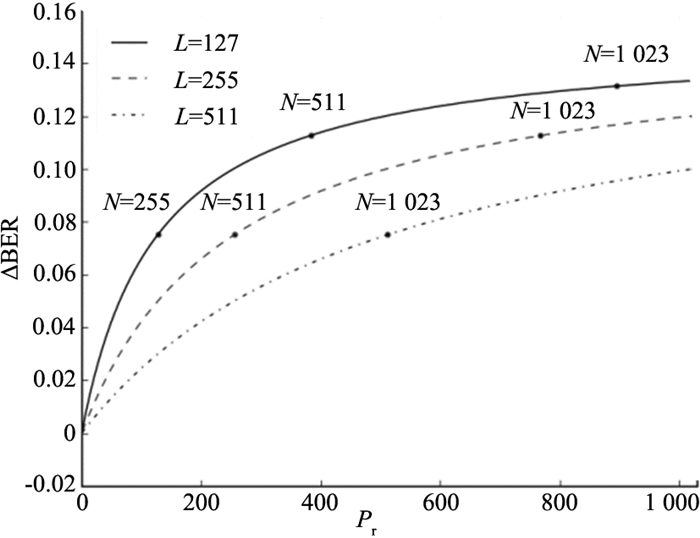

在错误率为15%的情况下,减少的最大错误率ΔBER和参数寄存器长度Pr之间的关系如图 10所示.可以看出,随着L的增加,ΔBER不断增加,即最大错误率不断降低.

|

图 10 参数化辅助数据算法下Pr对ΔBER的影响 Fig. 10 Effects of Pr on ΔBER using parametric helper data algorithm |

当Pr=384,N=511时,将各参数代入式(7),得到降低的最大错误率ΔBER为11%,即纠错模块中的最大错误率降到4%左右,与原SRAM PUFs中的最大错误率相比降低了73%.使用参数化辅助数据算法后,纠错模块中可以根据错误率选择合适的纠错码,相应的译码结构会大幅降低,从而减少资源消耗.参数化辅助数据算法可以用于错误率低的SRAM芯片中,减少环境噪声的影响.

4 结语本文分析不同SRAM PUFs内部空间的错误率,提出使用地址块选择算法和参数化辅助数据算法来处理错误分布不均的情况.通过实验和分析可知,采用这两种方法能够有效地提高SRAM PUFs密钥生成的可靠性;可靠性的提高导致错误率减少,从而降低所使用的纠错码译码结构复杂度,降低了资源消耗.当SRAM PUFs最大错误率为15%时,通过改变参数寄存器的长度,纠错模块可以降低11%的错误率,纠错模块中的最大错误率降到4%左右,与原SRAM PUFs中的最大错误率相比降低了73%.本文提出的方法适合密钥生成,也可以用于对可靠性要求高的SRAM PUFs认证.

| [1] |

LEEST V V D, MAES R, SCHRIJEN G, et al. Hardware intrinsic security to protect value in the mobile market[C]//Information Security Solutions Europe 2014 Conference. Brussels:Springer, 2014:188-198. http://link.springer.com/content/pdf/10.1007/978-3-658-06708-3_15.pdf

|

| [2] |

HERDER C, YU M D, KOUSHANFAR F, et al. Physical unclonable functions and applications:a tutorial[J]. Proceedings of the IEEE, 2014, 102(8): 1126-1141. DOI:10.1109/JPROC.2014.2320516 |

| [3] |

LIM D, LEE J W, GASSEND B, et al. Extracting secret keys from integrated circuits[J]. IEEE Transactions on Very Large Scale Integration Systems, 2005, 13(10): 1200-1205. DOI:10.1109/TVLSI.2005.859470 |

| [4] |

GASSEND B, CLARKE D, VAN D M, et al. Silicon physical random functions[C]//ACM Conference on Computer and Communications Security. Washington:ACM, 2002:148-160. http://citeseerx.ist.psu.edu/viewdoc/versions?doi=10.1.1.12.6972&version=2

|

| [5] |

GUAJARDO J, KUMAR S S, SCHRIJEN G J, et al. FPGA intrinsic PUFs and their use for IP protection[C]//International Workshop on Cryptographic Hardware and Embedded Systems. Vienna:Springer, 2007:63-80. http://dl.acm.org/citation.cfm?id=1421971

|

| [6] |

HOLCOMB D E, BURLESON W P, FU K. Power-up SRAM state as an identifying fingerprint and source of true random numbers[J]. IEEE Transactions on Computers, 2009, 58(9): 1198-1210. DOI:10.1109/TC.2008.212 |

| [7] |

PRABHU P, AKEL A, GRUPP L M, et al. Extracting device fingerprints from flash memory by exploiting physical variations[C]//Proceedings of the 4th International Conference on Trust and Trustworthy Computing. Pittsburgh:Springer, 2011:188-201. http://dl.acm.org/citation.cfm?id=2022264

|

| [8] |

KUMAR S S, GUAJARDO J, MAES R, et al. The butterfly PUF protecting IP on every FPGA[C]//Hardware-Oriented Security and Trust. Anaheim:IEEE, 2008:67-70. http://www.computer.org/csdl/proceedings/hst/2008/2401/00/04559053-abs.html

|

| [9] |

DODIS Y, REYZIN L. Fuzzy extractors:how to generate strong keys from biometrics and other noisy data[J]. Proceedings of the International Conference on Advances in Cryptology Lecture, 2004, 38(1): 523-540. |

| [10] |

SCHRIJEN G J, LEEST V V D. Comparative analysis of SRAM memories used as PUF primitives[C]//Conference on Design, Automation and Test in Europe. Dresden:EDA Consortium, 2012:1319-1324.

|

| [11] |

LEEST V V D, PRENEEL B, SLUIS E V D. Soft decision error correction for compact memory-based PUFs using a single enrollment[C]//International Conference on Cryptographic Hardware and Embedded Systems. Leuven:Springer, 2012:268-282. http://link.springer.com/10.1007/978-3-642-33027-8_16

|

| [12] |

MAES R, TUYLS P, VERBAUWHEDE I. Low-overhead implementation of a soft decision helper data algorithm for SRAM PUFs[C]//Cryptographic Hardware and Embedded Systems. Lausanne:Springer, 2009:332-347. http://dl.acm.org/citation.cfm?id=1617755

|

| [13] |

ZHAO S, ZHANG Q, HU G, et al. Providing root of trust for ARM TrustZone using on-chip SRAM[C]//Proceeding of the 4th International Workshop on Trustworthy Embedded Devices. Scottsdale:ACM, 2014:25-36. http://dl.acm.org/citation.cfm?id=2666145

|