随着集成电路工艺水平的不断提高、CMOS晶体管尺寸不断的缩小以及工作电压不断的降低, 电路节点电容随之减少, CMOS电路越发容易受到辐射效应引起的软错误影响[1-2].辐射引起的存储节点电荷堆积引发的单粒子翻转(single event upset, SEU)是造成电路发生软错误的一个主要原因[3].为了克服粒子轰击对静态随机存储器(static random access memory, SRAM)的影响, Calin等[4-8]从不同的层级, 提出不同的优化解决方法.在电路层级上, 对SRAM单元改进的经典的结构有双向互锁存储单元(dual interlocked cell, DICE)[4]和4节点存储单元(quad-node ten transistor cell, QUATRO)[5]等, 其他很多改进型的结构都以几种经典结构为基础[6-9].在经典的存储单元中, DICE单元是应用和研究最广泛的[10], 本文主要针对DICE单元进行研究.

在传统的存储单元中, 读写稳定性会随着电路遭受偏置温度不稳定性效应(bias temperature instability, BTI)发生退化;这是因为BTI效应影响MOS管等效电阻和驱动能力的相对比值, 结果使得读写噪声容限降低[11].Yang等[12]研究正偏置温度不稳定性效应(positive bias temperature instability, PBTI)和负偏置温度不稳定性效应(negative bias temperature instability, NBTI)对传统SRAM单元的影响, 指出单元的读写能力退化程度与存储值的占空比有关.DICE单元的读写稳定性受到BTI效应的威胁.

目前, 针对DICE单元的老化特性研究及抗老化设计比较缺乏.Wang等[13]研究指出, DICE单元处于读状态下, 容忍SEU能力会发生失效, 从增加读状态时单元的容忍SEU能力角度对DICE单元的读写端口作出了改进, 把8晶体管SRAM单元[14]中分离读写端口的结构加入到DICE单元中, 分离的读写端口可以保持单元在读状态下容忍SEU的能力, 同时可以抑制读干扰, 减缓因BTI效应引起的稳定性退化问题.类似的分离读写功能的思想, 文献[15]中也有使用.读写端口分离的结构在处于和读状态类似的半选择状态时会失效[16].读写端口的分离改变了原存储单元的读写方式, 这在很大程度上增加了设计的复杂度和开销.

本文从改善DICE单元的读写稳定性和寿命出发, 首先对受BTI效应影响的老化特性进行具体的分析和HSPICE仿真, 发现随着老化的加剧, 读干扰和半选择干扰日益加重, 严重威胁存储单元的寿命和可靠性.利用DICE单元存储节点冗余的特性, 提出新的DICE的读写端口结构.和文献[13]中的结构不同, 本文提出的新结构抑制了DICE单元遭受到的读干扰和半选择干扰, 延长了电路的使用时限;增强了存储单元处于读状态和半选择状态时的容忍能力.新的DICE读写端口不改变原始的DICE单元的读写方式, 这大大减小了设计的复杂度和开销.

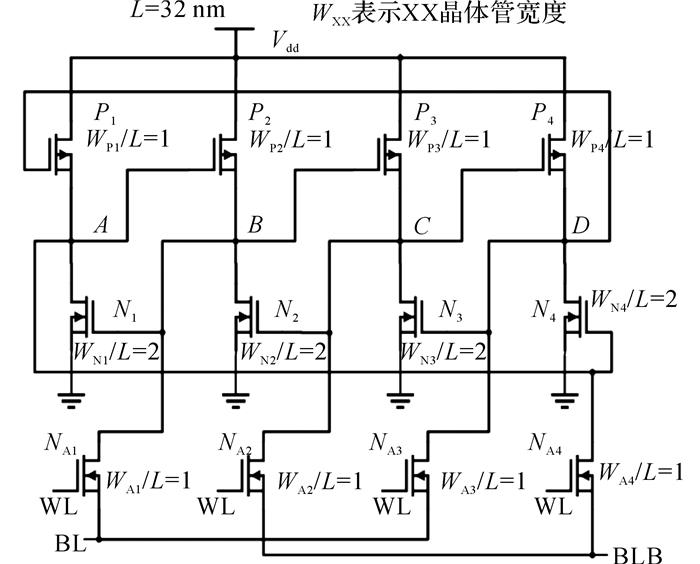

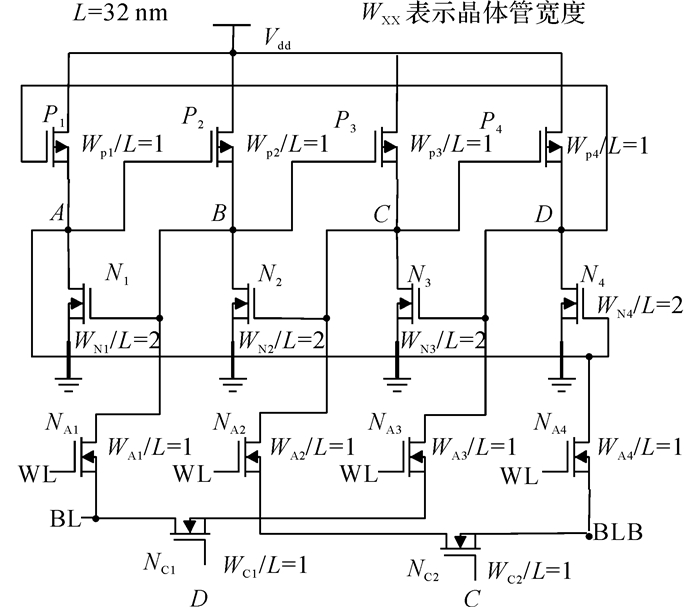

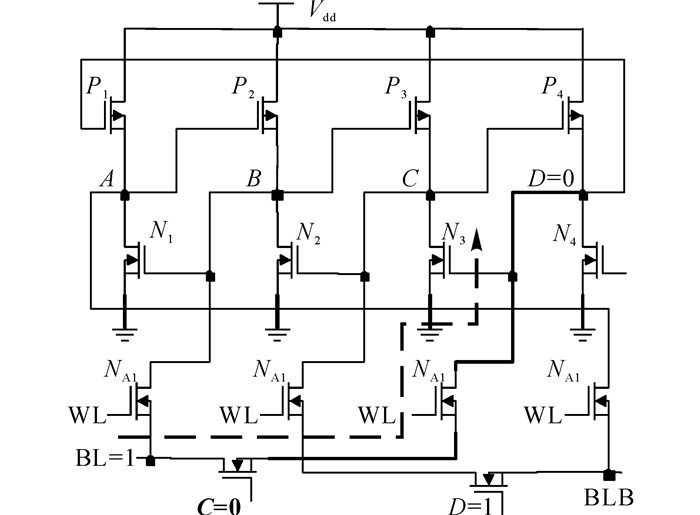

1 DICE单元和老化模型 1.1 传统静态随机存储器DICE单元DICE单元的结构如图 1所示, 8个MOS管(N1~N4、P1~P4)组成的4个反向器结构交错反馈构成单元的4个存储节点(A、B、C、D), 其余的4个NMOS管(NA1~NA4)作为传输管, 构成读写传输端口.DICE单元和传统6晶体管存储单元有相似的读写端口和读写原理, 不同的是DICE单元为了保证读写功能的正常, 必须有两对传输管分别连接4个存储节点和对应的位线, 而传统的6晶体管单元只有一对.4个节点存储的值有高、低电平两个状态, 以下的分析用“1”表示高电平, “0”表示低电平.

|

图 1 传统静态随机存储器DICE单元 Fig. 1 Traditional static random access memory DICE cell |

在保持状态时, 4个存储节点相继存储“1”和“0”, 每当高能粒子轰击内部节点导致该点存储值的翻转时, 反馈结构总是可以使存储值还原.假设存储节点的初始值为A=1、B=0、C=1、D=0, B受高能粒子轰击干扰由0跳变为1, A节点中存储的0可以使B节点存储值还原, 跳变不会在相邻的节点中传递.类似地, 当4个存储节点中的一个节点中存储的值由1跳变为0时, 翻转会被相邻节点的值还原, 避免了SEU的发生.DICE单元的4个存储节点无论对单节点0-1翻转还是1-0翻转都可以容忍.Rennie等[17]研究指出, 在130 nm及以上节点技术中, 可以认为DICE单元对单节点SEU免疫.

1.2 BTI老化模型本文考虑的老化主要是BTI效应引起的老化, 当PMOS管受压时, 在NBTI的作用下, 氧化层表面的硅-氢键会在电场力的作用下发生断裂, 从而在PMOS管沟道中形成许多界面陷阱.偏置的时间越长, 界面陷阱的数量越多.不断增多的界面陷阱会逐渐升高PMOS管的阈值电压Vth.当PMOS管关闭时, 随着应力的消失, 处于PMOS管沟道中的部分氢原子由于反向电场力的作用, 重新与硅原子相结合, 修复一部分原先断裂的硅-氢键, 使NBTI效应的影响降低, 漂移的阈值电压ΔVth会得到部分的恢复.对于NMOS管来说, 在普通的氧化物多晶硅栅工艺器件中, PBTI造成的ΔVth非常小, 所以在大多数的研究中没有被考虑.随着器件特征尺寸的缩减, 当集成电路制造工艺采用高k金属栅极材料时, PBTI效应对电路的性能有了明显的影响.Yang等[18]证明, 在特征尺寸低于45 nm的高k材料工艺中, PBTI效应造成NMOS的ΔVth退化, 甚至高于NBTI对NMOS造成的影响.

NBTI(PBTI)效应对PMOS(NMOS)管ΔVth的影响可以用AC RD(reaction-diffusion)模型来进行描述. Yang等[19]对RD模型作了简化, 如下所示:

| $ \Delta {V_{{\rm{th}}}}\left( t \right)\tilde = {K_{{\rm{AC}}}} \times {t^n}\tilde = \alpha \left( {S, f} \right) \times {K_{{\rm{DC}}}} \times {t^n}. $ | (1) |

| $ \begin{array}{l} {K_{{\rm{DC}}}} = A \times {T_{{\rm{OX}}}} \times \sqrt {{C_{{\rm{OX}}}}\left( {{V_{{\rm{gs}}}}- {V_{{\rm{th}}}}} \right)} \times \\ \;\;\;\;\;\;\;\;\;\left[{1-{V_{{\rm{DS}}}}/\left( {\alpha \left( {{V_{{\rm{gs}}}}-{V_{{\rm{th}}}}} \right)} \right)} \right] \times \exp \left( {{E_{{\rm{OX}}}}/{E_0}} \right) \times \\ \;\;\;\;\;\;\;\;\exp \left( { -{E_{\rm{a}}}/\left( {KT} \right)} \right). \end{array} $ | (2) |

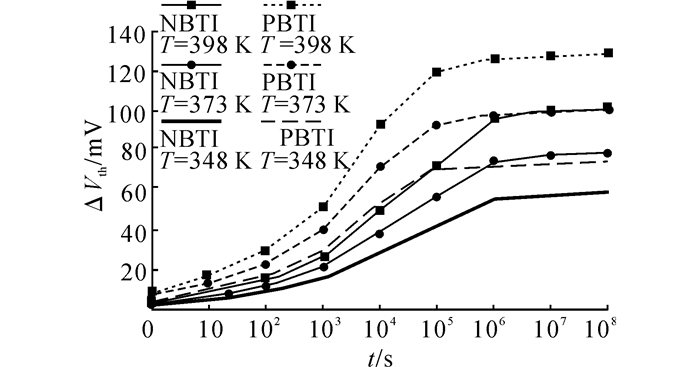

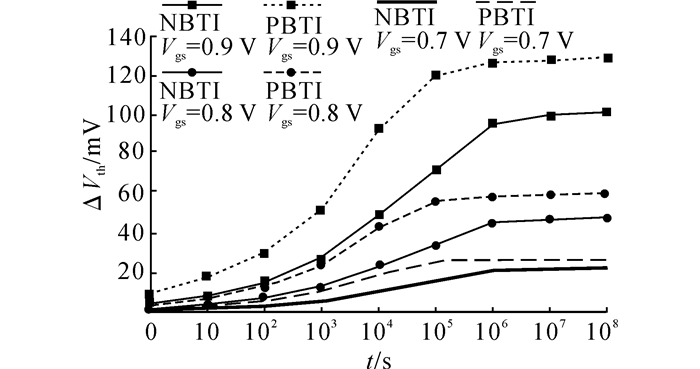

式中:α为自变量, 是信号频率f和信号占空比S的函数; KDC为取决于制造工艺的常数; A为和工艺相关的常数; TOX为栅氧化层厚度; Vgs为栅源电压;EOX为栅电场强度; K为玻尔兹曼常数; T为温度.Rennie等[17]对模型的细节有更详细的阐述.在晶体管持续受压的静态条件下, 利用RD模型结合PTM高k 32 nm[20]器件模型中的具体参数值计算出的阈值电压随着受压时间的漂移量如图 2、3所示.如图 2所示为当Vgs=0.9 V在不同温度下的ΔVth.如图 3所示为当T=398 K时,不同栅源电压下的ΔVth.

|

图 2 不同温度高k材料MOS器件受BTI效应影响ΔVth变化 Fig. 2 ΔVth drifts induced by BTI for high-k metal gate under different temperature |

|

图 3 不同Vgs高k材料MOS器件受BTI效应影响ΔVth变化 Fig. 3 ΔVth drifts induced by BTI for high-k metal gate under different Vgs |

由于SRAM单元一般采用较小的特征尺寸工艺, 易受工艺波动(process variations)的影响;阈值电压Vth是一个容易受其影响的参数, Vth的标准差是一个关于器件尺寸的函数

对于DICE单元中的各个晶体管来说, 不考虑BTI效应影响时, 初始Vth服从高斯分布:

| $ {V_{{\rm{th}}}} = {V_{{\mathop{\rm int}} }}\left( {m, \delta } \right). $ | (3) |

式中:m为晶体管的初始Vth, δ为考虑工艺影响时Vth的标准差.

考虑BTI效应的影响, 将Vth作为时间的函数, 表达式为

| $ {V_{{\rm{th}}}} = {V_{{\mathop{\rm int}} }}\left( {m, \delta } \right) + \Delta {V_{{\rm{th}}}}\left( t \right) + {V_{{\rm{td}}}}\left( {0, {\delta _{\rm{d}}}\left( {\Delta {V_{{\rm{th}}}}\left( t \right)} \right)} \right). $ | (4) |

式中:ΔVth(t)为受BTI效应影响阈值电压的漂移值; Vtd(0, δd(ΔVth(t)))对应的ΔVth受BTI效应影响的随机变化, 服从Skellam分布[21].为了简化分析复杂度, 不考虑ΔVth受BTI效应影响的随机变化, 式(4) 可以简化为

| $ {V_{{\rm{th}}}} = {V_{{\mathop{\rm int}} }}\left( {m, \delta } \right) + \Delta {V_{{\rm{th}}}}\left( t \right){\rm{ = }}{V_{{\mathop{\rm int}} }}\left( {m + \Delta {V_{{\rm{th}}}}\left( t \right), \delta } \right). $ | (5) |

以下对DICE单元的BTI老化特性分析会使用到蒙特卡罗方法, 分析方法采用的分布模型服从式(5).式(5) 中的m、δ和ΔVth都是通过结合DICE单元中具体的晶体管几何尺寸以及RD老化模型和PTM高k 32 nm器件模型中给出的参数计算得到.

2 BTI效应对DICE结构的影响研究DICE单元分别在读、写状态下的稳定性.主要考虑在BTI效应影响下的最坏情况, 存储单元长时间存储某一值, 即MOS处于静态受压状态, 单元中受压的MOS管ΔVth漂移, 改变原本对称的存储单元结构.实验仿真时, DICE单元如图 1所示.由于SRAM单元占据了大部分的芯片面积, 几何尺寸通常取满足功能的最小尺寸[10].在进行SPICE模拟仿真时, 本文在满足上拉P管、传输管以及下拉N管内在宽长比要求的前提下[20], 将DICE单元中所有晶体管的长均设为最小几何长度, 上拉P管和传输管的宽长比均设为1:1, 下拉N管的宽长比设为2:1.以下所有对DICE单元的仿真实验均基于该设定.

2.1 写操作DICE单元的写操作可以参考图 1, 令节点存储的初始值分别为A=1, B=0, C=1, D=0;进行写操作时, 首先字线BL置高, BLB置低; 然后WL置高4个传输管开启, A、C节点电平开始通过传输管NA2、NA4放电, 电平被拉低, 当拉低的电平使得N2、N4关闭, P2、P4开启, 节点B、D的电平被抬高, 写操作完成.若DICE单元长时间存储初始值, 则N2、N4的下拉能力被PBTI削弱, P1、P3的上拉能力被NBTI削弱, 这使得接下来的写入上拉和下拉电平变得更容易; N2、N4、P1、P3的削弱可以导致写操作最坏情况的发生, 最坏情形概括如下.

t=0 to t1: A=1, B=0, C=1, D=0.

受BTI效应, N2、N4、P1、P3驱动能力下降.

t=t1+Tclk:单元翻转A=0, B=1, C=0, D=1.

t=t1+nclkTclk:在经过nclk个周期之后单元再次写入相反值, 使得A=1, B=0, C=1, D=0.

当t=t1时, 单元受BTI效应的影响, 晶体管驱动能力变得不对称.若nclk足够大, 则DICE单元受BTI效应的影响, 会逐渐恢复对称结构; 写操作最坏的情况发生在nclk非常小的时候, 此时P2、P4不受NBTI效应的影响, 因此下拉B、D节点没有变得容易, P1、P3节点受NBTI效应的影响, 上拉能力减弱.

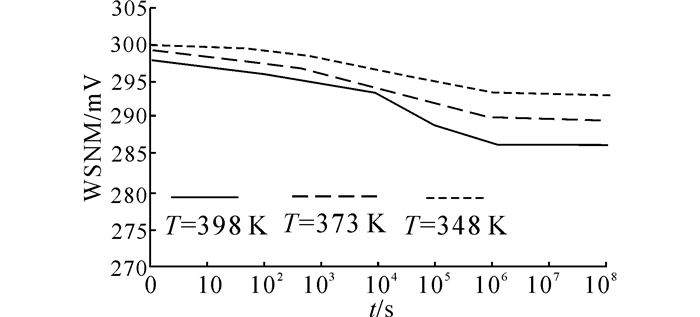

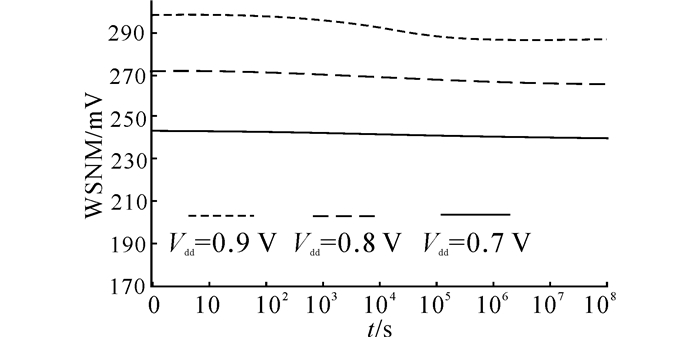

一般用写静态噪声容限(write static noise margin, WSNM)来表征单元的写入能力.WSNM定义为在写操作时写入成功所能遭受的最大噪声干扰.WSNM越小, 表示写操作越不稳定; 当WSNM为0时, 写操作不能正常进行.利用HSPICE对DICE单元进行仿真, 当t=t1时, 在不同的温度和电源电压的条件下, DICE单元长时间存储某一值的情况下, WSNM退化如图 4、5所示.考虑不同的温度和电源电压的环境条件时, 虽然WSNM的初值不同, 但参照WSNM为0的写故障发生条件, 相对退化量都很小.

|

图 4 不同温度下WSNM随时间退化(Vdd=0.9 V) Fig. 4 WSNM deterioration under different temperature |

|

图 5 不同供电电压下WSNM随时间退化(T=398 K) Fig. 5 WSNM deterioration under different Voltage |

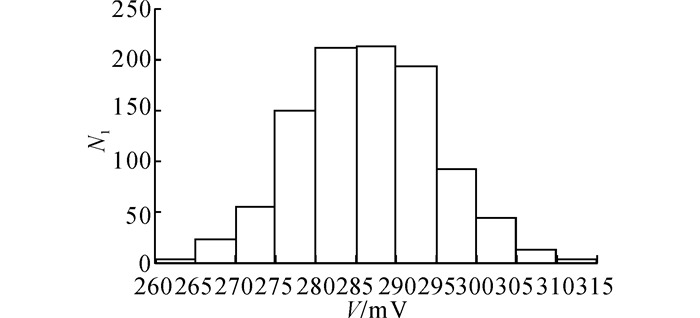

应用式(5) 的模型, 当T=398 K, Vdd=0.9 V时, 对t=t1(t1=108 s)时的DICE单元进行1 000次蒙特卡罗分析, 得到如图 6所示的WSNM分布.图中, V为电压, N1为WSNM落在相应电压区间中的数量.经计算可知, 均值μ=284.6 mV, 标准差δ=8.7 mV.仿真结果表明, t1=108 s后, 写操作WSNM从298.4 mV退化到284.6 mV, 退化量仅为4.6%, 且考虑随机性的最坏情况时的WSNM达到了260 mV.这是因为影响写操作的主要因素是高电平节点的下拉, 而低电平节点的上拉其次; 最坏情况时的节点高电平下拉能力没有受到BTI效应的影响, 因此写操作的稳定性退化较小.

|

图 6 经历108 s后DICE单元WSNM分布 Fig. 6 WSNM distribution of DICE cell after 108 s aging |

DICE单元的读操作可以参考图 1.令节点存储的初始值分别为A=1, B=0, C=1, D=0;进行读操作时, 首先两条位线BL、BLB电平被同时置高, 接着字线WL置高传输管开启, 此时位线BL通过NA1、N2和NA3、N4两条通路放电, BL电压降低使两条位线出现一个电位差, 这个电位差会经差分灵敏放大器放大作为读出的数据.在读取的过程中, B和D点的低电平会被拉高, 这被称为读干扰(read disturb), 升高的值取决于NA1和N2以及NA2和N4的相对驱动能力.当DICE单元存储固定值经过一定时间后, 受BTI效应的影响, 读过程中B、D点会遭受更大的读干扰.在最坏情况下, 读干扰导致读取的过程中单元发生翻转, 造成读故障(read failure).读故障发生的机理类似传统的6晶体管SRAM单元.

读操作的最坏情况发生在当存储单元长时间存储固定数据后的读取操作; 相当于A、B、C、D长时间存储1、0、1、0, N2、N4在长时间的静态受压情况下受PBTI效应的影响, 驱动能力减弱, 这会在B、D两点引入更高的干扰电平; 同时, P1、P3管受NBTI效应的影响, 阈值电压漂移, 更容易被干扰电平关闭, 使A、C点电平被拉低.对于读操作来说, 最坏情形可以概括为

t=0 to t1: A=1, B=0, C=1, D=0.

受BTI的效应, N2、N4、P1、P3驱动能力下降.

t=t1+Tclk:读操作发生.

由于DICE单元结构对称, 在A、B、C、D长时间存储A=0, B=1, C=0, D=1的情况下, 会导致最坏情况的发生.

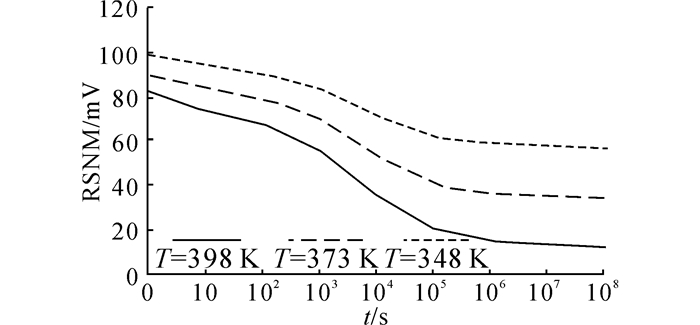

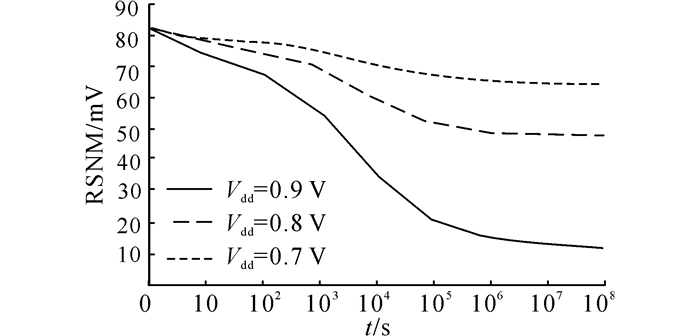

在SRAM单元设计中, 读干扰的引入降低了静态噪声容限, 在读操作时, 存储单元的稳定性用读静态噪声容限(read static noise margin, RSNM)来表征.RSNM的定义为读操作时引入最大的读干扰电平和使得单元存储值翻转的最高电平的差值.RSNM越小, 在读过程单元越容易发生翻转.当RSNM为0时, 读操作不能正常进行, RSNM通常用来衡量DICE单元的读稳定性.利用HSPICE对DICE单元进行仿真, 当t=t1时, 在不同的温度和电源电压的条件下, DICE单元长时间存储某一值的情况下, RSNM退化如图 7、8所示.

|

图 7 不同温度下RSNM随时间的退化(Vdd=0.9 V) Fig. 7 RSNM deterioration under different temperature |

|

图 8 不同供电电压下RSNM随时间退化(T=398 K) Fig. 8 RSNM deterioration under different voltage |

考虑式(5) 的模型, 当T=398 K, Vdd=0.9 V时, 对t=t1(t1=108 s)时的DICE单元进行仿真, RSNM的分布如图 9所示.图中, N2为WSNM落在相应电压区间中的数量.经过108 s老化后, RSNM的退化率达到了77.3%.以RSNM < 0的单元个数比率计算SRAM的读失效率, 则在经过108 s的静态受压后, 读失效率达到22.6%.随着RSNM的整体退化, 其他没有失效的单元变得极不稳定, 容易在外界微小的噪声干扰下发生错误.DICE单元读故障的发生在文献[22]中也有提及和探讨.

|

图 9 经历108 s后DICE单元RSNM Fig. 9 RSNM of DICE cell after 108 s aging |

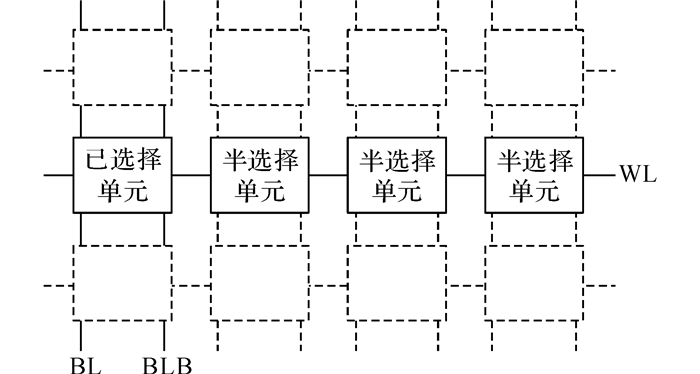

DICE单元在处于半选择状态时, 会遭遇和读状态相似的干扰, 如图 10所示.存储器阵列在读写操作过程中, 当一个存储单元被选中, 字线电平置高时, 和这根字线相连的同一行的存储单元虽然没有被选中, 但传输管会同时被打开.在闲置状态下的位线(BLB和BL)处于浮空态高电平, 因此这些处于半选择状态的存储单元会经历和读状态单元相似的干扰, 称为半选择干扰.半选择干扰和读干扰一起成为影响DICE单元可靠性和寿命的重要因素.在传统的SRAM单元中, 存在相似的问题.为了消除半选择状态, 可以使字线的每一行只控制一个字, 这相应地增加字线的数量和面积开销.或者采用非传统的SRAM行列结构[23], 利用更复杂的字线和位线电平控制, 避免半选择干扰对单元的影响.

|

图 10 存储阵列中的半选择单元 Fig. 10 Half-selected cell in memory array |

经过2.1、2.2节的分析可知, 在最坏情况下, 相比于写入能力随使用时间的轻微退化, 影响DICE单元稳定性及寿命的主要因素是在读过程时单元的抗噪能力受BTI效应影响的退化.在读过程中, 容易造成单元翻转的原因是在DICE单元两个存储“0”的节点中同时引入了高电平干扰, BTI效应的存在同时提高了两个存储点遭受的干扰电平.结合DICE单元对单点电平翻转免疫的特性, 对DICE结构的读、写端口作出改进.如图 11所示, 在原本相连的两对传输管之间分别加入控制管NC1和NC2.NC1、NC2的插入隔离了原本两两相连的传输管, 栅极分别和节点C、D相连, 由C、D两个节点的电平来控制NC1、NC2的开闭.

|

图 11 改进的DICE单元 Fig. 11 Modified DICE cell |

加入的控制管负责隔离在读状态时相通的存储节点, 为了节省面积开销, 可取最小尺寸.在对改进的DICE单元进行HSPICE仿真试验时, 控制管的宽长比设为1:1, 仿真环境选取T=398 K, Vdd=0.9 V.

3.2 改进的DICE单元抗BTI能力分析在改进后的结构中, 由于控制管分别由相邻的C、D节点的电平控制开闭, 两个连接存储“0”节点传输管的源极断开, 另外两个连接存储“1”节点传输管的源极相连.当DICE单元处于读取或半选择状态时仅有一个节点会出现高电平的干扰, DICE单元固有的抗单点翻转特性会将其屏蔽.这有效提高了DICE单元处于读状态或半选择状态时的稳定性和寿命.

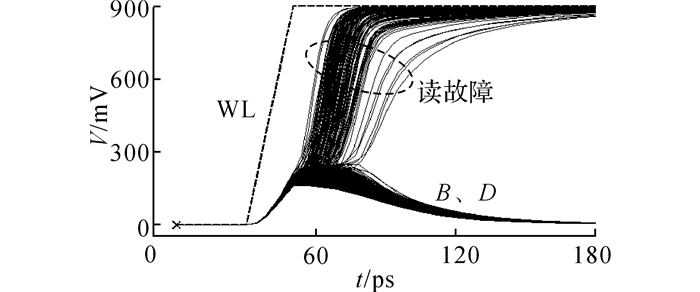

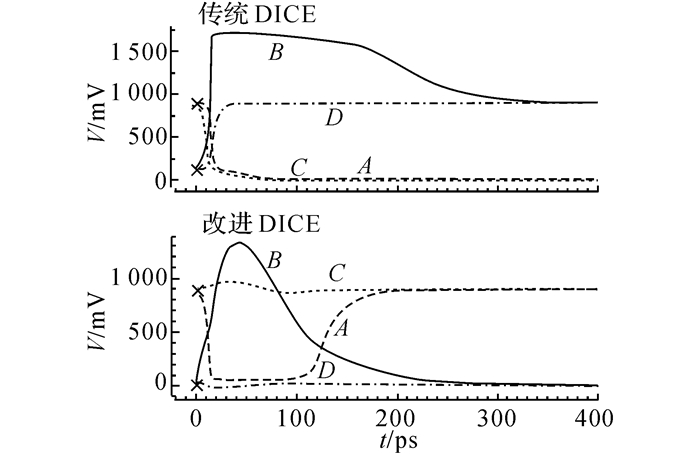

如图 12所示为采用蒙特卡罗方法进行1 000次仿真, 传统DICE单元在静态受压108 s后的读故障模拟.设单元初始值为A=1,B=0,C=1,D=0;当字线电平抬高后,读操作开始, 有一部分DICE单元的B、D节点受读干扰的影响电平发生翻转, 使整个单元翻转失效.

|

图 12 传统DICE单元老化后读故障模拟 Fig. 12 Read failure simulation of original DICE cell after aging |

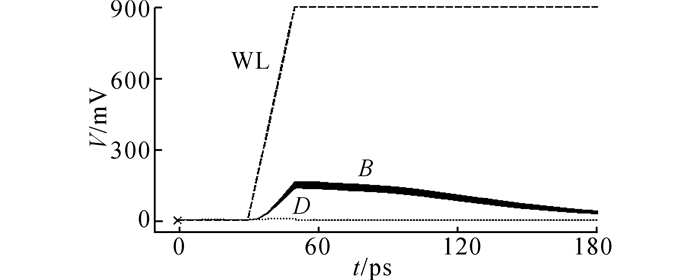

如图 13所示为采用蒙特卡罗方法进行1 000次仿真, 改进DICE单元在静态受压108 s后的读时序图.此时, B节点虽然受到读干扰的影响, 但D节点因为控制管的存在免受读干扰的影响, 进而使DICE单元对读干扰免疫.

|

图 13 改进的DICE单元读故障消除模拟 Fig. 13 Elimination of read failure for modified DICE cell |

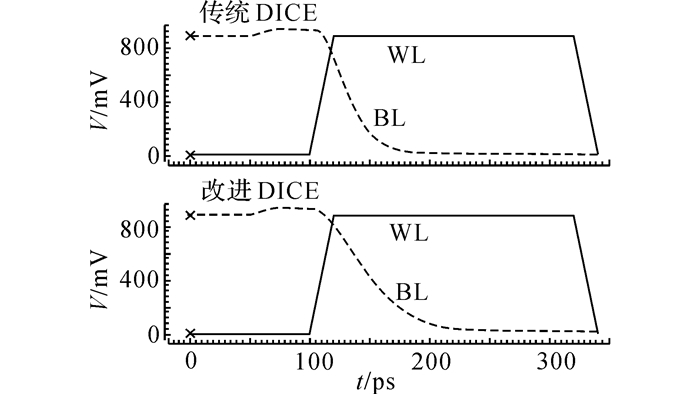

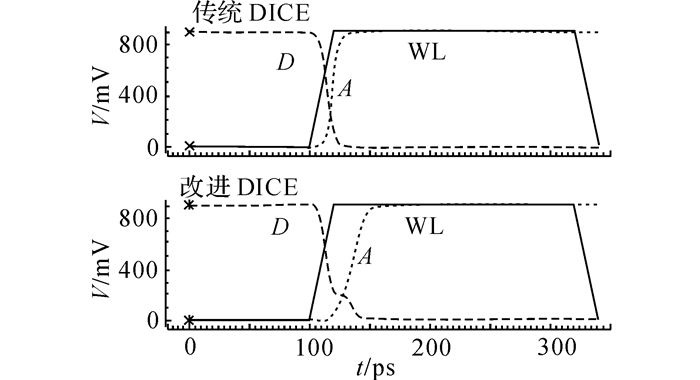

在改进的DICE单元结构中, 一个传输管仍然和一个存储“0”的节点相连, 这可以保证位线的高电平被下拉, 读操作正确执行.原DICE结构和改进后的结构的读时序功能如图 14所示, 位线BL的下降时间为读延时, 改进后结构的读延时相比增加一倍, 这是由于改进后的结构只有一个传输管负责下拉字线电平.可以通过增加传输管的宽长比, 增强驱动能力来补偿读延时的下降; 相比于传统的DICE单元, 这一点较容易实现, 因为改进后的单元结构对读干扰有屏蔽作用, 不用考虑增加传输管宽长比带来的读干扰增加的问题.

|

图 14 改进DICE单元读取操作模拟 Fig. 14 Reading process simulation of modified DICE |

当单元处于写状态时, 连接存储“0”节点的两个传输管源极断开, 连接存储“1”节点的两个传输管源极仍然相连; 根据2章的分析可知, 在写入数据时, 起主要作用的是存储“1”节点电平的下拉, 而存储“0”节点的上拉作用相对较小, 因此虽然在写入时仅有3个传输管与存储节点相连接, 写操作的正确性仍然能够被保证.改进后DICE单元与原单元的对比如图 15所示, 可以观察到改进后DICE单元的写延时会有一些增加.这一部分是由于只有一个传输管负责拉高低电平节点, 另一部分是因为控制管和DICE单元中的下拉N管阈值电压相同, 当两个高电平节点被下拉时控制管会被拉低的电平关闭, 从而不能及时地完全下拉两个节点的电平.可以在单元设计时提高下拉N管的阈值电压, 同时减小控制管的阈值电压, 来实现更快、更稳定的数据写入.

|

图 15 改进DICE单元写入操作模拟 Fig. 15 Writing process simulation of modified DICE |

使用双指数电流源模拟故障注入, 公式如下:

| $ {I_{{\rm{seu}}}}\left( t \right) = \left( {{Q_{{\rm{seu}}}}/{\tau _2}-{\tau _1}} \right)\left( {{{\rm{e}}^{-t/{\tau _2}}}-{{\rm{e}}^{ - t/{\tau _1}}}} \right). $ | (6) |

式中:Iseu为节点注入电流; Qseu为节点的沉积电荷; τ2、τ1分别为电荷聚集时间常数及离子建立常数, 与具体的电路工艺相关.

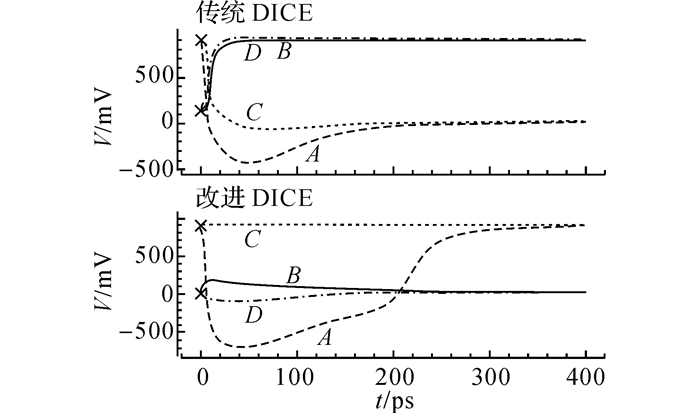

传统DICE单元在读状态或半选择状态时, 受到位线上拉的干扰丧失对单点SEU的容忍性, 出现在任何节点上的0-1或1-0翻转都会引起整个单元存储内容的翻转.设DICE单元的初始值为A=1, B=0, C=1, D=0;读操作开始时, B点出现0-1翻转, 打开的N1管因较强的下拉能力, 把A点的高电平拉低, 进而关闭N4管, D点由于P4和N4管同时关闭处于浮空状态, 此时D点被高电平位线上拉, 结果使DICE单元翻转.由于DICE单元的4个存储节点结构相同, 当0-1翻转出现在D点时, 会引起整个存储单元的值的翻转.类似地, 存储单元无法容忍在A或C出现的1-0翻转.

改进后的DICE在增加传统DICE单元抗老化能力的同时, 增强了单元处于读状态和半选择状态节点的容忍SEU能力.当DICE单元处于读状态或半选择状态时, 两个存储0的节点是断开的.设单元初始值A=1, B=0, C=1, D=0, D点和高电平的字线的连接断开, 这避免了D处于浮空态时电平被上拉, 单元可以有效容忍B点受SEU的影响出现0-1翻转.改进后, DICE单元与原DICE的D点0-1翻转容忍能力对比如图 16所示.在实验中, 在t=0时注入故障, 原单元B点遭受0-1干扰后, A、B、C、D4节点的存储值全部发生翻转, 改进后的单元只有B、A节点电平出现短暂的翻转, 随即恢复原状.同理, 改进后的DICE单元可以容忍发生在A点的1-0翻转, 如图 17所示, 原DICE结构因A点的干扰发生错误, 而改进后的单元可以有效容忍干扰.

|

图 16 单元改进前、后B点容忍0-1翻转能力对比 Fig. 16 Comparison of 0-1 flip of node B tolerance ability before and after modification |

|

图 17 单元改进前、后A点容忍1-0翻转能力的对比 Fig. 17 Comparison of 1-0 flip of node A tolerance ability before and after modification |

改进后DICE单元会受到0-1翻转和1-0翻转的影响, 和文献[12]相比, 虽然并不能做到在读状态时的4个节点完全容忍SEU, 但是在半选择状态时, 相比于文献[12]中单元的容忍SEU能力丧失.本文提出的结构能够使一半的节点对SEU完全容忍, 保证了DICE单元的整体抗辐射特性.

3.4 改进的DICE速度、功耗、面积开销分析在功耗方面, 当芯片制造工艺达到45 nm及以下时, 静态功耗成为电路总功耗的决定因素, 因此对DICE单元的功耗分析侧重于静态漏电功耗.在改进的DICE单元中, 加入的控制管增加了DICE单元位线漏电通路上的等效电阻, 如图 18所示; 位线漏电流是存储单元静态功耗的重要组成部分, 因此功耗降低, 为6.7%.功耗的降低使电路的工作温度降低, 这有助于减少晶体管的老化, 延长电路使用时限.

|

图 18 等效电阻增加的漏电通路 Fig. 18 Equivalent resistance increased leakage path |

改进的DICE单元加入了2个NMOS控制管, 为了节省面积开销, NMOS控制管的宽长比可取最小值; 与DICE单元相比, 面积开销增加12.5%.具体的数值如表 1所示.读写延时在2章已有分析, 延时的具体值如表 1所示.表中, Anorm为归一化面积, P为功耗, tread为读延时, twrite为写延时.

| 表 1 不同的SRAM单元的延时、功耗、面积开销对比 Table 1 Comparison of delay, power consumption, areaoverhead between different SRAM cells |

(1) 在不同的温度、电压等环境变量条件下, 对DICE单元的读写操作进行模拟仿真, 得到在T=398 K, Vdd=0.9 V的环境条件下, 单元经历108 s老化后, 写静态噪声容限和读噪声容限的退化率分别为4.6%和77.3%.DICE单元老化失效的首要原因都是随BTI效应影响增加的读干扰造成的读故障.

(2) 对传统DICE单元的读写端口做出改进, 利用DICE单元抗单点SEU的特性, 通过加入控制MOS管使传输管隔离, 进而消除了单元在读状态和半选择状态时遭受的干扰, 提升了读稳定性和使用寿命,直接减少了经过108 s的老化后22.6%的读失效率.

(3) 加入的控制管有效地隔断了读或半选择状态时字线对节点的充电路径, 使DICE单元的2个存储节点在读或半选状态时的容单点SEU能力提高.同时, 控制管的加入为单元额外提供了6.25%的功耗削减, 降低了存储单元的工作温度, 有助于进一步增强老化抗性.

和传统的DICE单元相比, 本文提出的改进型DICE单元在抗辐射、尤其抗老化能力方面有明显的优势, 克服了传统DICE单元由于静态噪声容限不足带来的可靠性问题.未来的进一步设计将主要集中在SRAM的外围电路上, 以弥补改进方案在读写速度方面带来的折损.

| [1] | DODD P E, MASSENGILL L W. Basic mechanisms and modeling of single-event upset in digital microelectronics[J]. IEEE Transactions on Nuclear Science, 2003, 50(3): 583–602. DOI:10.1109/TNS.2003.813129 |

| [2] | El-MALEH A H, DAUD K A K. Simulation-based method for synthesizing soft error tolerant combinational circuits[J]. IEEE Transactions on Reliability, 2015, 64(3): 935–948. DOI:10.1109/TR.2015.2440234 |

| [3] | TOURE G, HUBERT G, CASTELLANI-COULIEK, et al. Simulation of single and multi-node collection: Impact on SEU occurrence in nanometric SRAM cells[J]. IEEE Transactions on Nuclear Science, 2011, 58(3): 862–869. DOI:10.1109/TNS.2011.2110662 |

| [4] | CALIN T, NICOLAIDIS M, VELAZCO R. Upset hardened memory design for submicron CMOS technology[J]. IEEE Transactions on Nuclear Science, 1996, 43(6): 2874–2878. DOI:10.1109/23.556880 |

| [5] | JAHINUZZAMAN S, RENNIE D, SACHDEV M. A soft error tolerant 10T SRAM bit-cell with differential read capability[J]. IEEE Transactions on Nuclear Science, 2009, 56(3): 3768–3773. |

| [6] | SHAH J S, NAIM D, SACHDEV M. A 32 kb macro with 8T soft error robust SRAM cell in 65-nm CMOS[J]. IEEE Transactions on Nuclear Science, 2015, 62(3): 1367–1374. DOI:10.1109/TNS.2015.2429589 |

| [7] | LI L X, LI Y Q, MA Y, et al. A novel asymmetrical SRAM cell tolerant to soft errors [C]//Canadian Conference on Electrical and Computer Engineering. Halifax: IEEE, 2015: 1403-1408. |

| [8] | D'ALESSIO M, OTTAVI M, LOMBARDI F. Design of a nanometric CMOS memory cell for hardening to a single event with a multiple node upset[J]. IEEE Transactions on Device and Materials Reliability, 2014, 14(1): 127–132. DOI:10.1109/TDMR.2012.2206814 |

| [9] |

周恒, 李磊. 一种加固SRAM单元DDICE及外围电路设计[J].

微电子学与计算机, 2015, 32(5): 68–72.

ZHOU Heng, LI Lei. A hardened SRAM cell-DDICE and peripheral circuits design[J]. Microelectronics and Computer, 2015, 32(5): 68–72. |

| [10] | RAJAEI R, ASGARI B, TABANDEH M, et al. Design of robust SRAM cells against single-event multiple effects for nanometer technologies[J]. IEEE Transactions on Device and Materials Reliability, 2015, 15(3): 429–436. DOI:10.1109/TDMR.2015.2456832 |

| [11] | BANSAL A, RAO R, KIM J J, et al. Impacts of NBTI and PBTI on SRAM static/dynamic noise margins and cell failure probability[J]. Microelectronics Reliability, 2009, 49(6): 642–649. DOI:10.1016/j.microrel.2009.03.016 |

| [12] | YANG H I, CHUANG C T, HWANG W. Impacts of NBTI and PBTI on power-gated SRAM with high-k metal-gate devices [C]//IEEE International Symposium on Circuits and Systems. Taipei: IEEE, 2009: 377-380. |

| [13] | WANG K, CHEN L, YANG J. An ultra-low power fault tolerant SRAM design in 90 nm CMOS Electrical and Computer Engineering [C]//Canadian Conference on Electrical and Computer Engineering. St. John's: IEEE, 2009: 1076-1079. |

| [14] | CHANG L, MONTOYE R K, NAKAMURA Y, et al. An 8T SRAM for variability tolerance and low-voltage operation in high performance caches[J]. IEEE Journal of Solid-State Circuits, 2008, 43(4): 956–963. DOI:10.1109/JSSC.2007.917509 |

| [15] |

沈婧, 薛海卫. 基于DICE结构的SRAM抗辐照加固设计[J].

电子与封装, 2016, 16(3): 26–30.

SHEN Jing, XUE Hai-wei. Design of radiation hardened SRAM based on DICE[J]. Electronics and Packaging, 2016, 16(3): 26–30. |

| [16] | LEE Z C, HO K M, KONG Z H, et al. NBTI/PBTI-aware WWL voltage control for half-selected cell stability improvement[J]. IEEE Transactions on Circuits and Systems Ⅱ: Express Briefs, 2013, 60(9): 602–606. DOI:10.1109/TCSII.2013.2273731 |

| [17] | RENNIE D, LI D, SACHDEV M, et al. Performance, metastability, and soft-error robustness trade-offs for flip-flops in 40 nm CMOS[J]. IEEE Transactions on Circuits and SystemsⅠ: Regular Papers, 2012, 59(8): 1626–1634. DOI:10.1109/TCSI.2012.2206505 |

| [18] | YANG H I, HWANG W, CHUANG C T. Impacts of NBTI/PBTI and contact resistance on power-gated SRAM with high-k metal-gate devices[J]. IEEE Transactions on Very Large Scale Integration Systems, 2011, 19(7): 1192–1204. DOI:10.1109/TVLSI.2010.2049038 |

| [19] | YANG H I, YANG S C, HWANG W, et al. Impacts of NBTI/PBTI on timing control circuits and degradation tolerant design in nanoscale CMOS SRAM[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2011, 58(6): 1239–1251. DOI:10.1109/TCSI.2010.2096112 |

| [20] | Predictive technology model [EB/OL]. [2011-06-01]. http://www.eas.asu.edu/~ptm. |

| [21] | NAPHADE T, VERMA P, GOEL N, et al. DC/AC BTI variability of SRAM circuits simulated using a physics-based compact model [C]//IEEE International Reliability Physics Symposium. Waikoloa HI: IEEE, 2014: CA.2.1-CA.2.8. |

| [22] | 李广林, 张杰, 商中夏, 等. 适应于动态电压频率调整的抗辐照SRAM设计[J]. 微电子学与计算机, 2017, 34(4): 33–38. |

| [23] |

方海涛. 高速低功耗嵌入式SRAM的设计[D]. 武汉: 华中科技大学, 2012.

FANG Hai-tao. Design of high speed low power embedded SRAM. Wuhan: Huazhong University of Science and Technology, 2012. |