2. 北京交通大学 电气工程学院, 北京 100044;

3. 国网浙江省电力公司, 浙江 杭州 310007

2. College of Electrical Engineering, Beijing Jiao Tong University, Beijing 100044, China;

3. State Grid Zhejiang Electric Power Corporation, Hangzhou 310007, China

卫星一次电源系统对于输入输出电流的纹波、效率以及功率密度都具有很高的要求[1-4].加底推挽变换器(add-on push-pull converter, APPC)具有连续的输入输出电流、高效率、高功率密度, 因此适用于卫星一次电源系统[5-7].加底变换器将传统隔离型变换器的低电位端通过加底支路连接至输入电源正端, 属于输入并联输出串联变换器, 其输出电压由隔离型变换器的输出电压和输入电压叠加而成.由于大部分功率通过加底支路直接传送至负载, 加底变换器具有高效率[8-9], 且具有连续的输入输出电流, 减小了滤波器体积重量, 提高了功率密度.

由于加底支路的存在, 输入电压扰动通过加底支路及输出电容Cin直接对输出电压产生影响, 因此加底变换器的音频衰减率性能较差.对于输入电压纹波无法忽略的场合, 需要对音频衰减率进行研究.例如多脉波整流电路的后级变换器存在低频纹波(频率由脉波数决定), 又如航天功率调节器(PCU)工作在太阳电池阵提供负载所需功率并通过蓄电池充电调节器给蓄电池充电时, 由于母线电压受顺序开关分流调节器(S3R)的调节, 且多采用滞环控制[10-11], 母线电压即蓄电池充电调节器的输入电压存在低频纹波(频率由S3R的频率决定)[12].此外, 加底支路的存在相当于在原变换器的输入阻抗两端并了负载阻抗, 从而减小了加底变换器的输入阻抗.当加底变换器作为级联系统中的负载变换器时, 需要对输入阻抗进行研究, 以防止源变换器与负载变换器阻抗耦合, 从而影响系统的稳定性.

吴涛等[13]分析影响Buck变换器输入阻抗的因素.刘青等[14]分析输入电压扰动对输出的影响.Ejea最早提出加底全桥变换器, 并对该变换器的损耗及小信号模型进行分析[6].基于加底全桥变换器, 该学者提出三电容结构, 建立了考虑杂散参数下的小信号模型, 发现由杂散参数造成的谐振峰严重恶化了音频衰减率, 通过合理设计输出电容可以降低此谐振峰, 从而实现对闭环音频衰减率的优化[15].即使优化后, 音频衰减率仍存在谐振峰.还没有学者对加底变换器的输入阻抗特性进行分析, 也没有学者尝试通过改变电容结构以提高加底变换器的闭环特性.

若把加底变换器看成由隔离型变换器和加底支路两个模块输入并联输出串联而成, 则输出电容为三电容结构.若把隔离型变换器和加底支路看成一个整体, 则加底变换器的输出侧只需一个电容.可见, 加底变换器可能存在三电容和单电容两种结构.由于推挽变换器具有母线电压特性优、驱动简单等特点, 本文研究APPC的闭环特性, 比较两种电容结构的优劣.

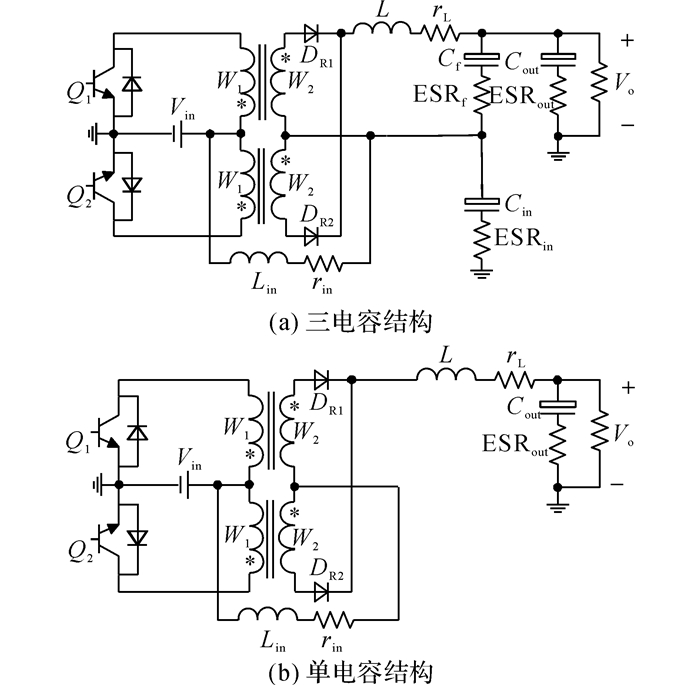

1 APPC的被控对象小信号模型如图 1(a)、(b)所示分别为考虑加底支路杂散电感Lin、杂散电阻rin、电感等效串联电阻rL、电容ESR等杂散参数下基于三电容结构与单电容结构的APPC.令变压器匝比为N=W1/W2, 两个MOS管的占空比之和为D.两种电容结构下APPC的电压增益均为1+D.下面对两种输出电容结构的APPC进行建模.

|

图 1 两种输出电容结构的APPC Fig. 1 APPC with two types of output capacitor structures |

由于APPC的小信号特性与Buck变换器相似, 可以得到

| $ {G_{{\rm{id}}}}\left( s \right) = \frac{{{{\hat i}_{\rm{L}}}\left( s \right)}}{{\hat d\left( s \right)}}\left| {_{{{\hat v}_{{\rm{in}}}}\left( s \right) = 0}} \right. = \frac{{{V_{{\rm{in}}}}}}{{N{Z_{\rm{f}}}\left( s \right)}}. $ | (1) |

|

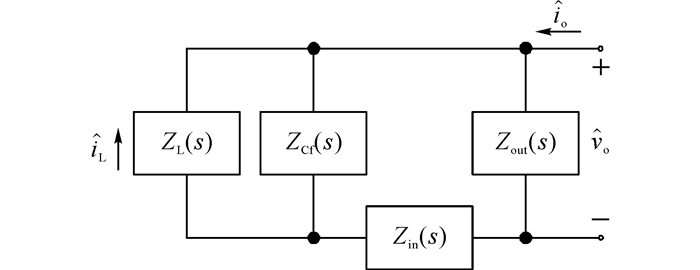

图 2

|

式中:

| $ {Z_{\rm{f}}}\left( s \right) = {Z_{\rm{L}}}\left( s \right) + \frac{{{Z_{{\rm{Cf}}}}\left( s \right)\left( {{Z_{{\rm{in}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)} \right)}}{{{Z_{{\rm{Cf}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)}}. $ |

根据输出电压对电感电流的传递函数LPF(s), 可得控制对象Gvd(s).

| $ {\rm{LPF}}\left( s \right) = \frac{{{{\hat v}_{\rm{o}}}\left( s \right)}}{{{{\hat i}_{\rm{L}}}\left( s \right)}} = \frac{{{Z_{{\rm{Cf}}}}\left( s \right){Z_{{\rm{out}}}}\left( s \right)}}{{{Z_{{\rm{Cf}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)}}. $ | (2) |

由于APPC的输入电流扰动

| $ \begin{array}{l} {G_{{\rm{id}}\left( g \right)}}\left( s \right) = \frac{{{{\hat i}_{{\rm{in}}}}\left( s \right)}}{{\hat d\left( s \right)}}\left| {_{{{\hat v}_{{\rm{in}}}}\left( s \right) = 0}} \right. = \\ \frac{{{I_{{\rm{out}}}}}}{N} + {G_{{\rm{id}}}}\left( s \right)\left\{ {\frac{D}{N} + \frac{{{Z_{{\rm{Cf}}}}\left( s \right){Z_{{\rm{in}}}}\left( s \right)}}{{{Z_{{\rm{Lin}}}}\left( s \right)\left[ {{Z_{{\rm{Cf}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right]}}} \right\}. \end{array} $ | (3) |

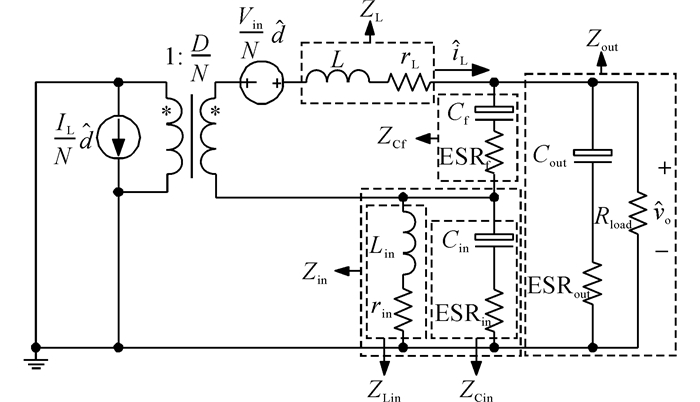

当

|

图 3

|

对于功率调节器支路, 由图 3(a)可得电感电流对输入电压的传递函数YolZVS(s)以及输出电压对输入电压的传递函数FolZVS(s).

| $ {Y_{{\rm{olZVS}}}}\left( s \right) = \frac{{{{\hat i}_{{\rm{LZVS}}}}}}{{{{\hat v}_{{\rm{in}}}}}} = \frac{D}{{N{Z_{\rm{f}}}\left( s \right)}}, $ | (4) |

| $ \begin{array}{l} {F_{{\rm{olZVS}}}}\left( s \right) = \frac{{{{\hat v}_{{\rm{oZVS}}}}}}{{{{\hat v}_{{\rm{in}}}}}} = {Y_{{\rm{olZVS}}}}\left( s \right) \cdot {\rm{LPF}}\left( s \right) = \\ \;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\frac{D}{{N{Z_{\rm{f}}}\left( s \right)}} \cdot \frac{{{Z_{{\rm{Cf}}}}\left( s \right){Z_{{\rm{out}}}}\left( s \right)}}{{{Z_{{\rm{Cf}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)}}. \end{array} $ | (5) |

输入电流扰动

| $ \begin{array}{l} {G_{{\rm{ig}}\left( g \right)1}}\left( s \right) = \frac{{{{\hat v}_{{\rm{inZVS}}}}\left( s \right)}}{{{{\hat v}_{{\rm{in}}}}\left( s \right)}}{{\rm{|}}_{\hat d\left( s \right) = 0}} = \\ \frac{{\frac{{{D^2}{Z_{{\rm{Lin}}}}\left( s \right)}}{{{N^2}{Z_{\rm{f}}}\left( s \right)}}\left[ {{Z_{{\rm{Cf}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right] + \frac{{D{Z_{{\rm{Cf}}}}\left( s \right){Z_{{\rm{in}}}}\left( s \right)}}{{N{Z_{\rm{f}}}\left( s \right)}}}}{{{Z_{{\rm{Lin}}}}\left( s \right)\left[ {{Z_{{\rm{Cf}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right]}}. \end{array} $ | (6) |

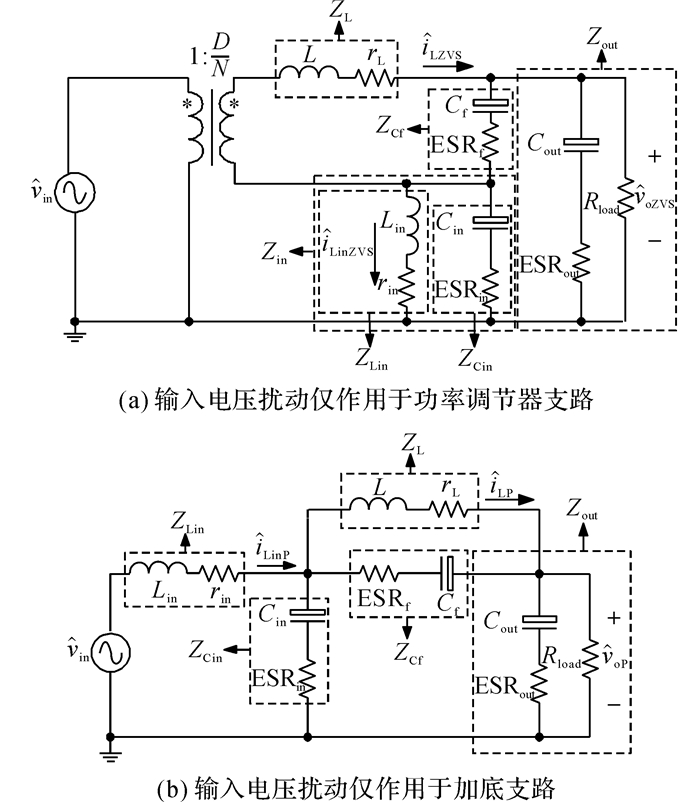

对于加底支路, 令

| $ \begin{array}{l} {Z_1}\left( s \right) = \frac{{{Z_{\rm{L}}}\left( s \right){Z_{{\rm{Cf}}}}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{Cf}}}}\left( s \right)}},{Z_2}\left( s \right) = {Z_1}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right),\\ {Z_3}\left( s \right) = \frac{{{Z_{\rm{2}}}\left( s \right){Z_{{\rm{Cin}}}}\left( s \right)}}{{{Z_{\rm{2}}}\left( s \right) + {Z_{{\rm{Cin}}}}\left( s \right)}}. \end{array} $ |

由图 3(b)可得电感电流对输入电压的传递函数YP(s)以及输出电压对输入电压的传递函数FP(s).

| $ {Y_{\rm{P}}}\left( s \right) = \frac{{{{\hat v}_{{\rm{LP}}}}\left( s \right)}}{{{{\hat v}_{{\rm{in}}}}\left( s \right)}} = \frac{{{Z_1}\left( s \right){Z_3}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right){Z_2}\left( s \right)\left[ {{Z_{{\rm{Lin}}}}\left( s \right) + {Z_3}\left( s \right)} \right]}}, $ | (7) |

| $ \begin{array}{l} {F_{\rm{P}}}\left( s \right) = \frac{{{{\hat v}_{{\rm{oP}}}}\left( s \right)}}{{{{\hat v}_{{\rm{in}}}}\left( s \right)}} = \\ {Y_{\rm{P}}}\left( s \right){\rm{LP}}{{\rm{F}}_{\rm{P}}}\left( s \right) = {Y_{\rm{P}}}\left( s \right){Z_{{\rm{out}}}}\left( s \right)\left[ {1 + \frac{{{Z_{\rm{L}}}\left( s \right)}}{{{Z_{{\rm{Cf}}}}\left( s \right)}}} \right]. \end{array} $ | (8) |

输入电流扰动

| $ \begin{array}{l} {G_{{\rm{ig}}\left( g \right)2}}\left( s \right) = \frac{{{{\hat i}_{{\rm{inP}}}}\left( s \right)}}{{{{\hat v}_{{\rm{in}}}}\left( s \right)}}\left| {_{\hat d\left( s \right) = 0}} \right. = \\ \frac{{\frac{D}{N}{Z_1}\left( s \right){Z_3}\left( s \right) + {Z_{\rm{L}}}\left( s \right){Z_2}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right){Z_2}\left( s \right)\left[ {{Z_{{\rm{Lin}}}}\left( s \right) + {Z_3}\left( s \right)} \right]}}. \end{array} $ | (9) |

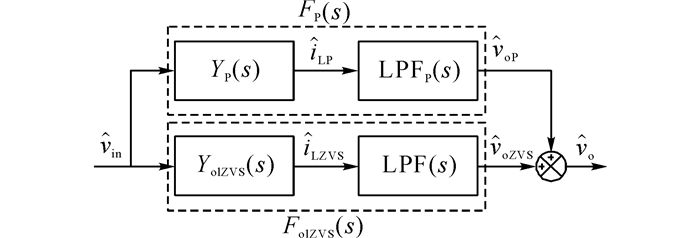

根据叠加定理可知, 输入电流对输入电压的传递函数Gig(g)(s)等于Gig(g)1(s)与Gig(g)2(s)的叠加, 开环音频衰减率Gvg(s)等于FP(s)与FolZVS(s)的叠加, 如图 4所示.

| $ {G_{{\rm{ig}}\left( g \right)}}\left( s \right) = {G_{{\rm{ig}}\left( g \right)1}}\left( s \right){G_{{\rm{ig}}\left( g \right)2}}\left( s \right), $ | (10) |

| $ {G_{vg}}\left( s \right) = {F_{\rm{P}}}\left( s \right) + {F_{{\rm{olZVS}}}}\left( s \right). $ | (11) |

|

图 4 开环音频衰减率框图 Fig. 4 Open-loop system audio susceptibility |

当

| $ {Z_4}\left( s \right) = {Z_1}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right),{Z_5}\left( s \right) = \frac{{{Z_4}\left( s \right){Z_{{\rm{out}}}}\left( s \right)}}{{{Z_4}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)}}, $ |

|

图 5

|

开环输出阻抗

| $ {Z_{{\rm{open}}}}\left( s \right) = \frac{{{{\hat v}_{\rm{o}}}\left( s \right)}}{{{{\hat i}_{\rm{o}}}\left( s \right)}}\left| {_{{{\hat v}_g}\left( s \right) = 0,\hat d\left( s \right) = 0}} \right. = {Z_5}\left( s \right). $ |

负载电流到滤波电感电流的传递函数为

| $ {G_{{\rm{ii}}}}\left( s \right) = \frac{{{{\hat i}_{\rm{L}}}\left( s \right)}}{{{{\hat i}_{\rm{o}}}\left( s \right)}}\left| {_{{{\hat v}_g}\left( s \right) = 0,\hat d\left( s \right) = 0}} \right. = - \frac{{{Z_1}\left( s \right){Z_5}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right){Z_4}\left( s \right)}}. $ | (12) |

基于以上方法, 可以得到基于单电容结构的APPC的各项传递函数如下所示:

| $ {G_{{\rm{id}}}}\left( s \right) = \frac{{{{\hat i}_{\rm{L}}}\left( s \right)}}{{\hat d\left( s \right)}}\left| {_{{{\hat v}_{{\rm{in}}}}\left( s \right) = 0}} \right. = \frac{{{V_{{\rm{in}}}}}}{{N\left[ {{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right]}}, $ | (13) |

| $ {G_{{\rm{id}}\left( g \right)}}\left( s \right) = \frac{{{{\hat i}_{{\rm{in}}}}\left( s \right)}}{{\hat d\left( s \right)}}\left| {_{{{\hat v}_{{\rm{in}}}}\left( s \right) = 0}} \right. = \frac{{{I_{{\rm{out}}}}}}{N} + {G_{{\rm{id}}}}\left( s \right)\left( {1 + \frac{D}{N}} \right), $ | (14) |

| $ {Y_{{\rm{olZVS}}}}\left( s \right) = \frac{{{{\hat i}_{{\rm{LZVS}}}}}}{{{{\hat v}_{{\rm{in}}}}}} = \frac{D}{{N\left[ {{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right]}}, $ | (15) |

| $ {F_{{\rm{olZVS}}}}\left( s \right) = \frac{{{{\hat v}_{{\rm{oZVS}}}}}}{{{{\hat v}_{{\rm{in}}}}}} = \frac{{D{Z_{{\rm{out}}}}\left( s \right)}}{{N\left[ {{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right]}}, $ | (16) |

| $ {Y_{\rm{P}}}\left( s \right) = \frac{{{{\hat i}_{{\rm{LP}}}}}}{{{{\hat v}_{{\rm{in}}}}}} = \frac{1}{{{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)}}, $ | (17) |

| $ {F_{\rm{P}}}\left( s \right) = \frac{{{{\hat v}_{{\rm{oP}}}}}}{{{{\hat v}_{{\rm{in}}}}}} = \frac{{{Z_{{\rm{out}}}}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)}}, $ | (18) |

| $ {Z_{{\rm{open}}}}\frac{{{{\hat v}_{\rm{o}}}\left( s \right)}}{{{{\hat i}_{\rm{o}}}\left( s \right)}}\left| {_{{{\hat v}_g}\left( s \right) = 0,\hat d\left( s \right) = 0}} \right. = \frac{{\left[ {{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right)} \right]{Z_{{\rm{out}}}}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)}}, $ | (19) |

| $ {G_{{\rm{ii}}}}\left( s \right) = \frac{{{{\hat i}_{\rm{L}}}\left( s \right)}}{{{{\hat i}_{\rm{o}}}\left( s \right)}}\left| {_{{{\hat v}_g}\left( s \right) = 0,\hat d\left( s \right) = 0}} \right. = \frac{{ - {Z_{{\rm{out}}}}\left( s \right)}}{{{Z_{\rm{L}}}\left( s \right) + {Z_{{\rm{in}}}}\left( s \right) + {Z_{{\rm{out}}}}\left( s \right)}}. $ | (20) |

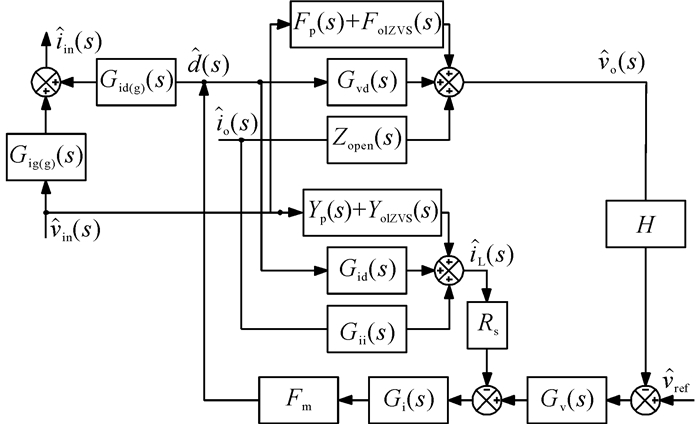

基于推导得到的被控对象小信号模型, 可以得到考虑杂散参数下APPC的闭环小信号模型, 如图 6所示.

|

图 6 平均电流控制的闭环小信号框图 Fig. 6 Conductance control block diagram |

由图 3(b)可知, 当输入电压扰动

主电路电感L与输出电容Cout谐振(谐振峰2频率为

求环路增益以及闭环输出阻抗时, 需要令

为了验证以上分析, 选取一工况对APPC的闭环特性进行分析, 主电路参数按照42 V全调节母线PCU中最常见的工况进行设置, 如表 1所示.表中,L、rL分别为电感的感值和导通电阻,Lm为变压器的激磁电感.

| 表 1 主电路参数 Table 1 Power converter specifications |

电感的选择按照试验工况下电感电流的纹波小于35%, 根据式(21) 计算设计可得, 电感选为102.2 μH.

| $ \Delta {i_{\rm{L}}} = \frac{{\left( {{V_{\rm{o}}} - {V_{{\rm{in}}}}} \right)\left( {0.5 - D} \right){T_{\rm{s}}}}}{L}. $ | (21) |

三电容结构的等效输出电容C3=Cout+CfCin/(Cf+Cin), 单电容结构的等效输出电容C1=Cout.根据文献[10]中对于三电容结构容值选取的结论:Cf对于系统的音频衰减率有重要的影响, 若Cf较小, 并且保证Cout大致等于等效输出电容, 则系统的音频衰减率得到改善.Cf与Cin的串联支路的电容远小于Cout, 因此三电容结构下几乎所有的电感电流交流分量都经过输出电容Cout, 输出电压纹波的表达式可以近似为

| $ \Delta {V_{\rm{o}}} = \frac{1}{{{C_{{\rm{out}}}}}} \times \frac{1}{2} \times \frac{{\Delta {I_{\rm{L}}}}}{2} \cdot \frac{{{T_{\rm{s}}}}}{2} + \Delta {I_{\rm{L}}} \cdot {\rm{ES}}{{\rm{R}}_{{\rm{out}}}}. $ | (22) |

为了满足输出电压纹波率小于0.5%的航天器电源标准, 将三电容结构的电容选择如下:Cf=1.43 μF、ESRf=373 mΩ、Cin=98.2 μF、ESRin=7 mΩ、Cout=960 μF、ESRout=19.1 mΩ.为了保证两种电容结构下的等效输出容值基本相等, 将单电容结构的电容选择如下:Cout=960 μF、ESRout=19.1 mΩ.通过测量得到PCB板加底支路的杂散电感为Lin=201.2 nH, 杂散电阻为rin=3 mΩ.

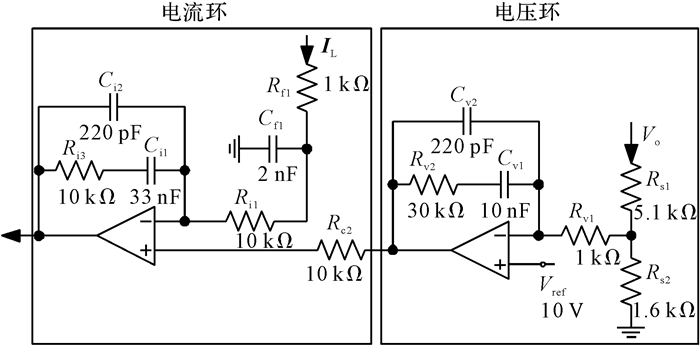

APPC采用双环控制, 其中外环为电压环, 内环为电流环.电压采样系数H=1, 电流采样系数Rs=0.8, 三角波调制系数Fm=1/1.8, 电流环、电压环控制器均采用双极点单零点控制器.为了保证电流环环路增益的截止频率高于电压环, 且电压环环路增益的幅值裕度大于10 dB, 相角裕度大于45°, 电流环、电压环控制器参数设计如图 7所示.

|

图 7 电流环、电压环控制器参数 Fig. 7 Parameters of voltage loop and current loop |

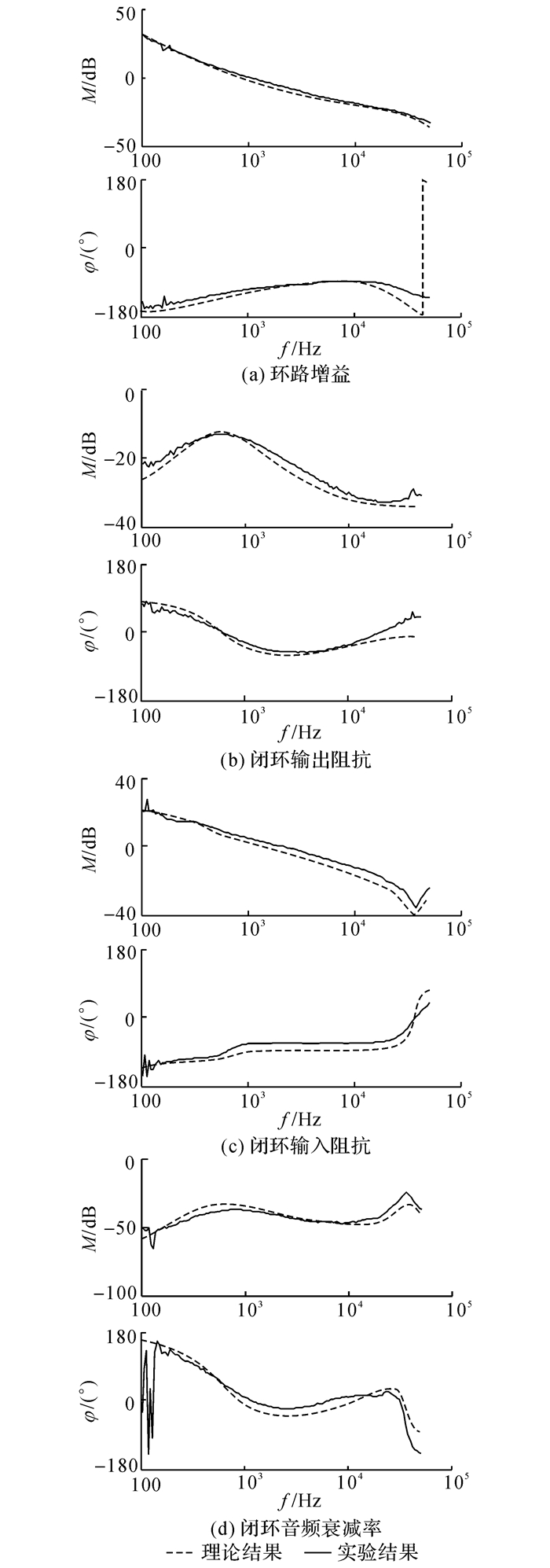

基于以上条件, 对基于三电容结构与单电容结构的APPC的闭环特性(环路增益、闭环输出阻抗、闭环音频衰减率、闭环输入阻抗)分别进行比较、分析.其中, 环路增益表征系统的动态响应以及稳定裕度, 闭环输入、输出阻抗表征级联系统的稳定性, 闭环音频衰减率表征抗输入电压扰动的能力.

2.1 环路增益令

| $ {T_{{\rm{vl}}}}\left( s \right) = \frac{{{G_{{\rm{vd}}}}\left( s \right){F_{\rm{m}}}{G_{\rm{i}}}\left( s \right)H{G_{\rm{v}}}\left( s \right)}}{{1 + {G_{{\rm{id}}}}\left( s \right){F_{\rm{m}}}{G_{\rm{i}}}\left( s \right){R_{\rm{s}}}}}. $ | (23) |

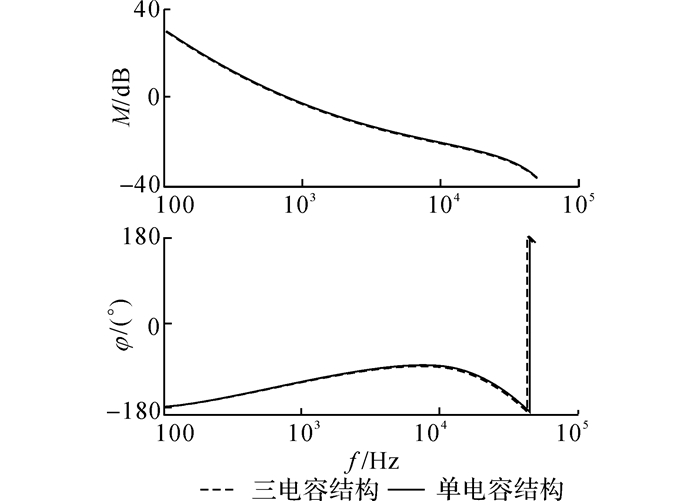

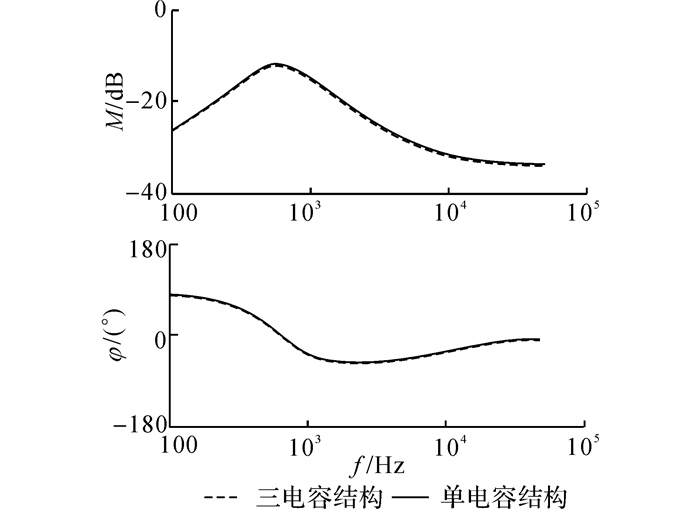

由式(23) 可得, APPC环路增益的Bode图如图 8所示.图中,M、φ分别为幅值和相角.单电容结构与三电容结构的环路增益一致.在本文配置的参数下, 两种结构下的稳定裕度均能达到大于10 dB和45°的指标.

|

图 8 环路增益Bode图 Fig. 8 Loop gain of voltage loop |

令

| $ \begin{array}{l} {Z_{{\rm{oc}}}}\left( s \right) = \frac{{{{\hat v}_{\rm{o}}}\left( s \right)}}{{{{\hat i}_{\rm{o}}}\left( s \right)}} = \\ \;\;\;\;\;\;\frac{{{Z_{{\rm{open}}}}\left( s \right)\left[ {1 + {T_i}\left( s \right)} \right] - \frac{{{T_{\rm{i}}}\left( s \right){G_{{\rm{ii}}}}\left( s \right){G_{{\rm{vd}}}}\left( s \right)}}{{{G_{{\rm{id}}}}\left( s \right)}}}}{{1 + {T_i}\left( s \right) + {T_{\rm{v}}}\left( s \right)}}. \end{array} $ | (24) |

式中:

由式(24) 可得, APPC闭环输出阻抗的Bode图如图 9所示.可知, 两种结构的闭环输出阻抗基本一致.

|

图 9 闭环输出阻抗Bode图 Fig. 9 Closed-loop output impedance |

令

| $ {Z_{{\rm{inc}}}}\left( s \right) = \frac{1}{{{G_{{\rm{ig}}\left( {\rm{g}} \right)}}\left( s \right) - \frac{{{G_{{\rm{id}}\left( g \right)}}\left( s \right){G_{\rm{i}}}\left( s \right){F_{\rm{m}}}\left\{ {{R_{\rm{s}}}\left[ {{Y_{\rm{p}}}\left( s \right) + {Y_{{\rm{olZVS}}}}\left( s \right)} \right] + {G_{\rm{v}}}\left( s \right)H\left[ {{F_{\rm{p}}}\left( s \right) + {F_{{\rm{olZVS}}}}\left( s \right)} \right]} \right\}}}{{1 + {T_i}\left( s \right) + {T_{\rm{v}}}\left( s \right)}}}}. $ | (25) |

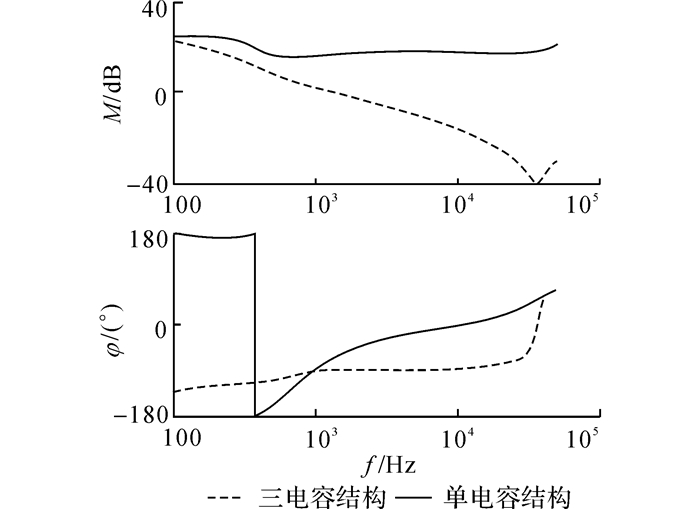

闭环输入阻抗越大, 说明前、后级阻抗耦合的可能性越小, 级联运行越容易稳定.根据式(25) 可得两种电容结构下闭环输入阻抗的Bode图, 如图 10所示.

|

图 10 闭环输入阻抗Bode图 Fig. 10 Closed-loop input impedance |

单电容结构的闭环输入阻抗整体高于三电容结构, 并且随着频率的升高, 单电容结构的优势越明显.在35.8 kHz附近, 三电容结构的闭环输入阻抗出现谐振峰, 此时的闭环输入阻抗最低.谐振峰对应的频率为

| $ {f_{\rm{r}}} = \frac{1}{{2{\rm{\pi }}\sqrt {{L_{{\rm{in}}}}\left[ {{C_{{\rm{in}}}} + \frac{{{C_{\rm{f}}}{C_{{\rm{out}}}}}}{{{C_{\rm{f}}} + {C_{{\rm{out}}}}}}} \right]} }}. $ | (26) |

可见, 此谐振峰由加底支路的杂散电感以及输出电容谐振产生.由以上分析可知, 单电容结构的闭环输入阻抗在全频率范围均明显优于三电容结构.

2.4 闭环音频衰减率令

| $ \begin{array}{l} {G_{{\rm{vgcl}}}}\left( s \right) = \frac{{{{\hat v}_{\rm{o}}}\left( s \right)}}{{{{\hat i}_{{\rm{in}}}}\left( s \right)}} = \\ \frac{{{F_{\rm{p}}}\left( s \right) + {F_{{\rm{olZVS}}}}\left( s \right) + {Y_{\rm{p}}}\left( s \right){R_{\rm{s}}}{G_{{\rm{id}}}}\left( s \right){F_{\rm{m}}}{G_{\rm{i}}}\left( s \right)\left[ {{\rm{LP}}{{\rm{F}}_{\rm{p}}}\left( s \right) - {\rm{LPF}}\left( s \right)} \right]}}{{1 + {R_{\rm{s}}}{G_{{\rm{id}}}}\left( s \right){F_{\rm{m}}}{G_{\rm{i}}}\left( s \right) + H{G_{\rm{v}}}\left( s \right){G_{{\rm{id}}}}\left( s \right){F_{\rm{m}}}{G_{\rm{i}}}\left( s \right){\rm{LPF}}\left( s \right)}}. \end{array} $ | (27) |

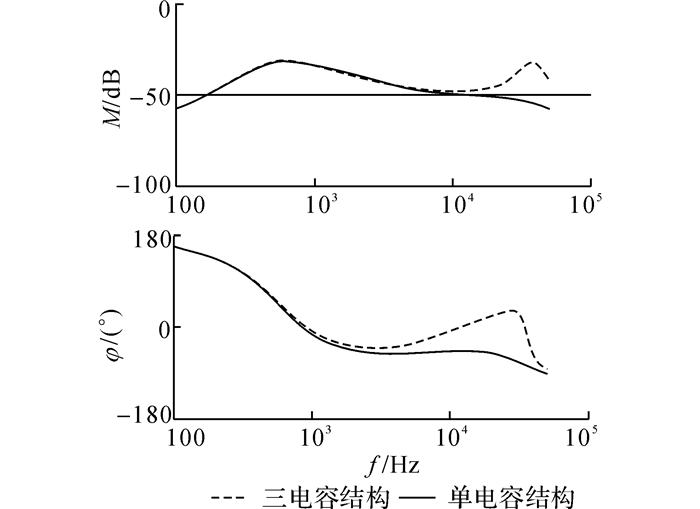

闭环音频衰减率越小, 说明输入电压扰动对于输出电压的影响越小, 系统的抗扰性能越好.根据式(27) 可得两种电容结构下闭环音频衰减率的Bode图, 如图 11所示.

|

图 11 闭环音频衰减率Bode图 Fig. 11 Closed-loop audio susceptibility |

比较两种结构的闭环音频衰减率可以发现:两种结构的低频段音频衰减率一致, 但是三电容结构中Lin与输出电容谐振引起的谐振峰会恶化高频段的闭环音频衰减率.单电容结构优于三电容结构.

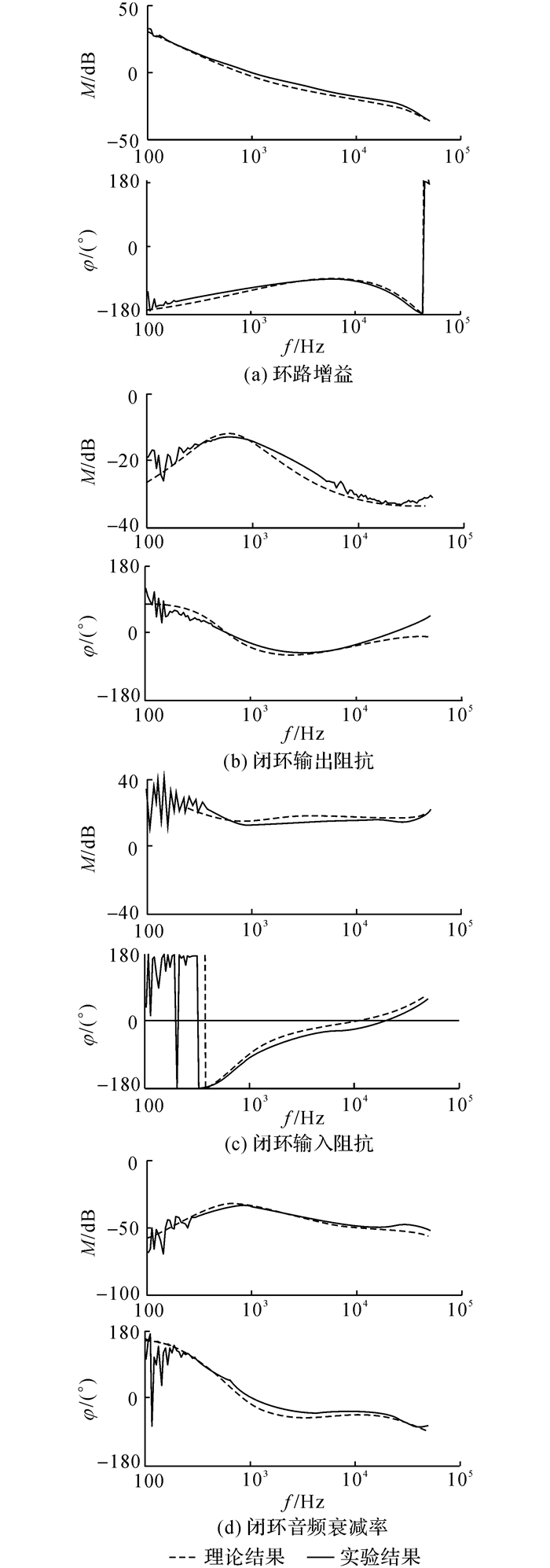

3 实验验证基于表 1的主电路参数搭建一台实验样机, 如图 12所示.使用N4L牛顿网络分析仪PSM1735对单电容与三电容结构的APPC的传递函数进行实验测试, 实验结果分别如图 13、14所示.

|

图 12 加底推挽变换器试验样机 Fig. 12 Experiment platform of APPC |

|

图 13 基于单电容结构APPC的测试结果 Fig. 13 Measured results for APPC with single-capacitor structure |

|

图 14 基于三电容结构APPC的测试结果 Fig. 14 Measured results for APPC with three-capacitor structure |

由图 13(a)、14(a)可知, 系统环路增益的实验结果与理论分析结果一致, 并且单电容与三电容结构下的环路增益一致, 证明小信号模型的正确性.如图 13(b)、14(b)所示为两种电容结构下的闭环输出阻抗, 可见实验结果与理论分析结果基本重合, 电容结构的变化未影响闭环输出阻抗.如图 13(c)、14(c)所示为闭环输入阻抗, 如图 13(d)、14(d)所示为闭环音频衰减率.除了由于扫频变压器的影响造成100~200 Hz的实验结果存在偏差外, 实验结果与理论分析结果基本一致, 三电容结构中的谐振峰对应的频率吻合较好.由此可见, 输出电容Cin、Cf的引入提供了谐振回路, 使得Lin与输出电容产生谐振, 具体体现为闭环输入阻抗与闭环音频衰减率中的谐振峰, 恶化了系统的输入阻抗与音频衰减率.

4 结语由于直接连接至输出的加底支路存在, APPC具有效率高、输入输出电流连续的优势, 并且控制对象与Buck变换器类似, 采用普通的环路设计方法可以获得较优的动态性能.加底支路的存在对系统的音频衰减率以及输入阻抗均存在不良的影响, 本文建立考虑杂散参数下基于单电容和三电容两种结构的APPC的小信号模型, 并对环路增益、闭环输出阻抗、闭环输入阻抗、闭环音频衰减率进行分析.根据理论分析结果以及实验结果证明, 两种电容结构下的环路增益以及闭环输出阻抗一致, 但单电容结构的闭环输入阻抗和闭环音频衰减率均优于三电容结构, 因此单电容结构能够满足级联系统稳定性以及输入低频纹波抑制的要求.

| [1] | DENZINGER W, DIETRICH W.Generic 100V/high power bus conditioning[C]//The 7th European Space Power Conference. Italy: ES Agency, 2005. |

| [2] | SOUBRIER L, PATRICK B. High performance BDR for the PCU of alphabus[C]//The 8th European Space Power Conference. France: ES Agency, 2008. |

| [3] | HANSEN M M. Power conditioning unit for bepicolombo transfer module[C]//The 8th European Space Power Conference. France: ES Agency, 2008. |

| [4] | SOUBRIER L, TREHET E. High power PCU for alphabus: PSR100V[C]//The 9th European Space Power Conference. France: ES Agency, 2011. |

| [5] |

陈骞, 郑琼林, 李艳. 单电感电流连续型推挽类拓扑的推衍和特性研究[J].

中国电机工程学报, 2013, 33(6): 85–92.

CHEN Qian, ZHENG Trillion Q, LI Yan. Derivation and characterization of single-inductor push-pull based topologies with continuous currents[J]. Proceedings of the CSEE, 2013, 33(6): 85–92. |

| [6] | EJEA J B, FERRERES A, SANCHIS E, et al. Optimized topology for high efficiency battery discharge regulator[J]. IEEE Transactions on Aerospace and Electronic System, 2008, 44(4): 1511–1519. DOI:10.1109/TAES.2008.4667726 |

| [7] |

陈骞, 郑琼林, 李艳. 一种高效率蓄电池放电调节器的优化设计与损耗分析[J].

电工技术学报, 2013, 28(8): 224–232.

CHEN Qian, ZHENG Trillion Q, LI Yan. Parameter design and power loss analysis of a high efficiency battery discharge regulator[J]. Transactions of China Electrotechnical Society, 2013, 28(8): 224–232. |

| [8] | AYYANAR R, MOHAN N. Novel soft-switching DC-DC converter with full ZVS-range and reduced filter requirement——part Ⅰ: regulated-output applications[J]. IEEE Transactions on Power Electronics, 2001, 16(2): 184–192. DOI:10.1109/63.911142 |

| [9] | LI Yan, ZHENG Trillion Q, CHEN Qian. Research on high efficiency non-Isolated push-pull converters with continuous current in solar-battery systems[J]. Journal of Power Electronics, 2014, 14(3): 432–443. DOI:10.6113/JPE.2014.14.3.432 |

| [10] |

李芳, 游小杰, 李艳. 过调节现象对顺序开关分流调节器的影响[J].

太阳能学报, 2014, 35(11): 2119–2126.

LI Fang, YOU Xiao-jie, LI Yan. Influences of double section functioning on the sequential switching shunt regulator[J]. Acta Energiae Solaris Sinica, 2014, 35(11): 2119–2126. DOI:10.3969/j.issn.0254-0096.2014.11.008 |

| [11] |

杨岳枫. 高效顺序开关分流调节器研究[J].

电源技术, 2016, 40(6): 1284–1285.

YANG Yue-feng. Research on efficient sequential shunt switching regulator[J]. Chinese Journal of Power Sources, 2016, 40(6): 1284–1285. |

| [12] |

贾鹏宇, 郑琼林, 李艳. 级联系统中Buck充电调节器前馈控制方法研究[J].

电工技术学报, 2014, 29(10): 134–140.

JIA Peng-yu, ZHENG Trillion Q, LI Yan. Research on feedforward control of buck circuit as battery charge regulator in cascade system[J]. Transactions of China Electrotechnical Society, 2014, 29(10): 134–140. DOI:10.3969/j.issn.1000-6753.2014.10.017 |

| [13] |

吴涛, 阮新波. 分布式供电系统中负载变换器的输入阻抗分析[J].

中国电机工程学报, 2008, 28(12): 20–25.

WU Tao, RUAN Xin-bo. Input impedance analysis of load converters in the distributed power system[J]. Proceedings of the CSEE, 2008, 28(12): 20–25. DOI:10.3321/j.issn:0258-8013.2008.12.004 |

| [14] |

刘青, 张东来. 抑制输入扰动的Buck变换器控制方法[J].

电工技术学报, 2011, 26(4): 93–99.

LIU Qing, ZHANG Dong-lai. An improved control method of Buck converter to reject input-disturbance[J]. Transactions of China Electrotechnical Society, 2011, 26(4): 93–99. |

| [15] | EJEA J B, FERRERES A, SANCHIS E, et al. Study of the audio susceptibility in parallel power processing with a high-power topology[J]. IEEE Transactions on Power Electronics, 2009, 24(10): 2323–2337. DOI:10.1109/TPEL.2009.2022757 |