皮纳卫星有重量轻、功耗低、研制周期短、造价和发射成本低等特点, 已经逐步应用在对地观测、轨道试验、测控等多个领域[1-2].目前, 全世界在研、已发射的数量已经超过300颗[3].

ZDPS-2(浙大皮星2号)是浙江大学研制的第二代皮纳卫星, 为我国首颗应用型皮纳卫星, 具备很高的功能密度, 已于2015年9月20日搭载CZ-6火箭发射成功.卫星综合电子系统采用一体化设计思想[4-5], 集成了星间测距、实时定轨、姿态控制与轨道控制、星务管理、电源管理、热控管理等功能, 系统外部接口较多;并管理分布在大型展开机构上的84路载荷单元.且载荷任务对系统有较高实时性要求, 给系统的设计带来了新的挑战.

在目前已发射的皮纳卫星中, 如Zhang等[6-7]描述的国内首颗公斤级皮卫星ZDPS-1A, 廖文和等[8-9]描述的国外主流CubeSat, 其系统的扩展方式主要通过CAN\I2C等总线实现.这种总线方式虽易于扩展, 但使用时CPU需要以串行的方式对总线上挂载的下位机逐个访问, 通信速率受限于下位机, 实际的外设访问总速率通常仅有几十Kbps到几百Kbps, 在通信上会消耗大量CPU时间.叶伟松等[10]描述了“天巡一号”皮卫星综合电子系统设计, 虽然通过FPGA实现了所有接口扩展, 但外设交互机制上还是通过CPU轮询, 通信效率较低.以上设计在多外设、多载荷的卫星系统中, 均难以满足实时性需求.

为满足ZDPS-2任务实时性需求, 须寻找有效的综合电子系统设计方法.本系统采用低功耗的SRAM型FPGA, 利用其丰富的逻辑资源, 设计基于独占式DMA的多路并行通信机制, 可快速完成多路平台外设交互;并分析影响载荷任务实时性的关键因素, 通过数据混编传输以及链式DMA机制实现多路分布式单元实时采集下传.对系统中关键器件进行抗辐射[11-12]加固;并通过系统层面的安全性设计, 提高容错与故障恢复能力, 保证系统的可靠性.

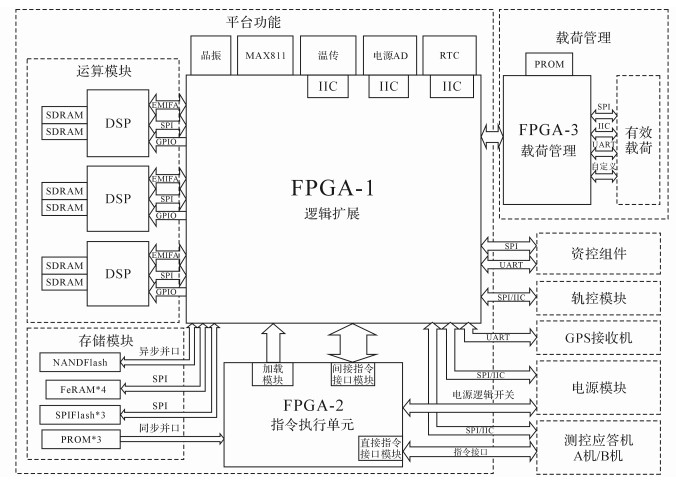

1 综合电子系统总体架构ZDPS-2综合电子系统总体架构如图 1所示.主要由运算模块、存储模块、逻辑扩展模块、指令执行单元与载荷管理模块组成.

|

图 1 ZDPS-2综合电子系统(IES)架构设计 Fig. 1 Architecture design and block diagram of integrated electronic system (IES) in ZDPS-2 |

系统核心器件为工业级FPGA及DSP.其中FPGA-1与FPGA-3使用的是Xilinx低功耗、低成本的Spartan6系列, FPGA-2使用的是Actel低功耗AX反熔丝系列;DSP则采用了TI公司高性能TMS320C6000系列.

运算模块由3片互为备份的数字信号处理器(digital signal processor, DSP)芯片组成.DSP通过其片上高速的外存访问接口(EMIFA)连接FPGA-1, 并通过后者实现对所有外设的访问.

FPGA-1、FPGA-3实现系统与所有外设包括载荷之间的接口.FPGA-2为指令执行单元, 采用抗辐射能力强的反熔丝FPGA[13-14], 实现指令容错编码、看门狗等功能, 是整星的最高可靠性单元.

ZDPS-2综合电子系统具有以下指标要求:外设访问总速率大于10 Mbps, 84路分布式载荷单元数据采集频度达100 Hz, 从采集至地面不超过40 ms时延, 平均无故障时间500 h等.

在本系统中, 运算速率、存储容量、功耗与重量等指标主要由上述硬件设计保证;在该硬件平台之上, 通过FPGA的逻辑架构设计, 保证平台外设交互的实时性、多路分布式载荷数据采集下传的实时性以及系统整体的可靠性.下文将描述为保证这些性能而使用的关键技术.

2 高实时性的平台外设交互机制ZDPS-2综合电子系统需提供如表 1所示的通信接口, 以实现与所有外设之间的数据交互.系统所有外设的控制与数据交互, 均由一个DSP完成.星上完整的任务执行周期为1 s, DSP在每秒内需要处理全部计算任务以及与所有外设交互任务.如表 1所示, 系统外设较多, 且接口通信速率不高, 在“CPU+总线控制器+外设”的系统架构下, DSP需要逐个访问外设并且会消耗大量CPU时间.为满足计算需求, 每秒仅能分配100 ms的CPU时间用于外设交互;然而根据数据量与规定速率计算, DSP逐个访问所有外设, 需消耗565 ms;此外, 部分外设交互需要同步进行, 如姿控系统12路敏感器的采样要求时间一致性优于10 ms, 然而DSP逐个访问各个敏感器, 最早与最晚完成的时间差达33 ms.

| 表 1 ZDPS-2综合电子系统(IES)外部接口需求 Table 1 External interface requirements of integrated electronic system (IES) in ZDPS-2 |

对于外设数量较少的系统, 可以通过DSP片上DMA, 降低CPU处理负担.然而有限的片上DMA资源无法支持ZDPS-2中大量外设交互任务.不仅如此, 片上DMA亦无法保证多外设同步交互的一致性.对此, 通过设计一种基于FPGA的多路并行的独占式DMA来解决上述问题.下文首先介绍单路独占式DMA模块的结构、特点、与优势;接着描述了多路独占式DMA并行扩展时遇到的问题及解决方法.

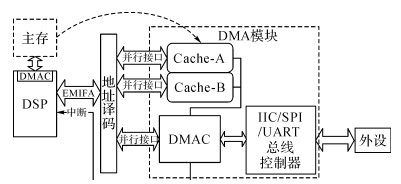

2.1 独占式DMA的结构本系统根据DSP片上DMA设计思想, 设计了如图 2所示结构的独占式DMA.该DMA由DMAC、总线控制器以及两片Cache组成.

|

图 2 FPGA中设计的DMA模块 Fig. 2 DMA module implemented in FPGA |

独占式DMA与标准片上DMA的不同之处在于:DSP片上DMA直接使用DSP的整块主存作为数据缓存;独占式DMA则利用FPGA内独立小块BRAM资源实现的2片Cache作为该DMA通道的独立数据缓存.独立式DMA除了可降低CPU时间占用率, 还给本系统带来如下好处.

1) DSP片上DMA实现的是主存与外设之间的数据传输, 但传输过程中存在CPU与DMAC共同访问主存的情况, 需要按优先级轮流访问, 会在一定程度上降低CPU的性能;而独占式DMA利用FPGA内小块BRAM资源实现2片Cache作为该DMA通道的独立数据缓存, 彻底避免了主存访问冲突的问题.

2) 独占式DMA的缓存为具有独立访问接口的存储单元, 具有真正并行访问能力, 无须分时访问.并且各DMA模块相互独立, 在实现多路DMA时, 无需复杂的仲裁器来处理多个DMA请求冲突的问题, 从而简化了设计.

理论上通过简单扩展多个DMA模块, 就可实现与所有外设的并行通信.但直接扩展会存在问题.

1) 由于DSP对DMA的访问是通过EMIFA进行的, 实现多路的DMA就需要更多寻址空间, 两者之间成正比关系.按设计需求实现表 1所对应的57路DMA需要约44 KB寻址空间, 但EMIFA最大仅提供32 KB, 限制了可扩展DMA的数量.

2) DMA传输完成后, 通过DSP片上外部中断反馈给DSP, 然而DSP受片上资源限制, 并不能支持54路外部中断.

故实现DMA多路扩展, 必须解决上述2个问题.2.2节描述了问题解决的技术途径.

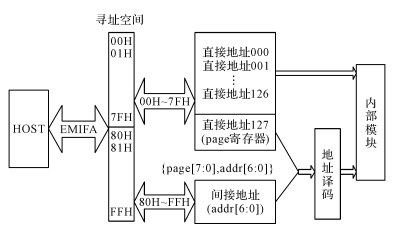

2.2 独占式DMA的多路并行扩展 2.2.1 基于分页地址的寻址空间扩展该方法可将每256字节的EMIFA寻址空间, 扩展为32 KB, 扩大128倍, 可解决EMIFA寻址空间不足的问题.256字节寻址空间分为直接寻址(00H~7FH)与间接寻址(80H~FFH)两部分, 容量分别为128 Byte.

直接寻址的特征为MSB=0, 作为特殊功能寄存器(SFR)寻址;间接寻址特征为MSB=1, 作为缓存(Cache)寻址, 当MSB=1时, 低7位地址称作偏移地址bias[6:0].在SFR中设置一个称之为页地址的寄存器page[7:0], 该值与bias[6:0]可拼接扩展成15位地址, 扩展后的寻址范围为32 KB.FPGA根据MSB的值, 执行对应的寻址操作.DSP则根据以下方法进行SFR与Cache的访问:1) DSP访问SFR:直接访问00H~7FH这段地址即可;2) DSP访问Cache:根据Cache地址, 换算出页地址与偏移地址,先将页地址的值写入page寄存器, 再访问偏移地址即可.基于FPGA的分页地址的具体设计如图 3所示.

|

图 3 基于FPGA的分页地址设计 Fig. 3 Segment addressing design based on FPGA |

可见扩展主要是通过间接寻址.然而间接寻址会增加额外的访问时间消耗, 降低通信效率.但本设计将有高频访问需求的SFR均设计为直接寻址, 并不存在访问效率降低的问题;仅将大容量Cache设计为间接寻址, 且Cache在本系统中均为顺序访问的方式, 每访问1个page(128 Byte)后才需要更新page的值, 额外消耗时间的百分比仅为

| $ {\eta _{{\rm{ext}}}} = \frac{1}{{{N_{{\rm{page}}}}}} = 0.78\% . $ |

故通过该方式, 系统以0.78%的额外时间消耗为代价, 可将EMIFA上32 KB寻址空间扩展到4 MB, 满足44 KB的应用需求.

2.2.2 分级合成的中断系统在并行通信机制中, 每个外设都有其独占DMA, 传输完成后通过DSP片上外部中断接口反馈DSP.然而DSP支持的外部中断数量很有限, 需要将多路中断合并到较少数量.

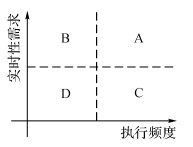

合并时需要按照中断优先级排序, 影响优先级的主要因素有任务的实时性需求以及执行频度.对此, 按图 4将所有中断分为4个优先级, 同级的所有中断合成一路后输出给DSP.

|

图 4 综合电子系统(IES)任务优先级分类原则 Fig. 4 Principle of task priority classification in IES |

根据卫星实际任务, 载荷任务的执行频度、实时性需求均最高, 设计为A类;为保证地面对卫星的控制, 上行链路相关任务实时性需求也较高, 但其频度相对较低, 设计为B类;下行链路实时性需求低于上行链路, 但其执行频度相对较高, 设计为C类;其余任务实时性需求、执行频度均相对较低, 设计为D类.按上述原则, 将所有任务划分为4个等级, 如表 2所示.

| 表 2 综合电子系统(IES)任务中断优先级划分 Table 2 Classification of task interrupt prioritization in IES |

通过合理的分级合成之后, 外部中断数量减少到4个, 满足DSP的需求;并且通过了整星测试, 各项任务实时性均满足需求, 未出现某个中断不响应或丢失的情况.

至此, 系统完整实现了基于独占式DMA的多路并行通信机制, 解决了实时性问题,其性能见第5章实验结果.此外, 由于系统具备了并行通信的能力, 按每种接口的规定速率计算, 根据表 1可知, 系统串行接口与外设交互总速率可达:

| $ {N_1} \cdot {V_{{\rm{spi}}}} + {N_2} \cdot {V_{{\rm{uart}}}} + {N_3} \cdot {V_{{\rm{i2c}}}} = 14.06\;{\rm{Mbps}} $ |

最高速率达到不小于10 Mbps的水平, 满足了指标需求.若简单采用“CPU+总线控制器+外设”的设计, 外设访问总速率小于max(Vspi, Vuart, Vi2c)=500 Kbps.

3 高实时性的分布式载荷数据采集机制传统皮纳卫星任务多为对地成像、大气探测之类, 并无高实时性要求, 可以将采集存储过程与下发过程分开进行.ZDPS-2载荷为一个如图 5所示的多路分布式单元, 每10 ms就需要完成一次对分布在展开机构上84个载荷单元的数据采集, 从采集完成到下发至地面不超过40 ms.这对资源十分有限的皮纳卫星来说, 主要在通信、数据处理各个环节均存在限制.

|

图 5 ZPDS-2及其展开机构结构图 Fig. 5 Structure of ZDPS-2 and corresponding deployment mechanism |

1) 通信环节的限制:为适应ZPDS-2展开机构的结构布局, 系统不能采用84路并行的设计, 而必须采用6组I2C总线连接84个分布的单元, 并通过6路独占式DMA分别通信.载荷单元的MCU仅支持最大120 Kbps的通信速率, 等价于10 ms中每个MCU最多可以传输10 Byte数据.载荷数据由100 Hz的Ⅰ类数据与10 Hz的Ⅱ类数据组成.经压缩后其数据量如下:Ⅰ类数据9 Byte/1MCU, Ⅱ类数据8 Byte/1MCU.如果不采取措施, 那么Ⅰ类数据与Ⅱ类数据同时传送时数据量为8+9=17 Byte, 超过了10 Byte的限制.

2) 数据处理环节的限制:在数据处理环节, DSP需要完成中断响应、存储等任务.每路DMA要在10 ms内完成与本组串联的14个MCU的通信, DSP则需要配合DMA实现该通信过程:即每间隔Δt=10/14=0.7 ms就要响应一次DMA中断、并发起下一次DMA传输.然而存储的最小单元为NAND Flash的1个Page, 耗时为7~8 ms, 且不可被打断.因此, 一旦DSP处于存储过程, 就无法配合DMA继续与后续MCU通信.故受存储时间限制, DSP无法兼顾频繁的中断响应任务与耗时长的存储任务.

可知,系统针对多路分布式单元采集下传机制的设计, 实际上是要在通信速率受限、数据处理频度高的情况下解决整条链路的实时性问题,主要通过数据混编传输以及链式DMA机制来解决, 保证多路分布式单元数据采集的实时性要求.

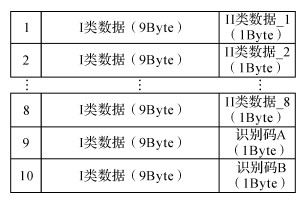

3.1 通信环节实时性保证通过数据混编通信的方法保证两类数据完整传输,混编方式如图 6所示.

|

图 6 数据混合编组方法示例 Fig. 6 Example of mixed data grouping method |

该方法将Ⅱ类数据按字节拆分, 与Ⅰ类数据进行组合.当Ⅰ类数据传输1~8帧时, 每帧附加1字节的Ⅱ类数据;当Ⅰ类数据传输9~10帧时, 每帧附加1字节固定的识别码.如此循环.

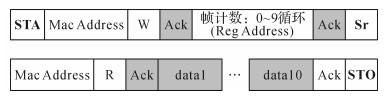

此方法有一缺陷, 当通信错误丢失其中一帧时, 会导致Ⅱ类数据无法拼接恢复, 而且会导致后续的Ⅱ类数据全部错位.在MCU返回的数据中增加1 Byte帧计数即可解决该问题, 但在通信速率限制下, 并无足够的帧空间为每个MCU增加1字节数据,在此利用了I2C协议中空闲的寄存器地址段,用于存放帧计数,修改后的协议格式如图 7所示.

|

图 7 将寄存器地址段作为帧计数 Fig. 7 Employ register address as frame counter |

进行如下的校验设计:通信时MCU先判断寄存器地址段的帧计数, 再根据帧计数返回对应的数据;DSP读取数据后, 根据两处进行校验:1)1~10的帧计数;2) 通过这2个校对信息,接收端可检测出丢失的数据帧编号,并能正确拼接出来后续数据,从而避免了数据错位后导致的后续Ⅱ类数据无法解析.采取校验设计前、后,数据传输的出错概率对比如表 3所示.表中, t为运行时长, m1为Ⅱ类数据发送量, m2为Ⅱ类数据成功解析量, η为数据丢失率.

| 表 3 校验措施对Ⅱ类数据的影响 Table 3 Effect on type Ⅱ data by verification measures |

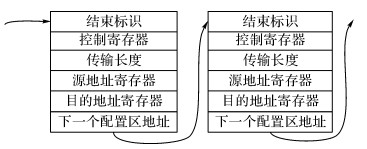

系统通过改进独占式DMA, 以降低DSP需要响应的中断频率, 即增大DSP响应中断的间隔时间, 使得NAND Flash可以在该时间间隔内完成存储, 从而保证数据处理环节的实时性.

在此设计链式结构的虚拟DMA, 以实现多个任务的预设.DSP可将多个传输任务设置在DMAC的配置区, 每个配置区包含传输数据长度、传输控制位、源地址/目的地址等信息, 以及下一个配置区的地址.链式DMA的控制器结构如图 8所示.

|

图 8 支持任务预设的链式DMAC结构 Fig. 8 Structure of DMAC based on link list for tasks presetting |

当DMAC完成一次传输时, 会根据下一个配置区的地址所指向的值, 自动开启下一次传输.若指向的结束标志为TRUE, 则传输结束.对于每组载荷MCU的数据传输需求, DSP只要预先设置好长度为14的链表, 即可由DMAC自动实现与14个MCU的通信.

这样对于每路DMA, 10 ms内DSP需要响应的中断次数由14次降低为1次.故DMA中断的时间间隔由原先的10/14=0.7 ms增加到了10/1=10 ms, 大于NAND Flash存储耗时(7~8 ms), 满足其存储对时间的需求.

通过以上方法, 系统可每10 ms采集到84路载荷单元的数据, 保证了采集数据并下发至地面100 Hz的需求.

3.3 数据下传ZDPS-2数传模式的速率为250 Kbps, 并以连续的数传帧下发, 以维持星地通信链路不中断.每帧传输时间为16 ms.为提高数传帧利用率并简化设计, 系统每20 ms通过数传帧下发一次载荷数据.对于传输延时来说, 最好的情况只需要等待一个数传帧的传输时间即可传到地面, 即16 ms;在最坏的情况下,需要额外等待一个数传帧的传输时间, 即32 ms.

至此, 基于以上方法, 系统保证了载荷数据100 Hz的采集频度以及不超过40 ms时延的要求.

4 抗辐射加固设计系统基于工业级器件设计, 包括1500万门大规模SRAM型FPGA.但这些器件并非针对航天应用环境, 抗辐射指标较低.皮纳卫星体积小、资源有限, 无法亦无须对所有器件进行加固保护, 仅对关键器件进行抗辐射加固.系统采用三模冗余(triple modular redundancy, TMR)技术加固DSP代码存储与加载功能;并通过周期性重配置对SRAM型FPGA进行抗辐射加固.

4.1 DSP的TMR加载DSP代码存储的可靠性对综合电子系统乃至整星至关重要.皮纳卫星研制周期短, 软件难以在早期成熟, 故不适合采用反熔丝器件烧写代码.采用可重复擦写的SPI Flash则必须对其进行加固处理.

考虑到SPI Flash体积、功耗均较低, 为提高可靠性, 系统在此采用TMR加载设计.代码存放在3片相同的SPI Flash中, 加载时DSP发出加载时序, FPGA捕捉该时序, 提前从3片SPI Flash读取并进行表决, 发送给DSP.如此循环, 直到加载完成.

空间高能粒子使存储器件产生单粒子翻转,这一现象称为离散事件, 假设每1 bit存储单元发生单粒子事件的概率是σ, 那么单位时间内每m bit存储单元中的i个bit发生单粒子翻转的概率为

| $ {p_{(i, m)}} = C_m^i{\sigma ^i}{(1-\sigma )^{m-i}}. $ | (1) |

那么对于N bit存储单元, 不采用TMR与采用TMR之后的出错概率之比为

| $ \tau = \frac{{1-p{'_N}}}{{1-p{'_{{\rm{TMR}}}}}}. $ | (2) |

式中:p′N(σ)=(1-σ)N为不采用TMR时N bit存储单元的可靠性, 当采用TMR之后冗余存储的N bit数据的可靠性为

| $ p{'_{{\rm{TMR}}}}(\sigma ) = {[{p_{(0, 3)}} + {p_{(1, 3)}}]^N}. $ |

在卫星运行的低地球轨道中[15-16], 浮栅型器件单粒子翻转的概率大约在(10-11, 10-10), DSP软件代码占用空间约为600 KByte即N=600×1 024×8, 在σ不同取值下出错概率比较如表 4所示.

| 表 4 不同单粒子翻转概率下的代码出错概率 Table 4 Error probability under different probability of single event upset |

可见, 对于600 KByte大小的软件代码, 采用TMR加载技术后, 出错概率降低了9个数量级, 可靠性大大提高.

4.2 SRAM型FPGA定时重配置由于SRAM型FPGA中配置字的存储介质采用静态内存, 易受到空间辐射影响而发生存配置位翻转等事件[17].在空间应用应对其进行加固, 才能保证系统的可靠性.ZDPS-2综合电子系统除了在HDL软件设计上对重要功能进行三模冗余表决、对状态机编码进行EDAC设计之外, 还在架构设计上对SRAM型FPGA进行了保护.

1) FPGA的配置代码存放在一次性烧写的PROM中, 该PROM使用反熔丝工艺制造, 具备很高的抗辐射能力.

2) FPGA加载方式使用从模式加载, 通过反熔丝指令执行单元产生加载时序, 并通过SelectMap接口完成对FPGA的加载, 同时通过该接口实现对FPGA的周期性重配置.重配置的周期可根据0.1~0.5的TMTBF(TMTBF=1/(N·r))估算而设置, 其中TMTBF为发生1 bit单粒子翻转的时间间隔, N为可配置存储器的位数, r为单粒子翻转率.

系统采用的FPGA配置位N=4 122 Kbit, 在低地球轨道环境中, SRAM型器件单粒子翻转率可取r=1×10-7·bit-1/d, 则有

| $ {T_{{\rm{MTBF}}}} = \frac{1}{{N \cdot r}} = 2.4\;{\rm{d}}. $ | (3) |

系统采用6 h的重配置周期, 可在FPGA发生配置位翻转后及时刷新内部SRAM, 减少或消除翻转事件的影响, 提高了系统的可靠性.

此外, 综合电子系统进行了整星层面的安全性设计, 具备容错、检错与故障恢复能力.主要包括:1) 指令接口中Hamming编码设计, 可实现指令一位纠错, 两位检错;2) 针对多机备份的看门狗设计;3) 监控整星能源状态, 根据能源状态对卫星工作模式进行切换管理, 以保证卫星在轨正常运行;4) 低功耗模式设计, 使卫星可在不充电的情况下待机15 d以上, 以应对能源极端不足的特殊情况.

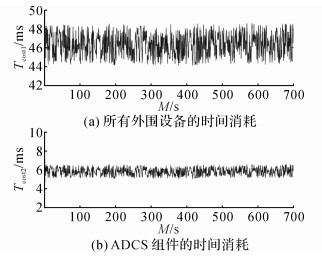

5 试验结果 5.1 实时性试验结果ZDPS-2综合电子系统通过并行通信机制, 降低了外设交互中DSP的时间占用.DSP工作中以1 s为周期, 测试时每周期内对所有外设进行一轮访问;并在DSP程序主循环中加入DSP与外设交互中的时间消耗统计, 统计所有姿控敏感器从开始采样到采样完成的时间消耗, 并将结果通过遥测数据下传.在此选取一段测试数据说明效果, 如图 9所示.图中,M为主循环计数, 循环周期为1 s;Tcost1为DSP与外设通信消耗的时间,可以看出, 在每秒中DSP与外设通信时间均小于50 ms, 满足了小于100 ms的需求;Tcost2为姿控所有敏感器采样时间消耗, 约6 ms, 满足10 ms的时间一致性需求.

|

图 9 综合电子系统数字信号处理器(DSP)与外设以及姿控系统部件交互的时间消耗 Fig. 9 Time consumption of communication between DSP (digital signal processor) and peripherals/ADCS (attitude determination and control system) components |

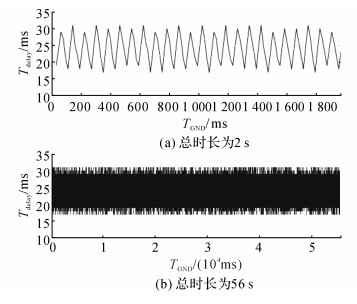

此外, 载荷单元数据要求从采集到下传不超过40 ms时延.综合电子系统在数据采集完成后会打上一个时间戳, 地面数传设备接收到每一帧星上数据, 都会记录接收时间.故可以将数据包中解析出来的时间戳与对应的地面记录时间作对比, 以验证载荷数据到地面的时延.

选取一段接收的数据进行处理, 结果如图 10所示.图中TGND为地面站的钟面时间, Tdelay为数据下发至地面的时延(即地面时间减去数据包中解析出的时间).可以看出, 时延Tdelay呈周期波动, 满足小于40 ms的需求.

|

图 10 载荷数据下传至地面的传输时延 Fig. 10 Transmission delay of payload datadown to groud |

通过各项测试及可靠性增长试验, 验证了ZDPS-2综合电子系统的功能正确性与可靠性.这些试验包括接口容差容错测试, 高低温循环、热真空等不同环境应力下的测试, 以及总时长为200 h、每5 s随机发送指令的老练试验.在各项测试中, 系统均表现稳定, 且功能正确、性能满足需求, 未出现死机情况.此外对DSP的TMR加载进行专项测试:烧写2份相同的正确代码, 并将第3份代码存储区域整片擦除, 然后进行加载试验, 重复50次, 结果均加载成功.

在卫星发射后的在轨运行阶段, 地面持续接收到了星上遥测数据以及数传数据.结果表明:ZDPS-2综合电子系统连续正常运行时间超过了5 m, 完成了载荷及各项试验, 实现了500 h的无故障运行时间指标.

6 结语本文从ZDPS-2的任务需求出发, 通过FPGA软件化的设计, 实现了所有外设的快速访问, 使54路外设接口总通信时间降低为不到50 ms, 并使姿控敏感器采样的时间一致性从33 ms优化到6 ms;实现了多路分布式载荷100 Hz的数据采集, 并满足下传至地面不超过40 ms时延的需求.通过关键器件抗辐射加固以及系统层面的安全性设计, 保证了系统500 h的无故障运行时间.在轨运行结果表明:本系统的功能、性能、可靠性均满足任务要求.

| [1] | YOON S, SHIN Y, JEON J, et al. Analysis of the charged particle radiation effect for a CubeSat transiting from Earth to Mars[J]. Current Applied Physics: the Official Journal of the Korean Physical Society, 2014, 14(4): 575–581. |

| [2] | PIATTONI J, CANDINI G P, PEZZI G, et al. PlasticCubesat: An innovative and low-cost way to perform applied space research and hands-on education[J]. Acta Astronautica, 2012, 81(2): 419–429. DOI:10.1016/j.actaastro.2012.07.030 |

| [3] |

赵炜渝, 白保存, 金仲和, 等. 皮纳卫星应用与特点分析[J].

国际太空, 2012, 81(2): 419–429.

ZHAO Wei-Yu, BAI Bao-cun, JIN Zhong-he, et al. Application and characteristic analysis of pico/nano satellite[J]. Space International, 2012, 81(2): 419–429. |

| [4] |

王九龙. 卫星综合电子系统现状和发展建议[J].

航天器工程, 2007, 16(5): 68–73.

WANG Jiu-long. Development state and thought of the satellite synthesized electronic system[J]. Spacecraft Engineering, 2007, 16(5): 68–73. |

| [5] |

乐浪, 李明峰, 王君, 等. 卫星综合电子系统的FDIR研究与设计[J].

计算机工程与设计, 2014, 35(7): 2607–2611.

LE Lang, LI Ming-feng, WANG Jun, et al. Research and design of FDIR techniques for satellite avionics[J]. Computer Engineering and Design, 2014, 35(7): 2607–2611. |

| [6] | ZHANG Y, ZHENG Y M, YANG M, et al. New technique: design and implementation of the highly-reliable, low-cost housekeeping system in the ZDPS-1A pico-satellite[J]. Journal of Zhejiang University: Science C, 2012, 13(2): 83–89. DOI:10.1631/jzus.C1100079 |

| [7] | XIANG T, MENG T, WANG H, et al. Design and on-orbit performance of the attitude determination and control system for the ZDPS-1A pico-satellite[J]. Acta astronautica, 2012, 77(8/9): 182–196. |

| [8] |

廖文和. 立方体卫星技术发展及其应用[J].

南京航空航天大学学报, 2015, 47(6): 792–797.

LIAO Wen-he. A survey of Cubesat technology development and applications[J]. Journal of Nanjing University of Aeronautics and Astronautics, 2015, 47(6): 792–797. |

| [9] |

袁少钦, 于晓洲, 周军, 等. 基于国产CPU的立方星星计算机系统设计[J].

计算机工程, 2014, 40(6): 16–19.

YUAN Shao-qin, YU Xiao-zhou, ZHOU Jun, et al. Design of cubesat on-board computer system based on domestic CPU[J]. Computer Engineering, 2014, 40(6): 16–19. |

| [10] |

叶伟松, 刘海颖, 陈志明, 等. "天巡一号"微小卫星数据综合系统设计与在轨性能评估[J].

南京航空航天大学学报, 2012, 44(6): 797–802.

YE Wei-song, LIU Hai-ying, CHEN Zhi-ming, et al. DIS system design and in-orbit performance assessment of NHTX-1 SAT[J]. Journal of Nanjing University Aeronautics and Astronautics, 2012, 44(6): 797–802. |

| [11] | SCHWARZ R, THEIL S. A fault-tolerant on-board computing and data handling architecture incorporating a concept for failure detection, isolation, and recovery for the SHEFEX Ⅲ navigation system [C] // 13th International Conference on Space Operations. Pasadena: SpaceOps, 2014: 1874. |

| [12] |

张钰, 郁发新, 郑阳明, 等. 皮卫星星务管理系统容错设计[J].

宇航学报, 2007, 28(6): 1753–1757.

ZHANG Yu, YU Fa-xin, ZHENG Yang-ming, et al. Fault tolerance design of pico-satellite's house keeping system[J]. Journal of Astronautics, 2007, 28(6): 1753–1757. |

| [13] |

王刚, 李平, 李威, 等. 反熔丝的研究与应用[J].

材料导报, 2011, 25(11): 30–33.

WANG Gang, LI Ping, LI Wei, et al. Research and application of antifuse[J]. Materials Review, 2011, 25(11): 30–33. |

| [14] | Microsemi Corporation, RTAX-S/SL and RTAX-DSP Radiation-Tolerant FPGAs Data Sheet [EB/OL]. (2010-08-01)[2015-12-01]. http://www.microsemi.com/document-portal/doc_download/130713-rtax-s-sl-and-rtax-dsp-radiation-tolerant-fpgas-datasheet. |

| [15] |

贺朝会. 空间轨道单粒子翻转率预估方法研究[J].

空间科学学报, 2001, 21(3): 266–273.

HE Chao-hui. Study of methods for predicting SEU rate in space orbits[J]. Chinese Journal of Space Science, 2001, 21(3): 266–273. |

| [16] |

贺朝会, 耿斌杨, 海亮, 等. 浮栅ROM与SRAM的辐射效应比较分析[J].

电子学报, 2003, 31(8): 1260–1262.

HE Chao-hui, GENG Bin, YANG Hai-liang, et al. Comparison and analysis of radiation effects between floating gate ROMs and SRAMs[J]. Acta Electronica Sinica, 2003, 31(8): 1260–1262. |

| [17] |

邢克飞, 杨俊, 王跃科, 等. Xilinx SRAM型FPGA抗辐射设计技术研究[J].

宇航学报, 2007, 28(1): 123–129.

XING Ke-fei, YANG Jun, WANG Yue-ke, et al. Study on the anti-radiation technique for xilinx SRAM-based FPGA[J]. Journal of Astronautics, 2007, 28(1): 123–129. |