2. 复旦大学 微电子学院,上海 201203

2. College of Microelectronics, Fudan University, Shanghai 201203, China

伴随集成电路工艺尺寸的缩小和系统供电电压的降低,工艺、电压和温度(process voltage and temperature, PVT)偏差导致电路延时波动明显[1-2],从而使关键路径出现大量时序违例的情形. 为了保证电路稳定、可靠地工作,传统设计方法需要引入充足的设计余量,导致电路性能、面积和功耗的巨大损失. 因此,研究人员提出了基于在线时序错误检测和纠正(error detection and correction,EDAC)的电路容错技术,通过在关键路径末端插入时序检测和纠错单元实时监测电路PVT偏差,动态调整系统的供电电压或者工作频率,确保系统正常工作[3-5].

当前EDAC技术主要集中在检错寄存器的成本优化与纠错电路的性能提升上. Chae等[6]采用新增从锁存器,通过双采样的方式来进行寄存器采样错误检测,而Zhang等[7]仅通过新增3个晶体管来感应寄存器内部电流变化,从而探测时序错误. 对于纠错电路而言,Kwon等[1]实现的传统指令重走机制需要对处理器原有架构进行修改,并存在长达11个时钟周期的性能损失. 因此Choudhury等[8-11]提出基于时序借用的现场纠错技术,仅产生单时钟周期的性能损失,并可通过商用工具自动集成到系统中,无需修改系统架构.

对于容错系统而言,如果其时钟树网络采用时钟门控单元来降低动态功耗,那么该时钟网络将同样面临时序错误的风险. 时钟网络通常占据系统总体动态功耗的50%[12],而时钟门控技术被用于在不需要提供时钟信号时关闭部分时钟网络. 同时,时钟门控单元采用锁存器电路避免输出时钟信号出现毛刺. 因此,该单元必须满足器件的时序约束要求,比如建立时间. 当PVT波动导致器件发生时序错误时,挂载在对应时钟树网络的寄存器簇将会保存错误的数据.

容错系统一旦引入时钟门控技术,需要为时钟门控单元增加EDAC机制. 尽管可以通过消除所有位于关键路径的时钟门控单元来避免该类单元的时序错误,但这会极大地削减时钟门控技术带来的能效收益. 因为综合工具倾向于将门控单元放置在靠近时钟树根节点以控制更多的器件,这导致时钟门控单元在关键路径的占比很高. 此外,门控单元的输入使能信号取自寄存器的输入端,而研究表明即使对于不同的处理器架构,55%的寄存器均位于关键路径上[1, 13].

本文提出一种适用于时序容错系统的时钟门控单元. 该单元利用内部节点完成错误的指示与当前周期自主现场纠错,并针对宽电压应用增强在近阈值电压下实现EDAC机制的稳定性. 结合现有的多种时钟门控技术,探究所提出的容错时钟门控单元的适用性和与之对应的纠错方案选择策略. 本文基于SMIC 40 nm LL工艺库,在传统时钟门控单元基础上仅新增12个额外的晶体管实现该单元. 通过将该单元应用于商用处理器中,研究其对容错系统能效和时钟树功耗带来的影响.

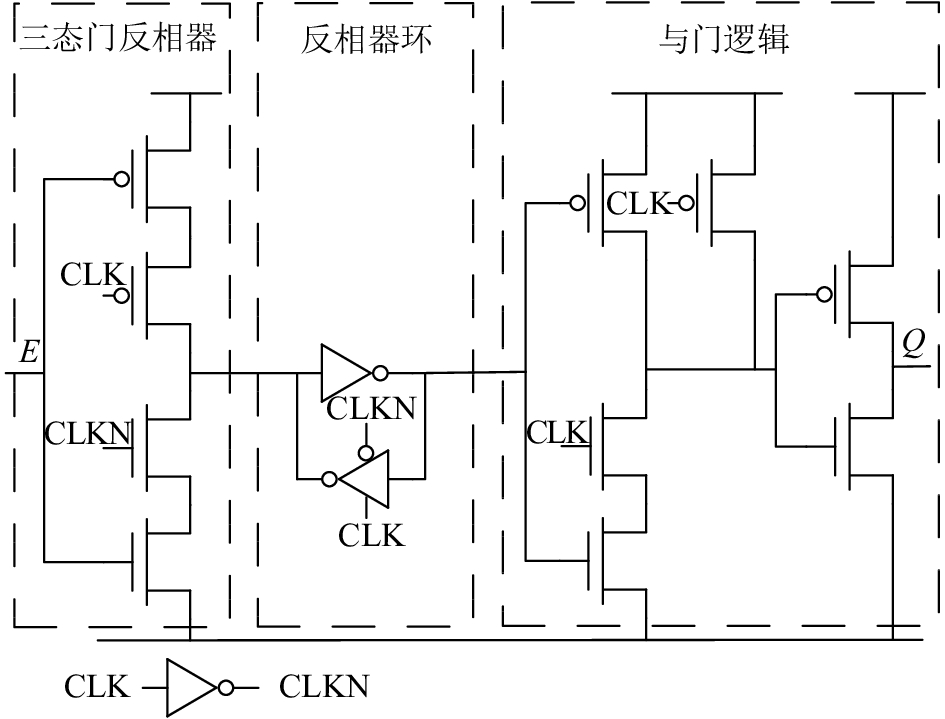

1 容错时钟门控单元 1.1 传统集成式时钟门控单元传统的时钟门控单元如图1所示. 该单元主要由三部分组成:三态门反相器、反相器环以及与门逻辑. 三态门反相器和反相器环共同组成负锁存器结构,在时钟高电平到来时,将输入的时钟使能信号E锁存. 与门逻辑负责将该锁存结果和时钟信号相与,从而得到最终通给各个特定寄存器的时钟信号. 由于时钟高电平期间,输入信号E端翻转不会传播到后级的时钟树网络,可以避免时钟毛刺出现.

|

图 1 传统集成式时钟门控单元 Fig. 1 Traditional integrated clock gate |

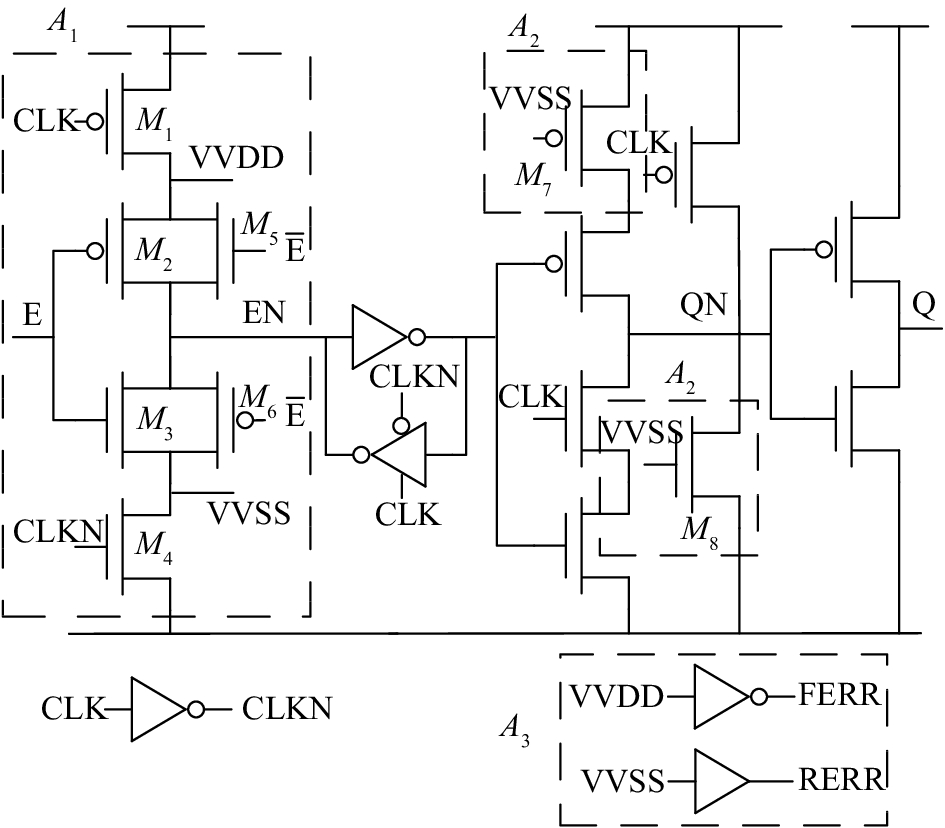

容错时钟门控单元在传统的时钟门控单元基础上,新增了在检错窗口内时序错误的检测与时钟信号的恢复逻辑,具体电路结构修改如图2虚线框所示. 首先在区域A1调整第一个三态门反相器的晶体管顺序,从而引出VVDD和VVSS两个内部虚拟节点[1]. 当输入E端数据在时钟高电平期间发生变化时,两节点将各自针对“0→1”和“1→0”这2种翻转情形出现电平的变化. 由于NMOS晶体管传输高电平和PMOS晶体管传输低电平时均会发生阈值损失,新增晶体管M5和M6用于提高上述两节点在近阈值电压下电压监测能力的稳定性. 其次,区域A2新增由VVSS驱动的晶体管M7和M8,用于错误的自修正过程. 当输入E端在检错窗口内发生“0→1”翻转时,VVSS节点将充电到高电平,并驱动M7和M8对QN点进行放电操作,从而对点Q重新输出正确的高电平时钟信号. 最后,新增区域A3负责监测VVDD和VVSS的电压变化,从而相应的生成两种不同翻转情形下的错误信号.

|

图 2 容错时钟门控单元的原理图 Fig. 2 Schematic of timing error resilient clock gate |

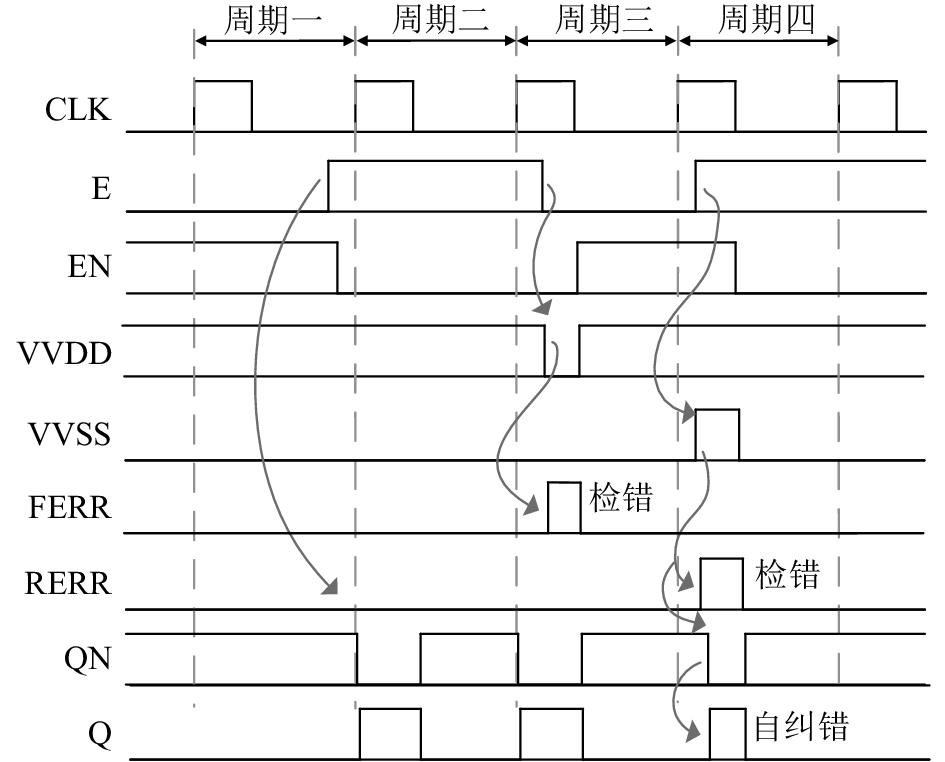

容错时钟门控单元的工作时序特征如图3所示. 在时钟信号CLK周期一和周期二,该单元正常实现普通门控时钟功能. 当输入信号E为低电平时关断输出时钟信号Q,而高电平时输出一个完整周期的时钟信号. 在时钟周期三,E端信号晚到且为“1→0”翻转情形. 节点EN是第一个三态门反相器的输出节点,当时钟信号为低电平时,该反相器导通,EN为输入信号E的取反值. 而在时钟高电平期间晶体管M1和M4关断,EN将保持原值. 在当前输入信号翻转情形下,EN此时为低电平. 晶体管M2、M5开始导通,M3、M6则关断. 节点VVDD在时钟上升沿到来前已预充电至高电平,此时将被逐渐放电到零. 该节点的电平变化将通给A3区域的反相器,从而输出错误信号FERR变为高电平. 同时该单元仍旧输出完整的时钟信号,不会被关断. 在时钟周期四,E端信号晚到且为“0→1”翻转情形. 此时节点EN保持为之前的高电平. 晶体管M2、M5开始关断,而M3、M6导通. 节点VVSS在时钟上升沿到来前已放电到低电平,此时将逐步被充电到完整的高电平. 该节点的电平变化将通给A3区域的缓冲器,输出错误信号RERR变为高电平. 由VVSS驱动的晶体管M8将导通,从而对节点QN进行放电操作. 同时M7将会被关断,加速该放电过程. 最终容错时钟门控单元将原先错误关断的时钟网络当前周期重新使能,完成时序错误的自修正过程.

|

图 3 容错时钟门控单元的工作时序特征 Fig. 3 Conceptual timing diagram of error resilient clock gate |

不同于现有的容错寄存器设计[3-13],容错时钟门控单元需要提供2种不同的错误指示信号FERR和RERR. 考虑时钟门控单元的基本功能,其不仅需要向对应的寄存器组提供有效的时钟信号,还必须在系统要求关断时钟网络时,不能错误使能;否则对于部分时钟门控技术而言,将会导致寄存器采样错误数据,从而破坏原先保存的正确值. 因此如果时钟门控单元需要加入检错纠错机制,需要和当前设计实现的时钟门控技术种类共同考虑. 基本时钟门控、多级时钟门控和层次化时钟门控技术[14]消除了原先位于寄存器输入端的多路选择器,当由于时钟门控单元时序错误导致其时钟信号未被关断时,寄存器原先保存值将很可能被更改. 因此对于上述时钟门控技术,容错时钟门控单元将根据2种不同的晚到情形,通过2种不同的错误信号指示,相应完成对应的纠错行为. 当E端发生时序错误且为“0→1”翻转情形时,通过现场纠错重新提供有效时钟信号;当“1→0”翻转情形时,系统依赖指令重走机制恢复正确指令流.对于增强型时钟门控和数据驱动型时钟门控技术[15-16]而言,即使时钟错误打开,数据仍旧不会被破坏掉. 因此当E端发生时序错误,2种翻转情形均可以仅采用现场纠错技术来恢复正确指令流.

|

图 4 容错时钟门控单元的版图设计 Fig. 4 Layout of timing error resilient clock gate |

图4为容错时钟门控单元的版图设计,该设计基于SMIC 40 nm工艺库中的传统时钟门控单元,通过在区域A1、A2和A3进行修改得到. 考虑到加快错误信号产生与输出时钟自修正过程,晶体管M8和A3区域错误产生逻辑的器件宽长比进行偏置性逻辑调整. 如对于M8而言,VVSS只存在将QN点单向放电的需求,因此可以加大该NMOS管宽长比.

通过抽取版图的物理参数,容错时钟门控单元与改动前的传统单元通过SPICE仿真进行电路特性对比. 仿真在1.1 V、25 ℃工作环境下进行,得到的数据如表1所示. 标准的时钟门控单元由22个晶体管构成,在此基础上增加12个管子用于提供容错能力,面积因而增加87%. 这导致器件静态功耗提高95%,而动态功耗仅增加16%. 考虑到器件在E端发生“0→1”时序错误时仍旧可以提供自修正能力,对于建立时间对比而言,数据将会相差较大. 因此建立时间和保持时间对比选择“1→0”翻转情形. 建立时间减小为改动前的0.31,而保持时间为改动前的0.37. 这是由于新增的晶体管M5与M6加快了EN节点的充放电速度,且VVDD和VVSS节点提供额外的电容,从而提高第一个三态门反相器的驱动能力.

| 表 1 容错时钟门控单元的电路特性变动 Table 1 Circuit characteristic change of timing error resilient clock gate |

应用时钟门控技术的设计需要对时钟门控和寄存器2种时序器件均进行时序约束分析.

|

图 5 容错时钟门控设计的时序路径分析 Fig. 5 Timing path analysis of error resilient cock gate design |

如图5所示为容错时钟门控设计的时序路径分析. 容错系统具备检错与纠错能力,因此采样器件进行建立时间分析时增加一段检错窗口大小的时序余量. 对于容错时钟门控而言,其检错窗口大小与寄存器存在一定差异. 这是由于该单元进行错误自修正时重新提供给后级寄存器簇的时钟信号,需要满足寄存器正常采样操作所需的最小时钟宽度要求. 因此对于容错时钟门控而言,其建立时间需要满足下列时序约束:

| ${t_{{\rm{arrive}}}} = {t_{{\rm{ctd1}}}} + {t_{{\rm{FFCKQ}}}} + {t_{{\rm{comb}}}}\text{,}$ | (1) |

| ${t_{{\rm{arrive}}}} + {t_{{\rm{setup}}}} < {T_{{\rm{CK}}}} + {T_{{\rm{CGDW}}}} + {t_{{\rm{ctd}}}}\text{,}$ | (2) |

| ${T_{{\rm{CGDW}}}} = {T_{{\rm{FFDW}}}} - {t_{{\rm{EQ}}}} + {t_{{\rm{CGCKQf}}}} - {T_{{\rm{FFckmin}}}}\text{.}$ | (3) |

式中:tctd1为第一级寄存器时钟树延迟,tFFCKQ为寄存器CK端到Q端延迟,tcomb为当前流水线组合路径延迟,tsetup为时钟门控单元等效建立时间,TCK为系统时钟周期,TCGDW为时钟门控单元的检错窗口,tctd为到达时钟门控单元的时钟树延迟,TFFDW为寄存器的检错窗口,tEQ为时钟门控单元的E端到Q端延迟,tCGCKQf为时钟门控单元从时钟下降沿时从CK端到Q端延迟,TFFckmin为寄存器时钟信号最小宽度.

容错时钟门控单元的保持时间检查需要考虑最小路径的问题. 这要求所有到达容错时序单元的路径延时必须大于该单元的检错窗口大小[17-18],避免误检发生. 因此该单元的保持时间检查如下:

| ${t_{{\rm{ctd1}}}} + {t_{{\rm{comb}}}} + {t_{{\rm{FFCKQ}}}} > {T_{{\rm{CGDW}}}} + {t_{{\rm{ctd}}}}.$ | (4) |

容错寄存器的时序分析与其他EDAC技术相同[1],由于具备时序借用的能力,它的建立时间分析也具有额外的时序余量TFFDW.

1.5 宽电压操作可容错设计通过动态调频调压模块调节系统工作电压和频率,从而达到所需的性能与功耗权衡. 由于器件功耗与供电电压之间呈平方关系,近阈值计算可以极大的提高系统能效[19]. 因此容错时钟门控单元要求能够稳定工作在宽电压(0.6~1.1 V)环境下. 这需要通过SPICE工具对其时钟门控功能和检错纠错能力进行仿真,得到宽电压尤其是近阈值电压下的工作数据.

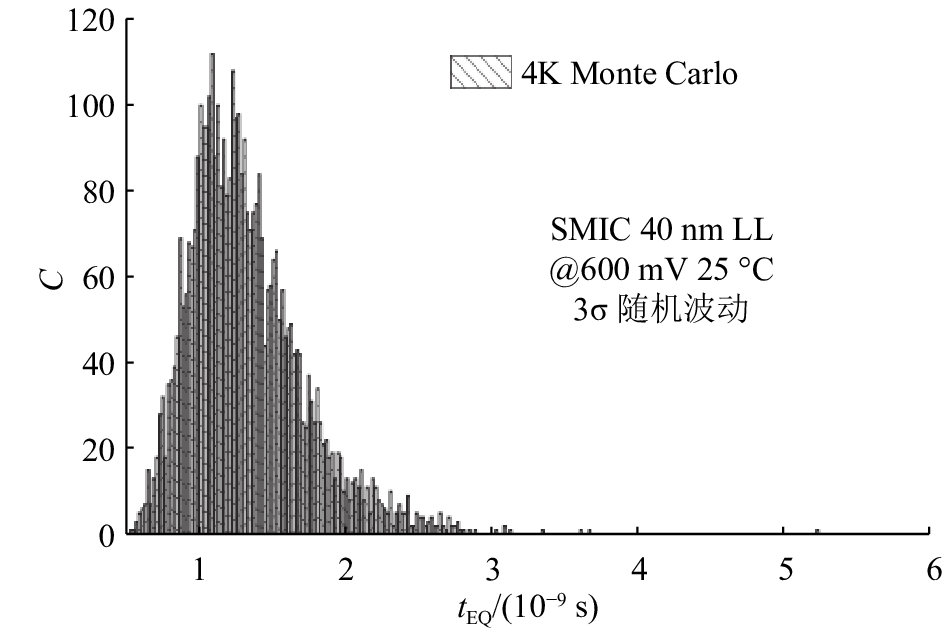

评估该单元的检错纠错能力采用发生时序错误时输入E端到输出错误端FERR/RERR错误指示信号产生时间和到输出时钟Q端时钟重新有效的恢复时间进行评判. 为了得到PVT对于电路工作特性影响,引入基于SPICE工具的4K Monte Carlo仿真. 如图6所示为容错时钟门控单元在0.6 V电压下发生“0→1”时序错误时E端到Q端输出自修正时间tEQ. 该延时最大值为5.4 ns左右,平均值为1.3 ns. 同时对错误信号产生时间进行相同仿真实验,得到RERR端错误产生最大延时为5.1 ns.

依据仿真得到的错误产生与恢复时延,结合式(3)给出的门控单元检错窗口大小TCGDW计算方法,得到器件在指定检错窗口大小下的最高工作频率. 现有容错系统设计的检错窗口大小为5%~30%[7-11],本文指定该窗口大小为系统周期的25%. 因此当工作电压为0.6 V时,计算得到容错单元的最高可工作频率为23 MHz. 采用同样方法,可以得到容错单元在1.1 V下的最高工作频率是6.1 GHz.

|

图 6 基于4 000次蒙特卡洛仿真的器件自修正延时 Fig. 6 Self-correction delay of timing error resilient clock gate by 4K-point Monte Carlo simulation |

容错时钟门控单元技术被集成到一款C-SKY CK802商用处理器中. C-SKY CK802是杭州中天采用国产自主16/32位混合指令集,研发的面向物联网应用的嵌入式处理器[20],可以提供一定的性能(1 DMIPS/MHz),同时只需占用很小的面积和功耗成本. 处理器实现了三级流水线,包括取指级、译码执行级和回写级.

该容错系统设计包含2个方面. 一是将关键路径上的寄存器和门控单元替换为相对应的容错时序器件. 其中容错寄存器同样具备错误检测与消除能力[21]. 而系统错误的修正仅采用现场纠错策略,并选择与之对应的时钟门控技术,无需对架构进行修改. 另一方面系统需要利用错误收集电路来将各个错误信号相或从而得到最终的错误指示信号. 为了加速该过程,采用iRazor[7]中实现的动态或门锁存器. 同时该错误信号将会被用于关闭整体系统时钟一个周期,这样可以给予流水线更多的时间用于计算,避免时序借用对流水线下一级的影响.

容错时钟门控技术可以被自动化工具集成到商用设计流程中. 应用该技术的设计物理实现包含如下步骤:1)在RTL或者综合步骤插入选定的时钟门控技术;2)经过完整后端流程得到关键路径信息,包含寄存器和时钟门控单元,并加以替换;3)分析所有路径是否时序收敛,并进行相应的修正操作;4)在不同的电压下遍历时序收敛检查.

3 实验评估 3.1 容错系统实现与对照组设计首先基准参考设计采用传统的物理设计流程,通过增加系统设计余量来保护电路. 并且该设计引入时钟门控技术,从而得到传统流程下能达到的最低功耗. 其次,为了验证容错时钟门控单元对于EDAC系统的时钟树功耗控制效果,提出EDAC对照设计. 该设计仍旧在非关键路径插入传统的时钟门控单元,仅取消关键路径的门控单元. 最后,本文实现容错时钟门控设计,具体实现细节如表2所示. 相对于基准设计,新增面积成本为10.03%,这主要来自替换的容错单元面积增加和最短路径的修正代价. 而对比EDAC对照设计,由于本文在关键路径新增容错时钟门控设计,因此这部分组合逻辑以及相应的检错纠错电路带来3.43%的额外面积.

| 表 2 基于容错时钟门控技术的处理器实现细节 Table 2 Proposed processor implementation details |

相对于传统基准设计,容错系统可以保护处理器工作在更低的电压或者更高的频率下,带来能效或者性能的提高. 为了考虑PVT波动对于电路的影响,研究人员对于基准设计增加如电压降和温度效应等的波动因素[7, 22-23]. 本文采用和Razor II[22]相同的策略,对于基准设计加入30%的设计余量.

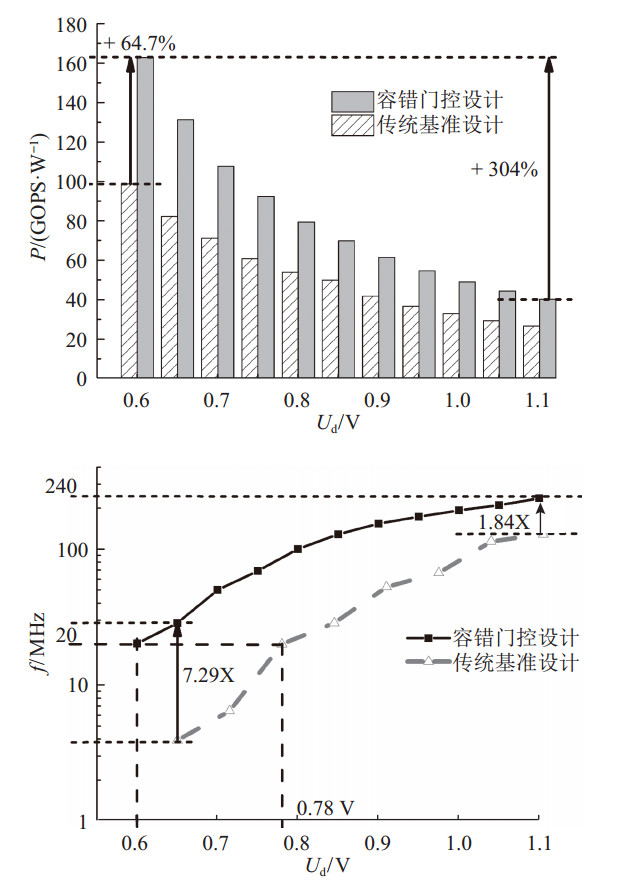

本文选择Drystone基准程序为测试程序,该程序可以覆盖C-SKY CK802后端设计中所有的时序关键路径. 如图7所示为容错时钟门控设计相对于传统基准设计的工作频率与能效数据对比,其中变量P表征系统工作能效. 容错设计由于具备检错和纠错能力,所以工作在第一个出错点(point of first failure, POFF)附近. 可以看到伴随着电压Ud的下降,容错系统在0.6 V下的能效相对于1.1 V提高304%,并且比基准设计在相同工作电压下提高64.7%. 同时容错设计在近阈值电压情形下的工作频率f是基准设计的7.29倍. 为了达到和容错设计在0.6 V电压下相同的工作频率,基准设计需要工作在0.78 V. 容错系统的能效和性能提升是因为该设计消除了系统过多的设计余量,并通过检错和纠错机制来保证器件能够在更严苛的工作环境下正常工作.

|

图 7 宽电压工作下容错时钟门控设计与基准设计在能效与频率方面对比 Fig. 7 energy efficiency and working frequency of error resilient clock gate design and baseline design during wide-voltage operation |

容错系统可以通过进一步降低电压或者超频的方式使电路工作在POFF点以下,从而获得更高收益. 以超频为例,图8给出容错系统工作在更高频率下的出错错误数与对应的能效. 伴随工作频率的提高,系统出错数增加,并且当工作周期T低于41 ns之后出错率提高速度加快. 容错系统的能效在出错率较低时,可以进一步的提高,并且在周期为43.5 ns时达到最大值. 之后开始下降,但是在最差情形的能效与最高值相比只降低0.53%. 这是由于本设计采用当前周期现场纠错技术,每次发生错误只需要1个周期的纠错成本. 数据表明,通过工作频率的提高,使每个任务所需的执行时间减少,最终可以降低每个计算任务所需的总能量消耗.

|

图 8 超频工作下容错时钟门控设计的错误数和能效 Fig. 8 error count and energy efficiency of timing error resilient clock gate design during overclocking |

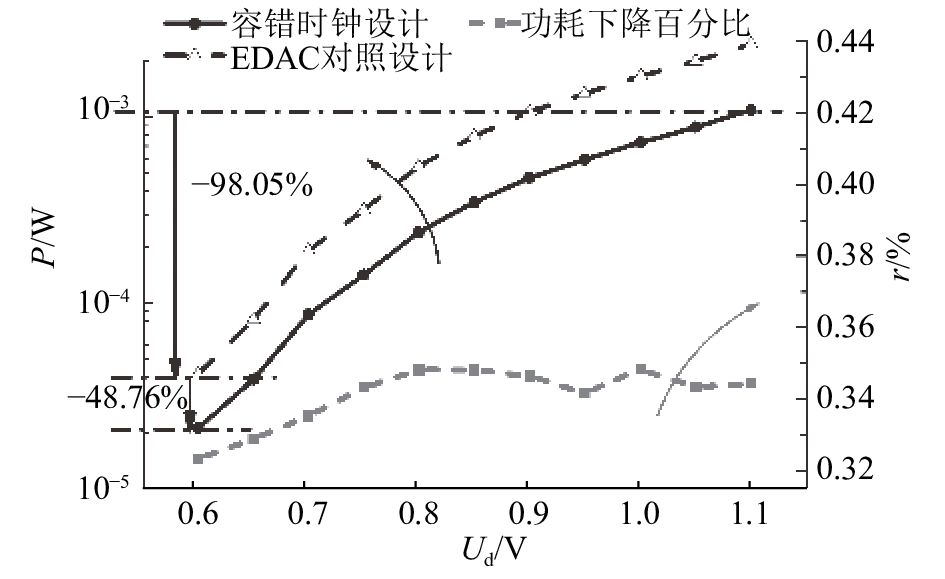

将时钟门控技术应用于时序容错系统中,观察其对于该系统时钟树功耗的影响. 如图9所示为容错时钟门控设计和EDAC对照设计在宽电压工作条件下的时钟树功耗对比和系统整体功耗下降百分比. P表征时钟树功耗,r表征功耗下降百分比. 伴随工作电压的下降,容错时钟门控设计的时钟树功耗总是低于EDAC设计,并且在0.6 V电压下降低了48.76%. 这带来系统整体功耗在近阈值计算时下降约32%. 可以看出,EDAC设计在关键路径加入了容错时钟门控单元之后,功耗下降明显.

|

图 9 宽电压工作下容错时钟门控设计与EDAC对照设计的时钟树功耗对比和系统整体功耗下降百分比 Fig. 9 Clock tree power and total system power of error resilient clock gate design and EDAC design in wide-voltage operation |

本文提出的容错时钟门控单元在发生时序错误时针对“0→1”和“1→0”这2种输入翻转情形均能有效覆盖,并适用于不同的时钟门控技术. 针对宽电压操作要求,器件增强了在近阈值电压下稳定提供错误检测和自修正的能力. 通过提取器件版图参数并引入PVT波动因素影响,仿真验证了容错门控时钟单元在最差工作环境下仍旧适用于EDAC系统.本文进一步给出了集成有容错时钟门控单元的系统设计所需的时序分析策略.

实验结果表明,集成有该单元的容错系统设计······比传统基准设计的能效有显著的提高,而时钟树功耗相对于现有的EDAC设计下降明显. 通过自动化的插入方法,该技术可以被应用于处理器的商用物理设计流程.

| [1] |

KWON I, KIM S, FICK D, et al. Razor-lite: a light-weight register for error detection by observing virtual supply rails[J]. IEEE Journal of Solid-State Circuits, 2014, 49(9): 2054-2066. DOI:10.1109/JSSC.2014.2328658 |

| [2] |

张苏敏, 陈黎明, 袁甲, 等. 面向亚阈值的脉冲生成电路设计[J]. 微电子学与计算机, 2014(9): 118-121. ZHANG Su-min, CHEN Li-ming, YUAN Jia, et al. Design of subthreshold pulse generator[J]. Microelectronics & Computer, 2014(9): 118-121. |

| [3] |

HUANG C M, LIU T T, CHIUEH T D. An energy-efficient resilient flip-flop circuit with built-in timing-error detection and correction [C] // 2015 International Symposium on VLSI Design, Automation and Test (VLSI-DAT). Hsinchu: IEEE, 2015: 1–4. https://www.researchgate.net/publication/282918002_An_energy-efficient_resilient_flip-flop_circuit_with_built-in_timing-error_detection_and_correction

|

| [4] |

SHIN I, KIM J J, LIN Y S, et al. One-cycle correction of timing errors in pipelines with standard clocked elements[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24(2): 600-612. DOI:10.1109/TVLSI.2015.2409118 |

| [5] |

VALADIMAS S, FLOROS A, TSIATOUHAS Y, et al. The time dilation technique for timing error tolerance[J]. IEEE Transactions on Computers, 2014, 63(5): 1277-1286. DOI:10.1109/TC.2012.289 |

| [6] |

CHAE K, MUKHOPADHYAY S. A dynamic timing error prevention technique in pipelines with time borrowing and clock stretching[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2014, 61(1): 74-83. DOI:10.1109/TCSI.2013.2268272 |

| [7] |

ZHANG Y, KHAYATZADEH M, YANG K, et al. 8.8 irazor: 3-transistor current-based error detection and correction in an arm cortex-r4 processor [C] // 2016 IEEE International Solid-State Circuits Conference (ISSCC). San Francisco: IEEE, 2016: 160–162. https://www.researchgate.net/publication/296706793_ISSCC_2016_SESSION_8_LOW-POWER_DIGITAL_CIRCUITS_88_88_iRazor_3-Transistor_Current-Based_Error_Detection_and_Correction_in_an_ARM_Cortex-R4_Processor

|

| [8] |

FUKETA H, HASHIMOTO M, MITSUYAMA Y, et al. Adaptive performance compensation with in-situ timing error predictive sensors for subthreshold circuits[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2012, 20(2): 333-343. DOI:10.1109/TVLSI.2010.2101089 |

| [9] |

CHOUDHURY M, CHANDRA V, MOHANRAM K, et al. TIMBER: Time borrowing and error relaying for online timing error resilience [C] // Design, Automation & Test in Europe Conference & Exhibition (DATE), . Dresden: IEEE, 2010: 1554–1559. https://www.researchgate.net/publication/221341182_TIMBER_Time_borrowing_and_error_relaying_for_online_timing_error_resilience

|

| [10] |

SHIN I, KIM J J, LIN Y S, et al. A pipeline architecture with 1-cycle timing error correction for low voltage operations [C] //Proceedings of the 2013 International Symposium on Low Power Electronics and Design. Beijing: IEEE Press, 2013: 199–204. https://www.researchgate.net/publication/261299384_A_pipeline_architecture_with_1-cycle_timing_error_correction_for_low_voltage_operations?ev=auth_pub

|

| [11] |

ZHANG J, YUAN F, YE R, et al. Forter: A forward error correction scheme for timing error resilience [C] // 2013 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). San Jose: IEEE, 2013: 55–60. https://www.researchgate.net/publication/261076097_ForTER_A_forward_error_correction_scheme_for_timing_error_resilience

|

| [12] |

WIMER S, KOREN I. Design flow for flip-flop grouping in data-driven clock gating[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22(4): 771-778. DOI:10.1109/TVLSI.2013.2253338 |

| [13] |

CONSTANTIN J, WANG L, KARAKONSTANTIS G, et al. Exploiting dynamic timing margins in microprocessors for frequency-over-scaling with instruction-based clock adjustment [C] // Design, Automation & Test in Europe Conference & Exhibition (DATE), . Grenoble: IEEE, 2015: 381–386. https://www.researchgate.net/publication/300717721_Exploiting_Dynamic_Timing_Margins_in_Microprocessors_for_Frequency-Over-Scaling_with_Instruction-Based_Clock_Adjustment

|

| [14] |

BHUTADA R, MANOLI Y. Complex clock gating with integrated clock gating logic cell [C] // International Conference on Design & Technology of Integrated Systems in Nanoscale Era. DTIS. Rabat: IEEE, 2007: 164–169. https://www.researchgate.net/publication/4318702_Complex_clock_gating_with_integrated_clock_gating_logic_cell

|

| [15] |

ZHANG Y, TONG Q, LI L, et al. Automatic register transfer level CAD tool design for advanced clock gating and low power schemes [C] // 2012 International SOC Design Conference (ISOCC). Jeju: IEEE, 2012: 21–24. https://www.researchgate.net/publication/261312297_Automatic_Register_Transfer_level_CAD_tool_design_for_advanced_clock_gating_and_low_power_schemes

|

| [16] |

阳玉才. DisplayPort 数字视频设计与研究[D]. 合肥: 合肥工业大学, 2012. YANG Yu-cai. Design and research on displayport digital video interface [D]. Hefei: HeFei University of Technology, 2012. http://cdmd.cnki.com.cn/Article/CDMD-10359-1013023371.htm |

| [17] |

UPPU R K, UPPU R T, SINGH A D, et al. Better-than-Worst-Case Timing Design with Latch Buffers on Short Paths [C] // 2014 27th International Conference on VLSI Design and 2014 13th International Conference on Embedded Systems. Mumbai: IEEE, 2014: 133–138. http://www.researchgate.net/publication/262236776_Better-than-Worst-Case_Timing_Design_with_Latch_Buffers_on_Short_Paths

|

| [18] |

YANG Y M, JIANG I H R, HO S T. PushPull: Short-path padding for timing error resilient circuits[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2014, 33(4): 558-570. DOI:10.1109/TCAD.2014.2304681 |

| [19] |

LAULAINEN E, TURNQUIST M J, MÄKIPÄÄ J, et subthreshold timing-error detection 8 bit microcontroller S [C] // 2012 IEEE International Symposium on Circ. Seoul: IEEE, 2012: 2953̵2956.

|

| [20] |

C-SKY Microsystems. CK802 of C-SKY embedded CPU: 8-Bit CPU cost, 32-Bit CPU efficiency [EB/OL]. [2017-02-14]. http://en.c-sky.com/solution/13411.htm.

|

| [21] |

BOWMAN K A, TSCHANZ J W, KIM N S, et al. Energy-efficient and metastability-immune timing-error detection and instruction-replay-based recovery circuits for dynamic-variation tolerance [C] // Solid-State Circuits Conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International. San Francisco: IEEE, 2008: 402–623. http://www.mendeley.com/research/energy-efficient-metastability-immune-timing-error-detection-recovery-circuits-dynamic-variation-tol/

|

| [22] |

DAS S, TOKUNAGA C, PANT S, et al. RazorII: in situ error detection and correction for PVT and SER tolerance[J]. IEEE Journal of Solid-State Circuits, 2009, 44(1): 32-48. DOI:10.1109/JSSC.2008.2007145 |

| [23] |

KIM S, SEOK M. Variation-tolerant, ultra-low-voltage microprocessor with a low-overhead, within-a-cycle in-situ timing-error detection and correction technique[J]. IEEE Journal of Solid-State Circuits, 2015, 50(6): 1478-1490. DOI:10.1109/JSSC.2015.2418713 |