相变存储器(phase change memory, PCM)作为一种新型非易失存储器,由于其读写速度快、循环次数高、数据保持力长、存储密度大、读写功耗低以及非挥发等特性,被业界认为是最有发展潜力的下一代存储器[1-4].

相变存储器采用硫系化合物(Ge2Sb2Te5, GST)作为存储介质[5-6].该存储介质有2种相态:晶态(材料呈低阻状态)和非晶态(材料呈高阻状态).通过施加特定的写电流,可以实现存储介质在2种相态的转换,进而实现数据的存储.相变存储器的读操作是通过测量被选中的存储单元的电阻值来实现.一个预设的电压或电流被加于被选中的存储单元,同时读取单元流过的电流或两端电压;再将读取电流或电压与一个参考电流或电压相比较,即可确定存储单元的相态[7-10].

新型非易失存储器的读电路研究主要集中在读取速度[11-13]和读取可靠性[14-16].读取速度或随机读取时间往往受到寄生效应的限制.随着存储器规模的不断增大,阵列中寄生电容也在增多,这导致位线在达到满足要求的读出电压之前需要很长的充电时间,从而极大地制约了相变存储器的速度特性.Lei等[17-18]分析了非易失存储器中影响读取速度的几种寄生效应.Fan等[19-20]使用了一种全差分灵敏放大器,但其参考电流为恒定值,在与缓慢变化的读电流的比较中难以到达较快的读出速度.Chung等[21-22]采用了一种预充电方法,先选中一根位线,将位线充电至电源电压,再选中字线,使用一个高于电源电压的高电压进行读操作;因字线和位线都属地址信号,读出时间应从位线被选中时开始算起;该方法需要额外的升压电路,功耗较大且读出时间较长.Ko等[23]采用了一个温度跟踪参考电流源以补偿相变材料电阻变化导致的数据电流变化,但其自适应预充电方法的基本框架与文献[21-22]相同.本文提出一种相变存储器预充电读出方法,在解决上述问题的同时,以较小的读单元电流实现存储器的快速读取.

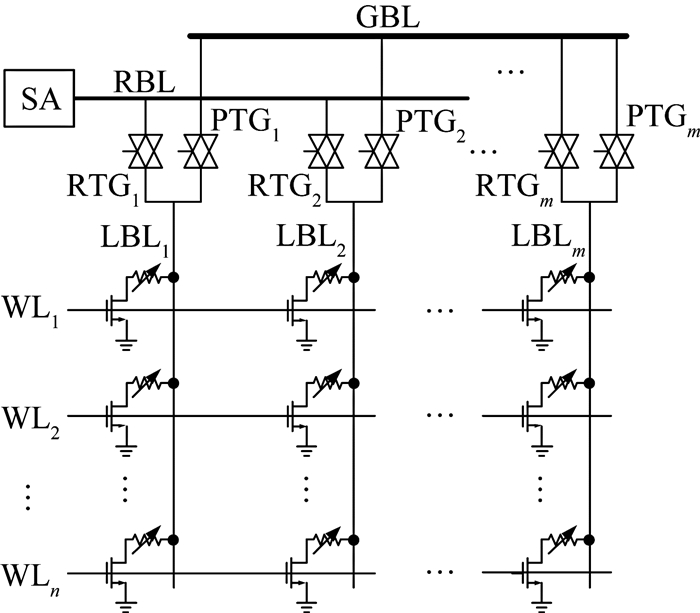

1 传统读出方法分析在如图 1所示的相变存储器阵列中,有多条字线(word line,WL)和位线(bit line,BL).字线连接选通器件的一端,用于控制选通器件的开关.位线连接于存储器件的一端,用于对相变存储单元进行读写操作.为实现对相变存储单元分别进行读写操作,有2种传输门:读传输门(read transmission gate,RTG)和写传输门(programming transmission gate,PTG).相应会出现3根位线:本地位线(local bit line,LBL),读位线(read bit line,RBL)和写位线(global bit line,GBL).其中本地位线连接于相变存储单元、读传输门和写传输门;读位线连接于读传输门和灵敏放大器(sense amplifier,SA).其中,m为降列中本地位线的个数.

|

图 1 相变存储器(PCM)阵列结构示意图 Fig. 1 Array architecture of phase change memory (PCM) |

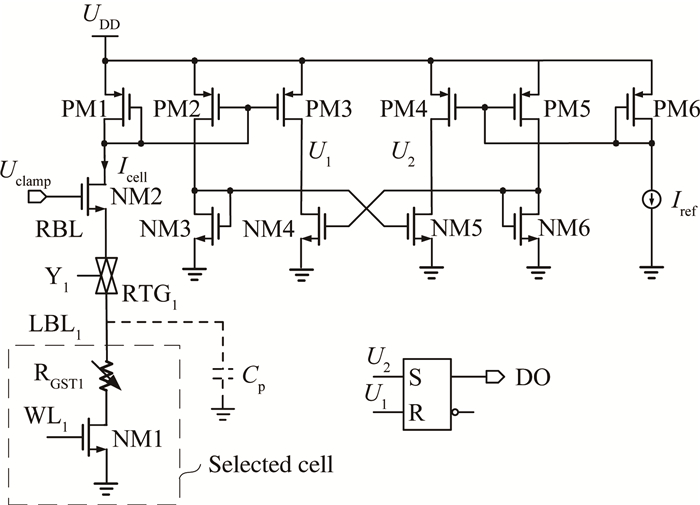

灵敏放大器电路示意图如图 2所示.虚线部分为被选中的相变存储单元,包括选通管NM1和相变电阻RGST1.位线信号Y控制传输门RTG的开启与关闭.Cp为相变存储器进行读操作时读路径上的寄生电容.NM2的栅端连接外部钳位电压Uclamp,产生被选中的相变存储单元中的读电流Icell.PM2,PM3将Icell复制到核心比较模块.Iref为参考电流,预设在晶态Icell和非晶态Icell之间.PM4、PM5将Iref复制到核心比较模块.当被选中的相变存储单元是一个晶态存储单元时,Icell > Iref.PM3试图镜像的电流大于NM4的电流,电压U1会上升到接近于电源电压VDD;PM4试图镜像的电流小于NM5的电流,电压U2会下降到0左右.SR锁存器将比较结果U1与U2锁存,其输出端DO此时输出高电平.非晶态存储单元的读取原理与晶态相似.

|

图 2 灵敏放大器(SA)电路示意图 Fig. 2 Schematic of sense amplifier (SA) |

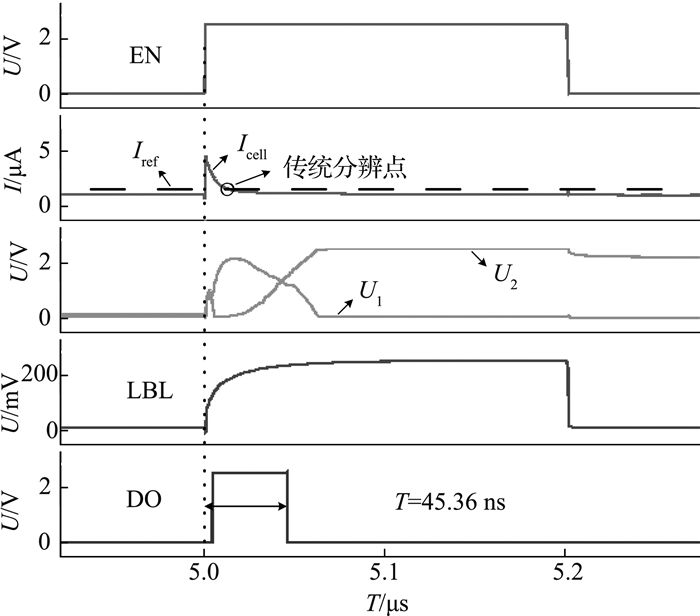

如图 3所示为采用传统读出方法的相变存储器的读出操作仿真结果,此时被选中的相变存储单元是一个非晶态相变存储单元.其中EN为读使能信号.该相变存储器中每个灵敏放大器对应128根字线和64根位线.基于SMIC 40 nm CMOS & PCM工艺设计,读出时间T=45.36 ns.读出操作之前,ULBL=0;读出操作阶段,稳定的ULBL在几十毫伏到几百毫伏.但因读出路径上寄生电容的存在,在读出操作的初始阶段,灵敏放大器需先给寄生电容充电,这时会产生一个较高的Icell,导致在读取非晶态单元时产生伪读取现象;当充电完成,ULBL稳定后,Icell也趋于稳定;在分辨点后,伪读取消失,灵敏放大器输出正确的读出结果(DO信号).

|

图 3 传统读出方法仿真结果 Fig. 3 Simulation results of conventional read scheme |

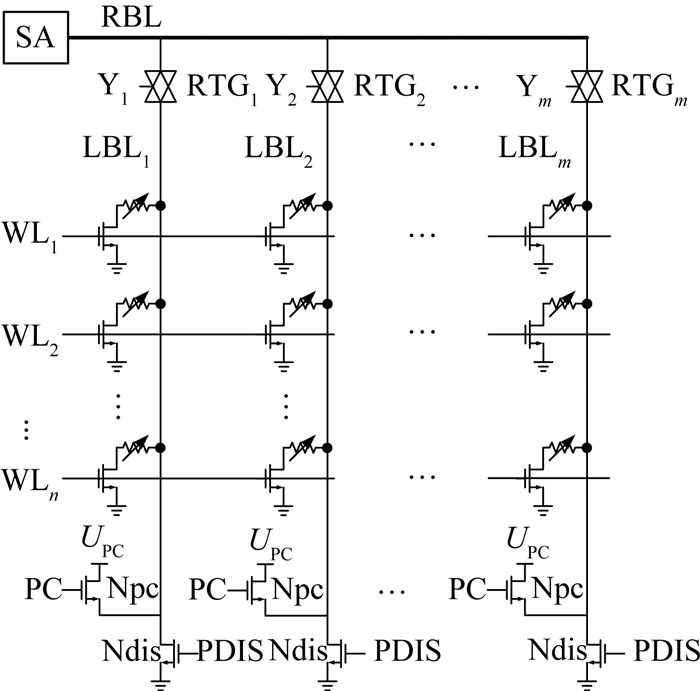

本文提出的相变存储器预充电读出电路如图 4所示.在与灵敏放大器相连的每条本地位线上,都有预充电NMOS管Npc连接.Npc由预充电信号PC控制,将本地位线充电至预充电电压UPC.每条本地位线还连接有放电模块Ndis,放电模块在读信号无效后泄放本地位线上的电荷.

|

图 4 相变存储器(PCM)预充电读出电路示意图 Fig. 4 Proposed pre-charge read circuit for PCM |

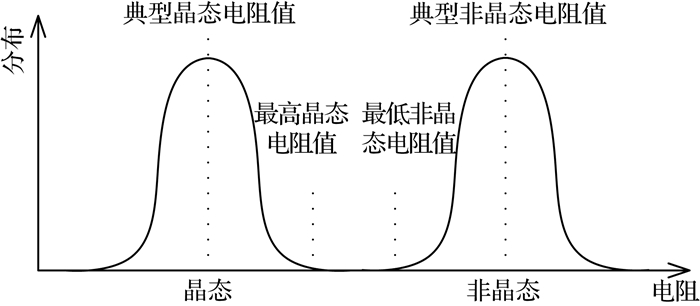

图 5为相变存储器芯片晶态电阻和非晶态电阻整体分布示意图.其中,典型晶态电阻值为分布最多的晶态电阻值,典型非晶态电阻值为分布最多的非晶态电阻值.读操作时的本地位线电压随着相变电阻阻值的增大而增大.本实验中,预充电电压设置在第一参考电压和第二参考电压的中间值.第一参考电压为读取最高晶态电阻值的存储器件时的本地位线电压,第二参考电压为读取最低非晶态电阻值的存储器件时的本地位线电压.此设计可以提高所有相变单元的读出速度.

|

图 5 相变存储器(PCM)晶态电阻和非晶态电阻整体分布示意图 Fig. 5 Distribution of set and reset resistance in PCM |

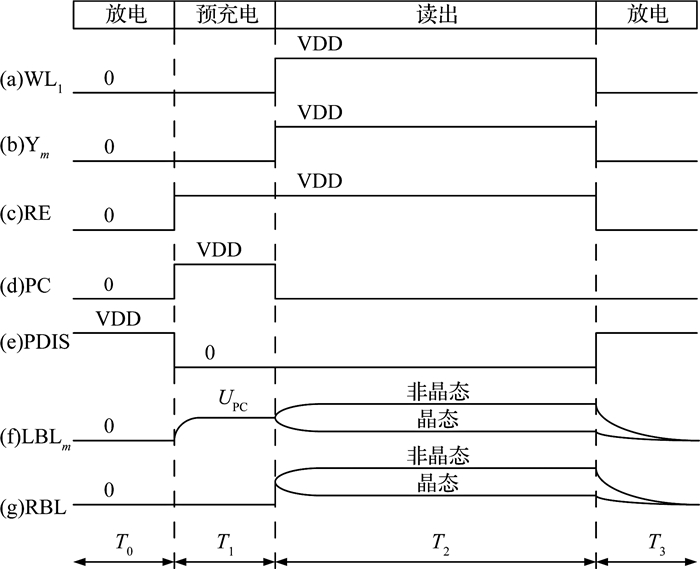

预充电读出方法的时序图如图 6所示.当外部读使能信号从0升至VDD后,芯片进入读模式.首先开始预充电阶段:预充电信号从0升至VDD,本地位线被Npc充电至UPC,预充电信号降至0,读出电路等待进入读出阶段.在读出阶段,一根字线和一根位线同时被选中,灵敏放大器开始读取.由于UPC被设置在读取最高晶态电阻值的存储器件时的本地位线电压和读取最低非晶态电阻值的存储器件时的本地位线电压的中间值,读取开始后,读出电路的电流和电压并不处于稳定状态;读取非晶态单元时,本地位线电压ULBL上升;读取晶态单元时,ULBL下降.当ULBL稳定后,Icell也趋于稳定,此时可得到正确的读出结果.当读模式结束后,Ndis泄放掉本地位线上的电荷.

|

图 6 预充电读出方法时序图 Fig. 6 Timing diagram of proposed pre-charge scheme |

本方法通过预充电将本地位线充电至预充电电压,预充电电压预设为2个参考电压的中间值,即使得读取非晶态电阻值的存储器件时的位线电压与预充电电压之差和读取晶态电阻值的存储器件时的位线电压与预充电电压之差相等,晶态单元的读出时间与非晶态单元的读出时间大致相等;且在接收到读取地址信号之前即将本地位线提前充电至预充电电压,从而使本地位线上的寄生电容储存了一定的电荷.在读取时,缩短了给寄生电容充电的时间,因此可以达到较快的读取速度,同时兼顾了读取的正确性和读裕度.另外,当相变存储器芯片调至读模式、即接收到读使能信号后,立刻开始对本地位线进行预充电,在达到预充电电压后,芯片即可随机读取,也就是说字线和位线并不因预充电而被提前选中,因此预充电的这段时间不被算进读取时间,从而大大减小了随机读取时间.

Fan等[19-20]在读取操作开始后,灵敏放大器开始给寄生电容充电,ULBL缓慢上升,升至一定电压后才能得出正确的比较结果;本方法中,ULBL提前充电至预充电电压,在读取时,缩短了给寄生电容充电的时间,因此可以达到较快的读取速度.Chung等[21-22, 25]的位线因预充电操作而提前选中,并需要额外的升压电路进行读取操作.本方法中,字线和位线并不因预充电而被提前选中,减小了随机读取时间;同时不需要额外的升压电路.

3 仿真结果分析基于SMIC 40 nm CMOS&PCM工艺,本方法应用于一款1-Mb相变存储器芯片.该芯片8位同时读写,每个灵敏放大器对应128根字线和64根位线.本文中,根据之前流片的40 nm PCM芯片测试结果,对GST器件进行了建模[20].表 1列出了相变电阻电阻值RGST和相应的本地位线电压ULBL,预充电电压设置在156.3 mV.

| 表 1 1-Mb相变存储器芯片各电阻值和相应的读本地位线电压 Table 1 Resistance of 1-Mb phase change memory chips and corresponding local bit line voltages |

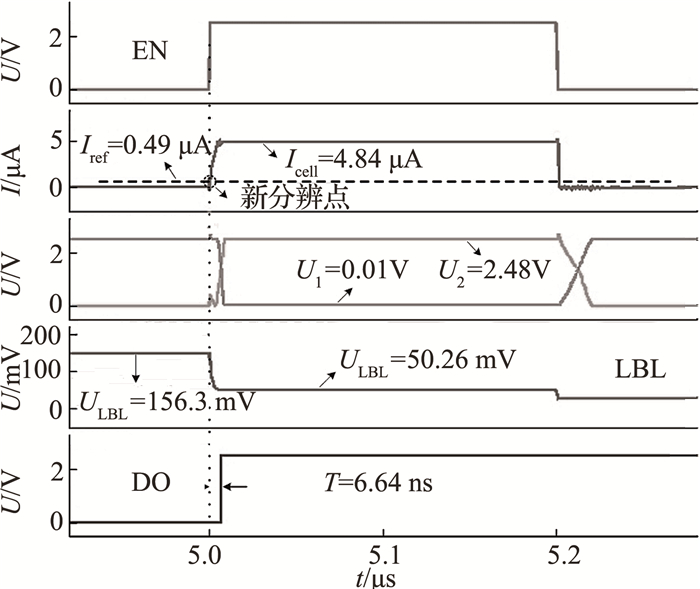

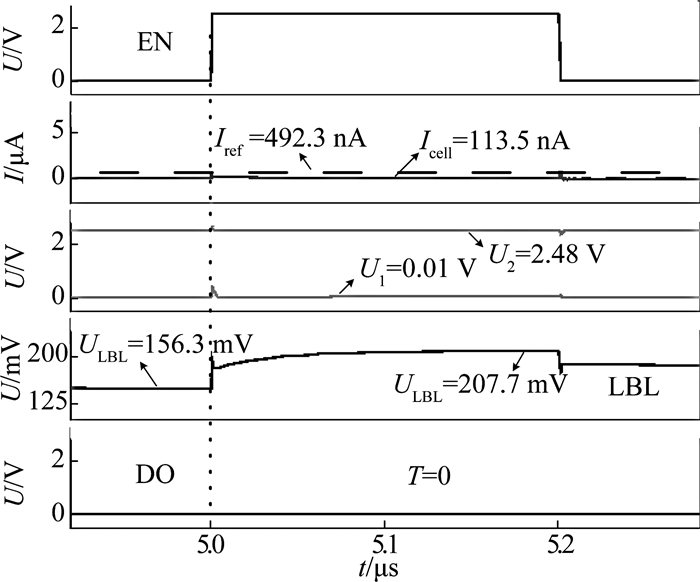

图 7和图 8为芯片的读取仿真结果,t为波形所处时刻.仿真环境为2.5 V电源电压,27 ℃和TT工艺角.对于非晶态单元和晶态单元,ULBL从UPC下降或上升到稳定值所需的时间大致相等;Icell更快的趋于稳定.本方法的分辨点大幅早于传统方法分辨点,相应的,芯片随机读取时间为6.64 ns.参考电流设置在492.3 nA,对应的参考电阻为300 KΩ.读晶态单元的Icell=4.84 μA.

|

图 7 读晶态单元仿真结果 Fig. 7 Simulation results of reading set cell |

|

图 8 读非晶态单元仿真结果 Fig. 8 Simulation results of reading reset cell |

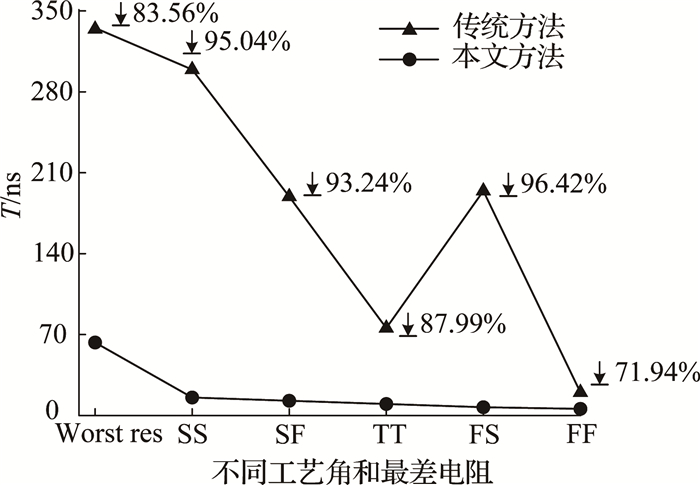

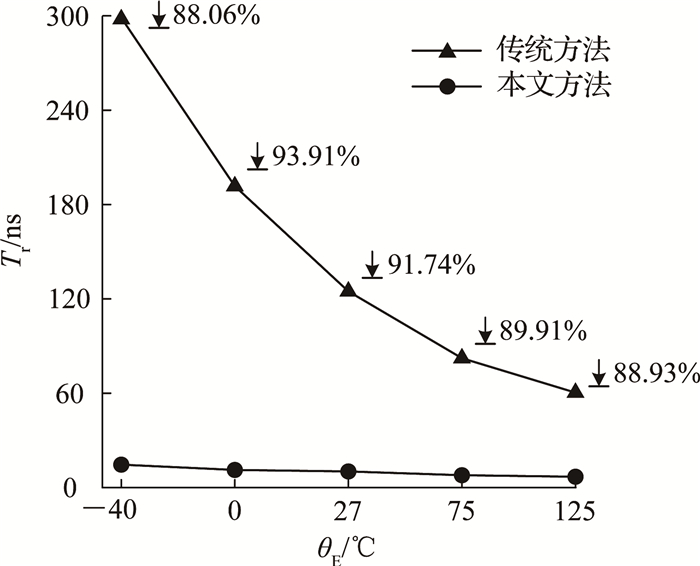

表 2、图 9和图 10分别是2种方法在不同工艺角,电源电压和温度(process, voltage and temperature, PVT)下的仿真结果.表 2的数据是在SS工艺角和-40 ℃下仿真得到的.Tr为随机读取时间,VDD为电源电压.图 9的数据是在2.5 V电源电压和-40 ℃下仿真得到的;对于最差电阻,指100 KΩ晶态电阻和1 MΩ非晶态电阻的仿真结果.图 10的数据是在2.5 V电源电压和SS工艺角下仿真得到的.在不同PVT参数下,本方法随机读取时间皆小于传统方法,且随机读取时间波动不大,说明本方法对于PVT波动有更好的抑制能力.

|

图 9 不同工艺角和最差电阻下随机读取时间对比 Fig. 9 Read access time comparisons under different process corners and worst resistances |

|

图 10 不同温度下随机读取时间对比 Fig. 10 Read access time comparisons under different temperatures |

| 表 2 不同电源电压下随机读取时间对比 Table 2 Read access time comparisons versus different VDDs |

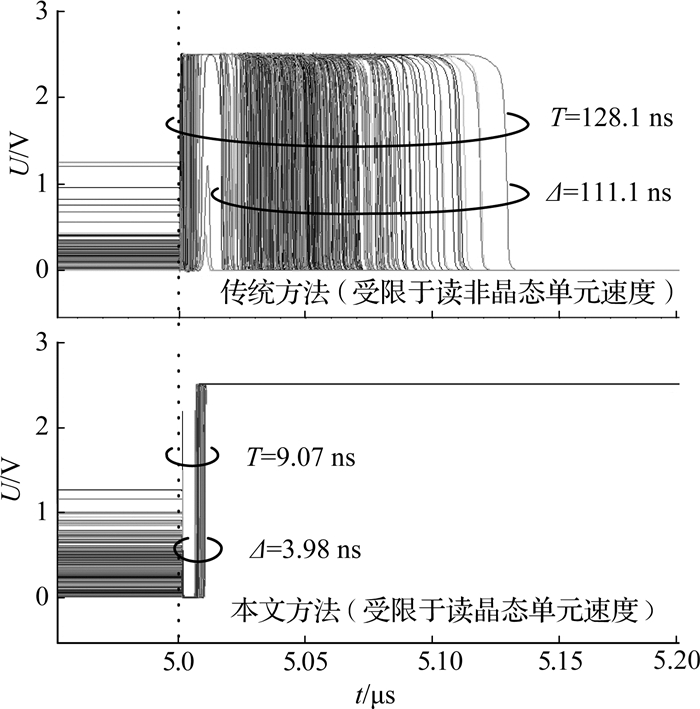

Monte Carlo仿真可以全面展示电路在面对工艺波动时的性能.图 11是2种方法的Monte Carlo仿真结果对比.仿真采用与工艺兼任的SMIC 40 nm Monte Carlo模型.仿真中,工艺和失调(mismatch)的变化同时被考虑入内,晶体管和电阻的参数和尺寸的变化量采用6倍的标准方差(6σ).每次仿真均运行4 000次(trials).传统方法的随机读取时间由读非晶态单元的时间决定,其最长随机读取时间为128.1 ns,最长随机读取时间与最短随机读取时间差值Δ=111.1 ns.本文所提出方法的随机读取时间由读晶态单元的时间决定,其最长随机读取时间为9.07 ns,Δ=3.98 ns.

|

图 11 本文方法与传统方法的Monte Carlo仿真结果对比 Fig. 11 Monte Carlo resultscomparison between our method and the conventional method |

表 3是本文所提出预充电读出方法和其他读出方法的性能对比.随机读取时间按照前仿,实测,最差Monte Carlo仿真结果进行了标注.对于相变存储器的读出电路,单元读电流Icell越大,随机读取时间Tr越小,但读的功耗也越大.本文提出的方法在单元读电流和读取速度都有着优秀的表现.

| 表 3 本文方法与重要文献性能比较 Table 3 Performance comparisons between our method and some important aricles |

本文提出了一种预充电读出方法.在地址信号来临之前,将本地位线充电到预充电电压;地址信号来临之后,开始读取操作.预充电电压设置在2个参考电压的中间值,可以提高所有相变单元的读出速度.该方法可以达到较小的随机读取时间,同时兼顾了读取的正确性和读裕度.采用SMIC 40 nm CMOS工艺进行设计和仿真,1-Mb相变存储器的随机读取时间为6.64 ns;Monte Carlo仿真表明,最长随机读取时间为9.07 ns.读晶态单元的电流为4.84 μA.仿真结果表明,本文提出的方法比传统方法对PVT波动有更好的抑制作用.

| [1] |

RAO F, DING K, ZHOU Y, et al. Reducing the stochasticity of crystal nucleation to enable subnanosecond memory writing[J]. Science, 2017, eaao3212: 1-10. |

| [2] |

雷宇, 陈后鹏, 金荣, 等. 用于相变存储器的高效开关电容电荷泵[J]. 微电子学, 2015, 45(3): 335-339. LEI Y, CHEN H, JIN R, et al. An efficiency-enhanced SC charge pump for PCM[J]. Microelectronics, 2015, 45(3): 335-339. |

| [3] |

BURR G W, BRIGHTSKY M J, Sebastian A, et al. Recent progress in phase-change memory technology[J]. IEEE Journal on Emerging & Selected Topics in Circuits & Systems, 2016, 6(2): 1-17. |

| [4] |

LEI Y, CHEN H, LI X, et al. An efficiency-enhanced 2X/1.5X SC charge pump with auto-adjustable output regulation for PCM[C]//International Workshop on Information Data Storage and Tenth International Symposium on Optical Storage. Changzhou:SPIE, 2016, 981807:1-7. http://proceedings.spiedigitallibrary.org/proceeding.aspx?articleid=2569694

|

| [5] |

XU Z, LIU B, CHEN Y, et al. The Improvement of Nitrogen Doped Ge2Sb2Te5 on the Phase Change Memory Resistance distributions[J]. Solid State Electronics, 2016, 116: 119-123. DOI:10.1016/j.sse.2015.11.001 |

| [6] |

GAO D, LIU B, Xu Z, et al. Failure analysis of nitrogen-doped Ge2Sb2Te5 phase change memory[J]. IEEE Transactions on Device and Materials Reliability, 2016, 16(1): 74-79. DOI:10.1109/TDMR.2016.2520984 |

| [7] |

JIN D H, KWON J W, KIM H J, et al. A 15μm-pitch, 8.7-ENOB, 13-Mcells/sec logarithmic readout circuit for multi-level cell phase change memory[J]. IEEE Journal of Solid-State Circuits, 2015, 50(10): 2431-2440. DOI:10.1109/JSSC.2015.2453236 |

| [8] |

YU S, CHEN P Y. Emerging memory technologies:recent trends and prospects[J]. IEEE Solid-State Circuits Magazine, 2016, 8(2): 43-56. DOI:10.1109/MSSC.2016.2546199 |

| [9] |

LEI Y, CHEN H, WANG Q, et al. A single-reference parasitic-matching sensing circuit for 3D cross point PCM[J]. IEEE Transactions on Circuits and Systems Ⅱ:Express Briefs, 2017, PP(99): 1-5. |

| [10] |

LEE K J, CHO B H, CHO W Y, et al. A 90 nm 1.8 V 512 Mb diode-switch PRAM with 266 MB/s read throughput[J]. IEEE Journal of Solid-State Circuits, 2008, 43(1): 150-162. DOI:10.1109/JSSC.2007.908001 |

| [11] |

HANZAWA S, KITAI N, OSADA K, et al. A 512kB embedded phase change memory with 416kB/s write throughput at 100μA cell write current[C]//IEEE International Solid-state Circuits Conference. San Francisco:IEEE, 2007:474-616. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4242471

|

| [12] |

TSUCHIDA K, INABA T, FUJITAa K, et al. A 64Mb MRAM with clamped-reference and adequate-reference schemes[C]//IEEE International Solid-state Circuits Conference. San Francisco:IEEE, 2010:258-259. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5433948

|

| [13] |

CHANG M F, WU J J, CHIEN T F, et al. 19.4 embedded 1Mb ReRAM in 28nm CMOS with 0.27-to-1V read using swing-sample-and-couple sense amplifier and self-boost-write-termination scheme[C]//IEEE International Solid-state Circuits Conference. San Francisco:IEEE, 2014:332-333. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=6757457

|

| [14] |

NN T, KIM J, KIM J P, et al. A double-sensing-margin offset-canceling dual-stage sensing circuit for resistive nonvolatile memory[J]. IEEE Transactions on Circuits & Systems Ⅱ Express Briefs, 2015, 62(12): 1109-1113. |

| [15] |

KO J, YANG Y, KIM J, et al. Incremental bitline voltage sensing scheme with half-adaptive threshold reference scheme in MLC PRAM[J]. IEEE Transactions on Circuits & Systems Ⅰ Regular Papers, 2017, 64(6): 1444-1455. |

| [16] |

NA T, KIM J, SONG B, et al. An offset-tolerant dual-reference-voltage sensing scheme for deep submicrometer STT-RAM[J]. IEEE Transactions on Very Large Scale Integration Systems, 2016, 24(4): 1361-1370. DOI:10.1109/TVLSI.2015.2453192 |

| [17] |

LEI Y, CHEN H, LI X, et al. Enhanced read performance for phase change memory using a reference column[J]. IEICE Electronics Express, 2017, 14(5): 1-10. |

| [18] |

LEI Y, CHEN H, LI X, et al. Set/reset reference and parasitic matching scheme to speed up PCM read operation[J]. Electronics Letters, 2017, 53(3): 144-146. DOI:10.1049/el.2016.3132 |

| [19] |

FAN X, CHEN H, WANG Q, et al. Optimization of periphery circuits in a 1K-bit PCRAM chip for highly reliable write and read operations[J]. IEICE Electronics Express, 2014, 11(24): 20141071-20141071. DOI:10.1587/elex.11.20141071 |

| [20] |

WANG Q, LI X, CHEN H, et al. Methods to speed up read operation in a 64Mbit phase change memory chip[J]. IEICE Electronics Express, 2015, 12(20): 1-6. |

| [21] |

CHUNG H, JEONG B H, MIN B J, et al. A 58 nm 1.8V 1Gb PRAM with 6.4MB/s program BW[C]//IEEE International Solid-state Circuits Conference. San Francisco:IEEE, 2011:500-502. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5746415

|

| [22] |

CHOI Y, SONG I, PARK M H, et al. A 20nm 1.8V 8Gb PRAM with 40MB/s program bandwidth[C]//IEEE International Solid-state Circuits Conference. San Francisco:IEEE, 2012:46-48. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=6176872

|

| [23] |

KO J, KIM J, CHOI Y, et al. Temperature-tracking sensing scheme with adaptive precharge and noise compensation scheme in PRAM[J]. IEEE Transactions on Circuits & Systems Ⅰ Regular Papers, 2015, 62(8): 2091-2102. |

| [24] |

LUNG H L, MILLER C P, CHEN C J, et al. A double-data-rate-2(DDR2) interface phase-change memory with 533MB/s read -write data rate and 37.5ns access latency for memory-type storage class memory applications[C]//IEEE International Memory Workshop. Paris:IEEE, 2016:1-5.

|

| [25] |

DE S G, BETTINI L, PIROLA A, et al. A 4 Mb LV MOS-selected embedded phase change memory in 90 nm standard CMOS technology[J]. IEEE Journal of Solid-State Circuits, 2011, 46(1): 52-63. DOI:10.1109/JSSC.2010.2084491 |