2. 浙江科技学院 理学院, 浙江 杭州 310023

2. College of Science, Zhejiang University of Science and Technology, Hangzhou 310023, China

工业相机因强鲁棒性、高拍摄帧率等特点被广泛应用到导航、测量、立体重建、模式识别等各个领域[1-2].但是在一些需要更高分辨率并对成本敏感的离散采样应用场合,工业相机将不再适用.因此,人们将更多的目光投向具有更高分辨率且低成本的民用相机系统.然而,采集图像的传输效率与系统稳定性是应用民用相机的主要瓶颈.对此,目前已有一些相应的解决方案.在离散采样应用领域中的系统稳定性方面,可以通过数据校验及自动重采样的方式对偶尔发生的无效采样行为进行有效规避.然而在图像传输方面,通过目前普遍采用的USB2.0协议,传输一张1 500万像素无压缩图像(15兆)大概需要5 s的时间,这在很大程度上制约了USB2.0传输协议工业化应用.为了解决上述问题,可以从以下2方面进行考虑:提高传输速率和减少传输数据量.

在民用相机的工业化应用过程中,部分研究人员通过对USB2.0接口进行升级或者替换方式来实现数据的高速传输[3-4],但是这样的改造对专业性要求较高,且破坏相机原有结构的方案具有增加系统不稳定性的潜在风险.为此东芝集团设计了具有WIFI功能的SD卡(Secure Digital Memory Card),在不破坏结构的前提下实现相机与上位机之间的无线传输,不过该方法也同样存在传输速度不理想的问题.

本文尝试通过外挂监听的方式,在不破坏相机结构的前提下,实现数据的快速传输.假设在相机拍照后图像存储到机身SD卡的过程中,可通过附加处理器的IO口实时监听该数据流.若能获取到完整的数据流,那么后继快速处理与传输将变得切实可行.

结合图像预处理硬件化的需要,现场可编程门阵列(field-programmable gate array, FPGA)是理想的附加处理器选择.这是因为它支持静态重复编程和动态在系统重配置,大大提高了系统设计的灵活性和通用性[5-6];此外,在高速信号处理应用中,能够在设计上实现硬件并行和流水线技术,因此可以大幅度提高处理速度,甚至可以超过目前最快的数字信号处理[7](digital signal processing, DSP).同时FPGA在预处理中的应用也为提高图像处理速度提供了新的思路和解决方法[8].

在完成监听与预处理工作后,需要一种传输方式来实现数据的快速传输.目前,处于主流地位的USB2.0技术已渐渐不能满足高速率的传输需求.基于PC机的高速外设接口,其种类主要有:IEEE1394接口,eSATA接口,PCI Express接口和USB3.0接口[9-10].与USB2.0相比,USB3.0除了具有USB通常的特性,在传输速率、接口性能、端点数目、通信方式、电源管理等方面都有了很大的提高[11-12].另外,从经济性角度考虑,USB3.0接口也是最佳的选择.

鉴此,本文主要研究基于FPGA监听与USB3.0传输的电路与算法实现.在不破坏相机原有结构的前提下,通过外挂附加处理器的方式对监听到的图像数据进行实时预处理并快速传输至上位机.实验显示,该方案是高效且鲁棒的.

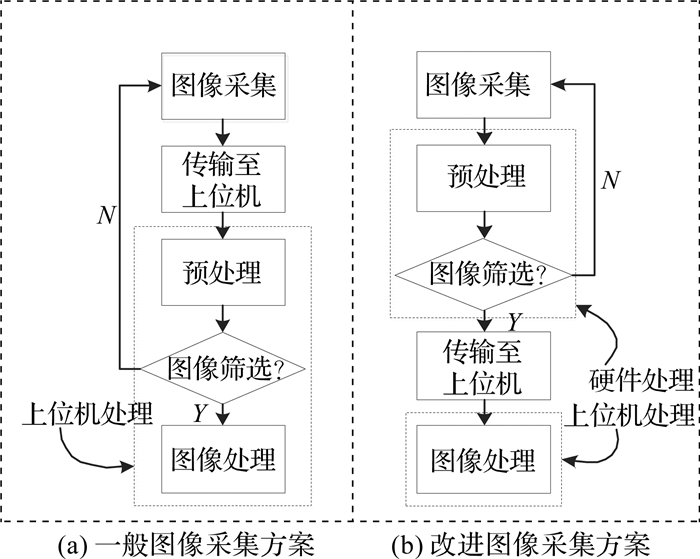

1 系统总体方案设计与实现对于民用相机的工业化应用方案,通常的实施步骤如图 1(a)所示:首先通过相机进行目标图像采集,然后将采集到的原始图像传输至上位机,由上位机对其进行必要的预处理和特征筛选工作,如果特征筛选成功,则进入下一步程序,否则需重新采样.通过研究可以发现,整个采样筛选过程中始终包含了极为耗时的图像传输步骤,对于特征筛选失败率较高的应用场景,这将导致整个系统的响应延时.为此,本文通过加入硬件芯片来实现传输之前的预处理与特征筛选工作,使得整个流程只包含一次图像传输步骤(如图 1(b)所示).为减轻上位机负担和提高整体系统效率,可选择硬件芯片FPGA应用在图像处理中.

|

图 1 图像预处理与筛选对比 Fig. 1 Comparison of image preprocessing and screening |

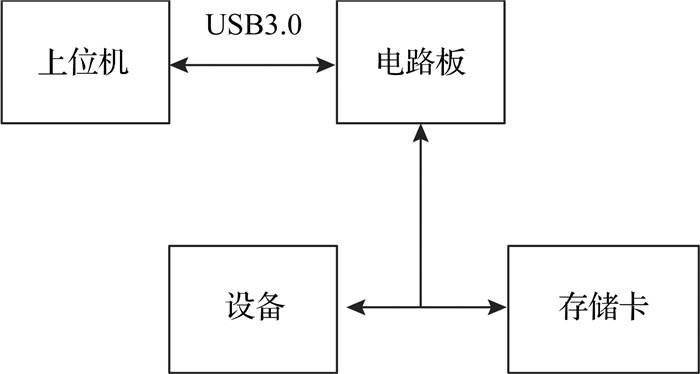

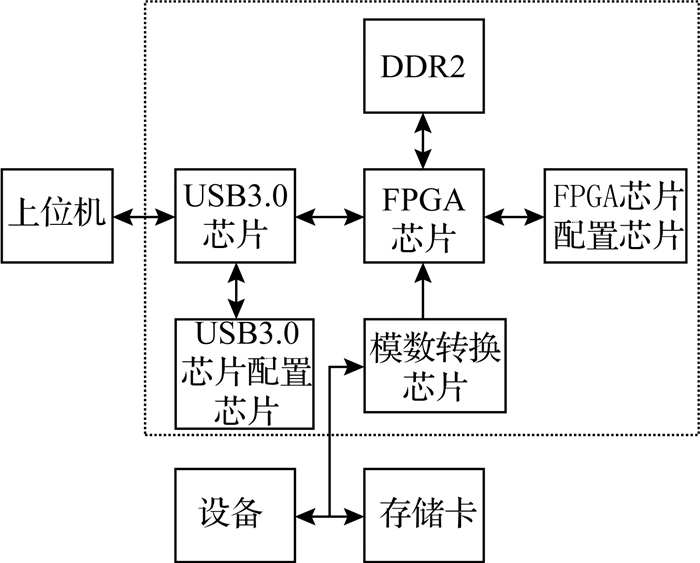

由于引入了FPGA, 则可通过其IO口对SD卡的数据传输进行实时化监听.如图 2所示,本文基于FPGA监听与USB3.0传输的图像预处理系统基本结构框图,包括电路板、上位机、民用相机、存储卡等.利用核心芯片FPGA强大的并行计算能力,对相机向SD卡写入图像数据的过程实行监听,将监听到的图像进行相应预处理并储存,最后上位机通过USB3.0与FPGA互相通讯,实现快速接收数据和还原图像文件等操作.在整体设计框架上,以下重点对核心模块进行深入分析,包括软件调试和实现、硬件设计、实验分析等.

|

图 2 图像预处理系统结构框图 Fig. 2 Image preprocessing system block diagram |

FPGA具有可设置分频数、占空比、移相等功能,可以提供片内和片外全面的系统始终管理,以便支持对其他设备的应用.FPGA模块设计框图如图 3所示,数据通过IO口进入后,首先进入乒乓控制模块,与外接RAM缓冲,然后通过先入先出模块(FIFO)进入图像预处理部分.FIFO、乘法器和加法器都可以直接调用FPGA中的IP模块.图像预处理的基本步骤:首先是图像的接收,进而是数据校验、浮点数定标、数据译码等步骤.这里根据实际需要可加入更多图像预处理技术,可将预处理后的数据存储在外接DDR2里面,进一步等待上位机的命令,而后通过接口上传.

|

图 3 FPGA模块设计框图 Fig. 3 FPGA module design block diagram |

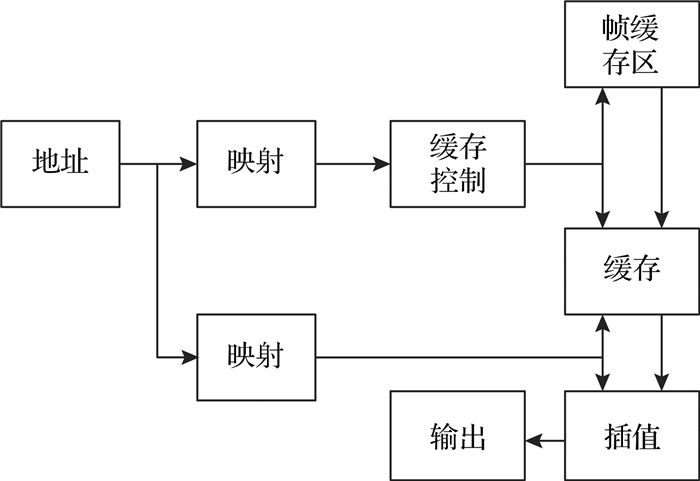

预载入缓存的方法如图 4所示.它需要提前计算哪些像素将要用到,这意味着需要计算2次,一次用于载入缓存,一次用于产生输出; 或者当所有像素都载入缓存后再将计算结果暂存下来供后面使用.

|

图 4 预载入缓存框图 Fig. 4 Preloaded cache block diagram |

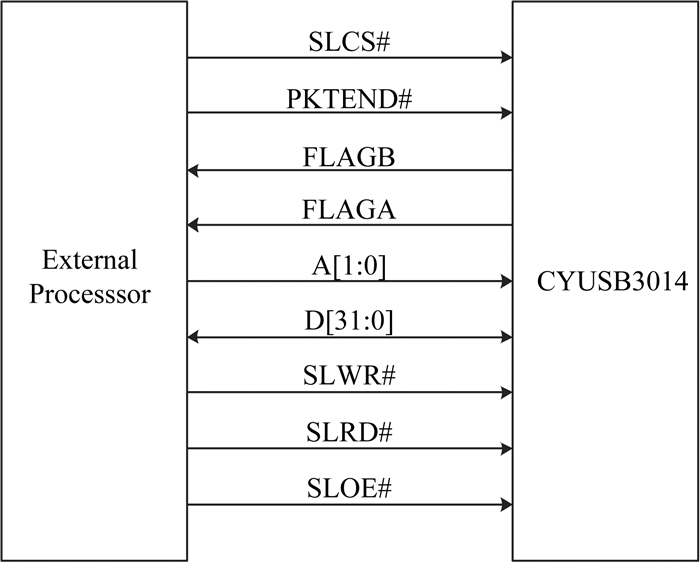

另外,FPGA对浮点数的运算可以通过数的定标实现.USB3.0芯片接口按照SLAVE FIFO接口协议设计,SLAVE FIFO接口协议如图 5所示,它具有高速、可编程、通用等特点,而且还能与外部硬件设备进行无缝相接.USB3.0芯片的接口在SLAVE FIFO工作模式下的时序逻辑由外部控制器FPGA控制.

|

图 5 USB3.0芯片接口 Fig. 5 USB3.0 chip interface |

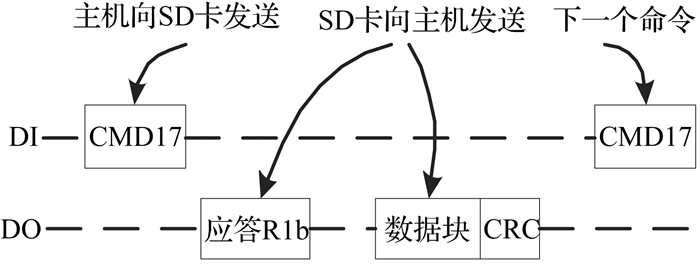

SD卡协议分为SD总线模式和SPI总线模式,SPI总线模式的数据传输属于单通道传输,而SD总线模式的数据传输属于多通道传输.SD卡在握手成功后默认选择SD总线模式,通过拉低CS信号和发送复位命令可使SD卡选择SPI总线模式.在SD总线模式下,SD卡的9针引脚名称分别是CMD、VSS1、VDD、CLK、VSS2、DAT0-DAT3.命令信号和应答信号都是通过CMD引脚传输,具体数据信号则通过DAT0-DTA3引脚传输.按照SD总线模式向SD卡写入多块数据,如图 6所示,当SD卡与主机握手成功后,主机通过引脚CMD发送命令CMD25, SD卡通过应答命令响应,若收到命令不合法则通过应答命令R1来要求重新发送;否则通过应答命令R1b来进行下一步.进一步SD卡收到数据并判断是否合法,若合法则存储,否则通过引脚CMD回应命令R1来要求重新发送数据.SD卡正在传输数据的时候处于忙状态,若收到其他传输命令则通过应答信号R1b响应;若收到命令CMD12,则终止传输.在SPI总线模式下,SD卡的9针引脚仅7针脚有效,它们分别是CS、VSS1、VDD、CLK、VSS2、DI、DO.所有的命令信号是通过DI引脚传输到SD卡,数据信号和应答信号则通过DI和DO引脚传输.按照SPI总线模式从SD卡中读取单块数据如图 7所示,主机通过引脚DI发送命令CMD17,SD卡发送应答信号响应.进而通过DO发送单块数据,一直循环操作直到传输结束.在传输过程中,可以通过命令CMD12终止传输.SD卡传输数据块的长度由命令CMD16事先定义(默认为512字节).复位命令CMD0可以对SD卡进行初始化,总线宽度默认是4根信号线,可用命令CMD6来重新设置总线宽度,SD卡在一个命令传输或者数据处理后会跟随8个时钟周期,确保主机或者从机有时间完成相应动作.每个数据块在传输之前会被标记,通过在数据块起始位置添加一个字节来判定数据的地址和错误等,例如单块数据读取对应的内容首字节为“11111110”.

|

图 6 SD总线模式写多块数据 Fig. 6 SD bus mode write multiple blocks of data |

|

图 7 SPI总线模式读单块数据 Fig. 7 SPI bus mode read block data |

SD卡的所有命令和信号都具备起始位“0”、终止位“1”等特点.所有命令CMD的格式大小都是6字节长度,例如命令CMD24格式中对应的第一个字节为“01011000”.命令字节R1和R1b格式组成:起始位为“0”、结束位为“1”、其他位为“0”.数据帧的格式包括帧头、具体数据、CRC16校验以及帧尾.汉字编码是基于机内码,而其他字符编码是基于ASCII码,因此汉字由2个字节组成,而其他字符由一个字节组成.

下面举例说明监听模拟信号的数字化.如图 8所示,当图像传输到SD卡时,FPGA对监听到的二进制信号进行译码,即转成ASCII码.图中“001100000000000000110000000000000011000000000001001100000000000100110000000000000011000000001000”会对应转化为“001108”.其中转化后的ASCII码“D8”代表图像开始(图像头字节),“C0”代表图像帧开始,“001108”对应转化为图像第一个像素,进而依次对应其他像素,“D9”代表图像结束(图像尾字节).上位机将译码结果写入空图文件,即完成图像还原.

|

图 8 监听模拟信号的数字化 Fig. 8 Analog signal digitization |

设M(x)为信息多项式,G(x)为生成多项式,得到的循环冗余校验(cyclic redundancy check,CRC)位数为r,则M(x)左移r作模2除法,得到的商为Q(x),余数多项式R(x)即是信息多项式的CRC校验码,可表示函数式(1),

| $ \frac{{M\left( x \right) \cdot {x^r}}}{{G\left( x \right)}} = Q\left( x \right) + \frac{{R\left( x \right)}}{{G\left( x \right)}}. $ | (1) |

| $ \frac{{M\left( x \right) \cdot {x^r}-R\left( x \right)}}{{G\left( x \right)}} = Q\left( x \right) + 0. $ | (2) |

式中:xr表示移位系数(即左移r位),Q(x)表示商多项式.

读取信息数据和CRC校验码时,用相同的生成多项式进行校验.如果校验结果错误,那么证明数据信息丢失或者已被破坏, 可表示函数式(2),余数多项式结果为0则表示正确,即利用查表法来实现CRC校验.

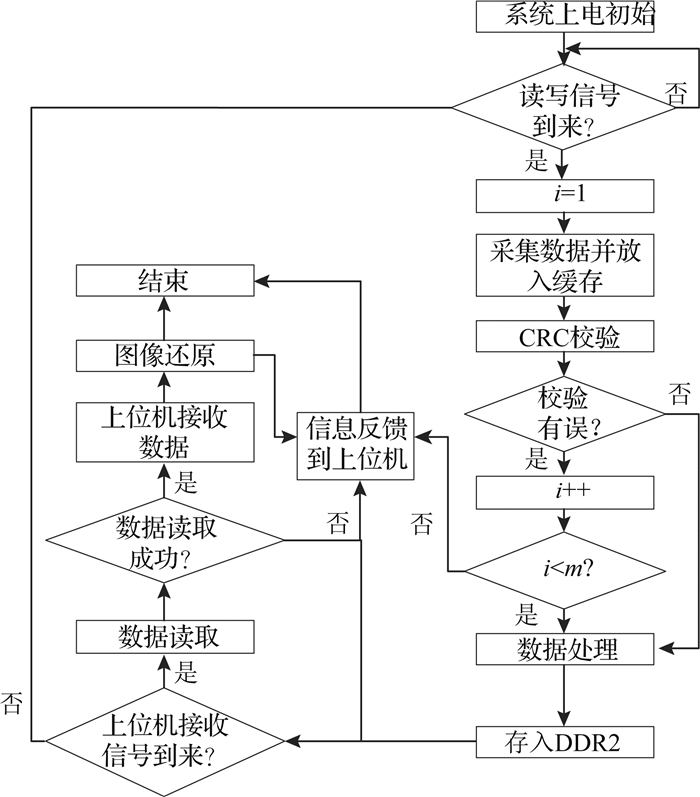

1.4 FPGA程序设计如图 9所示,硬件系统上电初始并复位.当上位机发送读写信号后,FPGA接收命令然后通过并行引脚端监听数据.进而放入缓存等待下一步CRC校验,FPGA则利用FIFO进行缓存并同时进行CRC校验.若CRC校验错误达到一定数量则反馈信息到上位机并结束,否则进行下一步数据处理.数据处理包括浮点数定标、数据校验、数据译码、数据存储等.在数据处理结束后,FPGA利用FIFO缓冲区存入DDR2并发送反馈信息给上位机.直到上位机的接收信号到来,FPGA利用FIFO缓冲区从DDR2读出数据发送给上位机,上位机接收到数据进而直接还原成图像.

|

图 9 FPGA程序设计流程 Fig. 9 FPGA programming flow |

实验中以FPGA作为控制芯片.FPGA为各个功能建立相对独立的硬件,实现应用程序所要求的逻辑功能,它具备了并行计算的内在特点.硬件设计使其具有较高的运行速度,同时又以相对较低的成本保持其所具有灵活可重新编程特点.对于流水线结构来说,可为流水线上每一个阶段操作建立相对独立的硬件.在数据同步系统中,数据简单地从一个操作输出传递到下一个操作输入;如果数据是不同步的,可在操作之间加入适当的缓冲区,以处理数据流或存取模式的变化.实验中通过使用并行硬件展开内部循环,以代替顺序执行操作.

如图 10所示,通过USB3.0数据线为电路板提供电源.时钟选用50 MHZ晶振和19.2 MHZ晶振分别为FPGA芯片和USB3.0芯片提供脉冲信号,其中FPGA芯片型号选用EP3C16F484,它会接收相应引脚的并行信号,然后对其进行浮点数定标、CRC校验、译码、存储等操作;其中USB3.0芯片内固化有可执行的中间程序,利用配置的并行通用可编程接口GPIF Ⅱ与FPGA连接.通过USB3.0芯片的UART接口,PC对FPGA进行直接控制传输或者直接发送传输指令,实现FPGA、PC、USB3.0芯片三者之间的通讯.

|

图 10 图像预处理系统基本结构框图 Fig. 10 Structure of image preprocessing system |

USB3.0芯片实现PC和FPGA之间的数据传输,负责解释USB3.0协议以及进行数据的编码和解码等操作,是组成USB功能设备的必需器件.一般情况下,USB3.0芯片包含多个驱动外围电路的IO口,用来实现USB3.0设备的一些特殊功能.USB3.0接口芯片大致分为3种:第1种是外接微控制器的芯片,第2种是集成微控制器的芯片,第3种是桥接芯片.外接微控制器的芯片缺点是会受所选控制器的限制而且还要另外开发底层驱动.集成了微处理器的芯片,其缺点是要单独开发系统,成本较高,并且需要编写底层驱动程序.这种外接微控制器的价格相对也较为昂贵,芯片的可选范围较小.USB3.0桥接芯片,此类芯片价格实惠,开发简单,包含功能控制器、USB3.0收发器、振荡器,带有全部调制解调器控制信号的异步串行数据总线.通常在选择芯片的时候,根据系统的要求还要考虑以下指标:数据的传输速度、程序/数据存储器容量、芯片封装、系统功耗、性价比、电源要求以及开发的难易程度等.在本设计中,USB3.0接口芯片型号选择CYUSB3014, 主要原因是该芯片具有高的数据传输速度,以及体积小、性价比高、易于开发、电路简单、系统功耗低等特点.CYUSB3014是FPGA与PC之间的通讯桥梁,PC直接控制FPGA进而控制所有模块,FPGA控制电路的其他模块传输数据并反馈给PC.FPGA通过USB3.0芯片和PC通讯,接收PC的传输指令.PC发送传输指令给FPGA,进而接收FPGA储存在DDR2中的数据和FPGA的反馈信号.终端设备PC可观测到数据传输时间和图像结果.

模数转换芯片型号选用ADC0809,它受FPGA控制,由FPGA为它提供时钟脉冲并将接收到的模拟信号转化为数字信号最终传输给FPGA.当上位机PC通过USB3.0数据线发送传输指令给FPGA时,FPGA则对接收的数字信号进行计算、CRC校验和存储等处理,并等待上位机指令进而传输数据给上位机.

其中FLASH芯片型号选用M25P64作为FPGA和USB3.0芯片配置芯片,用来储存固化有可执行的中间程序.该芯片若有固化有可执行的中间程序,断电仍然保存.FPGA通过其配置芯片中固化有可执行的中间程序,实现对电路中各个模块的控制.USB3.0芯片通过其配置芯片实现对USB3.0数据线的高速传输.FPGA和USB3.0芯片内含有可在线下载烧写程序的RAM,可以在线烧写相应可执行的中间程序,它具有断电易失性.其中DDR2芯片选用MT47H64M16HR,通过同步FIFO模式与FPGA进行通讯,实现FPGA对DDR2的控制和数据存储,保证数据的可靠性,不会因为过多数据的无法存储和传输丢包的问题而造成数据丢失.

实验电路板上各个模块受FPGA控制,而FPGA通过USB3.0受上位机控制.电路板采用8层电路,按工业标准设计.FPGA和USB3.0芯片及FPGA与外部IO接口之间的走线均采用等长设计,保证高速信号的可靠传输.FPGA的IO接口均采用外接上拉电阻的方式,增大IO接口的驱动能力,避免造成无法接收数据等问题.DDR2芯片采用独立的地址、控制和数据总线.FPGA为电路板的核心控制模块,PC控制其收集数据并实时还原成图像.

实验设备如图 11所示,采用佳能500D机身和佳能EF 50MM F/1.8 Ⅱ定焦镜头进行拍摄,其中CMOS尺寸为22.3 mm×14.9 mm,图像解析度为4 752(H)×3 168(V)像素,电脑配置为P4 3.0G、4GB RAM.SD卡通过设计的外挂硬件与相机相连,其相应接口同时与实验板中的FPGA相连,相机和其他硬件分别独立供电.相机采样并把图像存入SD卡中时,实验板中的FPGA对SD卡进行实时监听,通过数模芯片把接收到的模拟信号转化为数字信号,进一步对数字信号进行浮点数定标、CRC校验、译码等,然后通过FIFO缓冲储存到DDR2中.基于C++编写用于FPGA通信和控制下位机的软件界面如图 12所示,上位机通过安装USB3.0芯片等相应硬件的驱动和导入相关的固件即完成通信,最后把接收到的数据直接还原成相应的图像.

|

图 11 实验设备硬件 Fig. 11 Experimental equipment hardware |

|

图 12 上位机控制下位机软件 Fig. 12 Software of PC coercion |

实验通过监听采样获得如图 13(a)所示的图像,而其原始采样图为图 13(b)所示,可通过做差的方式来确定两者的差异.通过对实验样本的大量检测发现两者并无差异,所以本文提出的监听传输方式是稳定且可靠的.试验中,该部分图像预处理工作在FPGA中完成.

|

图 13 上位机和相机采样对比 Fig. 13 Comparison of PC and camera sampling |

为进一步验证本文方法的有效性,实验将传统基于USB2.0传输方法与本文方法进行对比,分别记录相机按下快门到上传图像结束所需要的时间.如表 1所示,表中t2i为USB2.0传i张图像所需时间,t3i为USB3.0传i张图像所需时间,利用USB2.0上传一张1 500万像素(4 752×3 168)无压缩数据格式的图像时,从相机按下快门到上位机成功接收大约需要4.4 s的时间.在同等情况下,利用本文FPGA监听结合USB3.0方法仅需要1.6 s左右的时间.通过表 1的对比数据可知,使用本文方法的传输效率比传统基于USB2.0的快将近2倍.

| 表 1 采样和上传图像所需时间对比 Table 1 Comparison of time for sample and upload images |

事实上,表 1的实验数据不仅包含了传输时间还包含了相机由按下快门开始到曝光结束的采样时间.若进一步将这部分“拍照时间”进行剥离,可得到对应的如表 2所示.因此,表 2仅对比了传输时间,进而可更准确地比较本文方法和传统方法涉及的传输速度.从表 2中看出,利用USB2.0传输一张图像平均用时为3.4 s,而使用本文方法为0.6 s,USB2.0的传输耗时约是本文设计硬件系统的6倍.

| 表 2 上传图像所需时间对比 Table 2 Comparison of time for upload images |

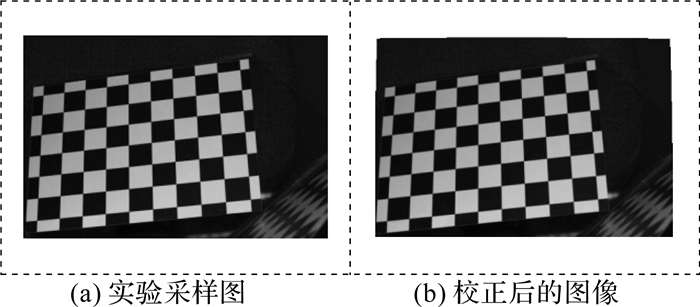

如表 3所示为采样包含预处理的耗时对比,表中,t21PC、t31PC分别为USB2.0和USB3.0传1张图像并用PC校正的数据.相机原始采样图为如图 14(a)所示,系统利用离线标定结果进行校正后的图像为如图 14(b)所示.实验对比了将该预处理过程从PC端前移至FPGA时的用时情况.

| 表 3 采样和上传1张图像并校正所需时间对比 Table 3 Comparison of time for transfer image and calibration |

|

图 14 实验采样校正前后对比 Fig. 14 Comparison of experimental samples before and after calibration |

实验表明,传统采样并在PC端进行预处理的耗时约为7.6 s,而若将预处理过程前移至FPGA,则只需要约3.0 s.

3 结语本文研究一种基于FPGA监听和USB3.0传输的图像预处理方法,在不损坏相机原有结构的基础上,通过外挂监听的方式对图像数据进行实时采集与预处理操作,最终达到快速获取经预处理的归一化图像目的.经过硬件加速处理,上位机在短时间内即可获得图像.实验结果表明,该系统及相应图像预处理方法具有更高效的图像预处理与传输能力,从而整体提高了图像采集的效率.它还具有接口友好、性能稳定、集成度高、使用灵活和实用性强等特点,因此可在诸如机器视觉、视觉导航、立体视觉、模式识别等领域应用.

| [1] |

ZHOU Jia-li, JIA Lu-shuai, WU Min. Flexible Calibration Method with high accuracy for Dynamic Focusing[J]. Pattern Recognition and Artificial Intelligence, 2016, 29(6): 481-491. |

| [2] |

周佳立, 张树有, 杨国平. 基于双目被动立体视觉的三维人脸重构与识别[J]. 自动化学报, 2008, 35(2): 123-131. ZHOU Jia-li, ZHANG Shu-you, YANG Guo-ping. A 3D face reconstruction and recognition method based on passive binocular stereo vision[J]. Acta Automatica Sinica, 2008, 35(2): 123-131. |

| [3] |

胡湘娟, 杨毅, 曾贤东. 嵌入式数码相机的设计与实现[J]. 计算技术与自动化, 2004, 9(24): 49-51. HU Xiang-juan, YANG Yi, ZENG Xian-dong. Design and implementation of embedded digital camera[J]. Computing Technology and Automation, 2004, 9(24): 49-51. |

| [4] |

韩春雷, 王库, 马健. 一种数码相机成像和视频处理前端的设计[J]. 新器件新技术, 2014, 33(3): 101-104. HAN Chun-lei, WANG Ku, MA Jian. Design of a digital camera imaging and video processing front end[J]. New Device New Technology, 2014, 33(3): 101-104. |

| [5] |

杨翠翠, 朱向东, 李帆. 基于USB3.0协议的PC与FPGA通信系统的设计[J]. 电子科技, 2014, 27(10): 136-138. YANG Cui-cui, ZHU Xiang-dong, LI Fan. Design of PC and FPGA communication system based on USB3.0 protocol[J]. Electronic Science and Technology, 2014, 27(10): 136-138. DOI:10.3969/j.issn.1007-7820.2014.10.037 |

| [6] |

蔡金. 嵌入式高清工业相机研究与实现[D]. 杭州: 浙江大学, 2013. CAI Jin. Rsearch and implementation of embedded HD camera[D]. Hangzhou: Zhejiang University, 2013. http://www.wanfangdata.com.cn/details/detail.do?_type=degree&id=Y2297989 |

| [7] |

MARIA D, ELIO A. A low cost FPGA based USB device core[C]//Southern Conference on Programmable Logic. 4th IEEE Conference on. [S. l. ]: IEEE, 2008: 149-154. http://ieeexplore.ieee.org/document/4547747/?arnumber=4547747&sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number:4547716)%26pageNumber%3D2

|

| [8] |

WANG P, WU C. Design of dual-channel high-speed data acquisition card based on USB 3.0 and FPGA[J]. Advanced Manufacturing Technology Icmse, 2012. |

| [9] |

SRINIVASAN R, ANUPAMA K, SAHA S K, et al. FPGA based ASM implementation for CCD camera controller[C]//International Conference on Emerging Trends in Electronic and Photonic Devices & Systems. [S. l. ]: IEEE, 2009: 170-172. http://ieeexplore.ieee.org/document/5441144/?reload=true&arnumber=5441144

|

| [10] |

AMBROSCH K, HUMENBERGER M, KUBINGER W, et al. Extending two non-parametric transforms for FPGA based stereo matching using bayer filtered cameras[C]//Computer Vision and Pattern Recognition Workshops, 2008. CVPRW'08. IEEE Computer Society Conference on. [S. l. ]: IEEE, 2008: 1-8. http://ieeexplore.ieee.org/document/4563146/

|

| [11] |

HARINARAYAN R, PANNERSELVAM R, ALI M M, Et al. Feature extraction of digital aerial images by FPGA based implementation of edge detection algorithms[C]//2011 International Conference on Emerging Trends in Electrical and Computer Technology (ICETECT). [S. l. ]: IEEE, 2011: 631-635. http://ieeexplore.ieee.org/document/5760194/

|

| [12] |

JIANLAI W, CHUNLING Y, MIN Z, et al. Implementation of Otsu's thresholding process based on FPGA[C]//4th IEEE Conference on Industrial Electronics and Applications. [S. l. ]: IEEE, 2009: 479. http://ieeexplore.ieee.org/document/5138252/

|