2. 中国科学院自动化研究所 国家专用集成电路设计 工程技术研究中心, 北京 100190

2. National ASIC Design Engineering Center, Institute of Automation, Chinese Academy of Sciences, Beijing 100190, China

集成电路制造技术已经进入纳米时代, 随着器件特征尺寸的降低和集成电路复杂化的提升, 静电放电(electrostatic discharge, ESD)问题越来越成为集成电路中最主要的可靠性问题之一[1].常见的ESD器件有BJT, MOS管, 可控硅(silicon controlled rectifier, SCR)等.其中SCR类器件具有单位面积泄放电流大、寄生电容小的优点, 成为新型ESD防护器件的研究热门[2].

对于一些存在共模电压的总线接口, 比如RS232/RS485/RS422/CAN等接口芯片, 需要双向的ESD防护结构进行I/O口的正负ESD防护[3], 如采用2个ESD防护器件堆叠来进行双向防护, 不仅会占用过大的版图面积, 而且会引入额外的寄生效应.因此, 需要设计一个能够同时进行双向防护的双向可控硅(dual-direction silicon controlled rectifier, DDSCR)器件来解决上述问题.

DDSCR防护器件设计窗主要包含3个关键的指标, 分别是触发电压, 维持电压和二次击穿电流.其中触发电压要小于内部电路的栅氧击穿电压; 维持电压要大于内部电路的工作电压[4]; 二次击穿电流越大, ESD防护器件鲁棒性越高.在对于触发电压和维持电压的改进方面:Liu等[5]提出一种低触发电压的双向SCR结构[5]; Wang等[6]研究了低触发电压, 维持电压可调的双向SCR结构[6]; Vashchenko对触发电压和维持电压都进行了研究调整[7], 梁海莲等[8]提出了改进型的双向SCR结构并优化关键尺寸以满足窄小的ESD设计窗口.针对二次击穿电流值的提高, Guo等[9-10]提出通过改变金属走线提高双向SCR的鲁棒性.但上述研究中均未对双向SCR结构与二次击穿电流之间的关系开展研究.

本文在传统DDSCR结构基础上, 提出了改进型DDSCR器件结构, 通过在N阱中加入N+注入区(DDSCR_N+)和在N阱中加入P+注入区(DDSCR_P+), 可以在保持触发电压和维持电压前提下, 提升二次击穿电流, 从而达到了更强的ESD鲁棒性.

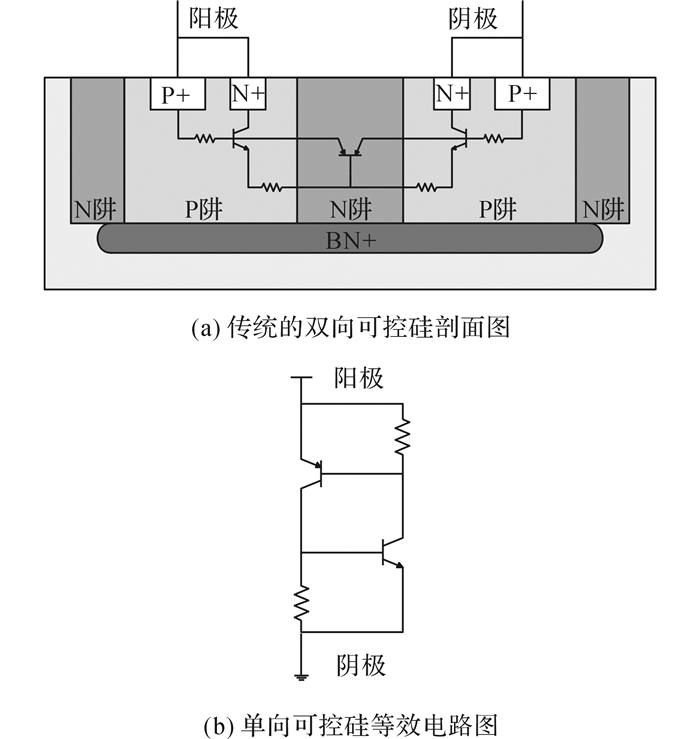

1 DDSCR的ESD原理分析 1.1 DDSCR的防护机理对于DDSCR器件, 在正向或反向ESD脉冲作用下, 利用其内部反偏的PN结形成具有相同PNPN特性的ESD电流泄放路径, 来实现对称性的双向ESD防护.同时, DDSCR类器件又可减小芯片面积, 提高单位面积ESD防护效率.如图 1(a)所示为传统的DDSCR剖面图及其对应的(b)单向SCR等效电路图.

|

图 1 传统的DDSCR剖面图及其对应的单向SCR等效电路图 Fig. 1 Cross-sectional view of conventional DDSCR and equivalent schematic diagram of SCR |

在传统的DDSCR中, 2个P阱各包含一个高掺杂的N+注入区和P+注入区.该结构同时存在3个寄生的三极管, 分别是器件两边的寄生NPN三极管和器件中间的寄生PNP三极管, 从而形成两路PNPN电流泄放路径, 即双向的SCR结构.

正向ESD脉冲作用在Anode时, Cathode侧寄生NPN晶体管的PN结(N-WELL/P-WELL)是反偏的, 达到雪崩击穿后产生大量的电子空穴对, 产生雪崩倍增电流.一旦寄生P阱(Cathode侧)电阻上的电压降达到足够大, 寄生NPN晶体管的发射结触发导通, 电流上升.随之该电流又在N阱电阻上产生电压降, 寄生PNP管触发导通, 从而形成了正反馈的闭合回路, 2个寄生晶体管进入饱和区, 泄放ESD电流.反之, 当反向的ESD脉冲作用在Anode时, 等效于正向的ESD脉冲作用于cathode.因为该结构是对称的, 所以这和在Anode侧加正向ESD脉冲是类似的, 但是雪崩击穿的PN结发生在Anode侧的P-WELL/N-WELL.综上所述, 该结构可以提供双向的具有回滞特性(S形I-V曲线)的ESD保护.

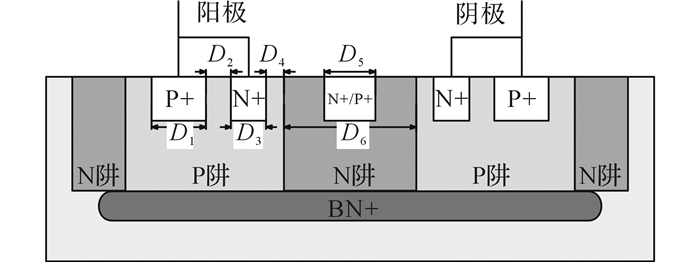

1.2 改进型的DDSCR结构本文在传统的DDSCR结构中间的N阱中对称加入了N+注入区(DDSCR_N+)或P+注入区(DDSCR_P+), 具体结构剖面如图 2所示.N阱中的N+注入区或P+注入区可以提供大量载流子, 增加寄生PNP三极管的基区电子浓度.电子对在基区的复合和电离的浓度加大, 从而促进寄生三极管的开启和对电流的泄放, 提高了ESD的放电能力.此外, 改进型的DDSCR结构和传统结构的器件尺寸和版图设计均相同.

|

图 2 N阱中间加入N+注入区(DDSCR_N+)或P+注入区(DDSCR_P+)的DDSCR结构剖面图 Fig. 2 Cross-sectional view of DDSCR structure with additional N+ implant (DDSCR_N+) or additional P+ implant (DDSCR_P+) in NWELL |

本文选用Silvaco公司的ATLAS仿真软件对DDSCR的物理机制进行仿真分析, 分别对传统的DDSCR, DDSCR_N+和DDSCR_P+进行直流仿真.在器件的阳极施加ESD脉冲, 模拟器件在ESD应力下的电学特性.3种结构的仿真剖面结构尺寸相同, 与实际流片的版图尺寸一致, 相关参数参照表 1(各参数含义见图 2).

| 表 1 仿真的DDSCR结构尺寸参数 Table 1 Size parameters of the simulated structure of the DDSCR |

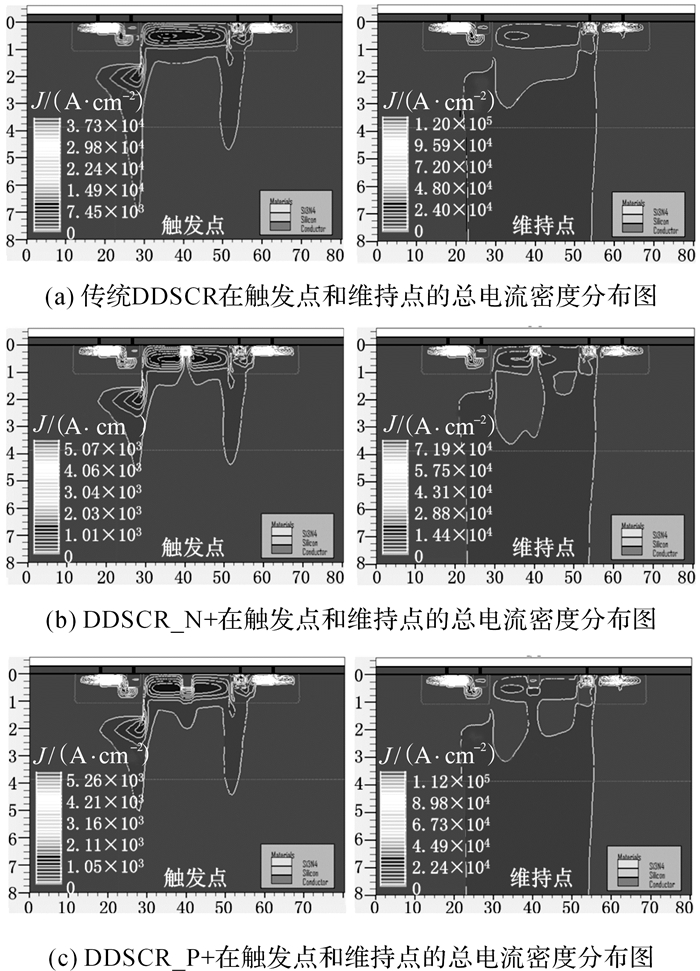

同时, 其他仿真参数设置一致, 只观察不同的剖面图结构对器件性能的影响, 即N阱中N+或P+注入对器件鲁棒性的影响.如图 3(a)所示为传统DDSCR在触发点和维持点的总电流密度J分布图;(b)是DDSCR_N+在触发点和维持点的总电流密度分布图;(c)是DDSCR_P+在触发点和维持点的总电流密度分布图.

|

图 3 传统DDSCR, DDSCR_N+和DDSCR_P+在触发点和维持点的总电流密度分布图 Fig. 3 Total current density of conventional DDSCR, DDSCR_N+ and DDSCR_P+ at triggering and holding point |

图 3中总电流密度大小由不同颜色区分, 具体数值显示在图中左下方区域.从图中可以看出, 3个结构在雪崩击穿发生时电流主要集中分布在器件的表面区域, 随着器件进入回滞(snapback), SCR结构完全开启泄放ESD电流, 电流分布趋于器件体内.由于3个结构的工作机理相同, 器件尺寸相同, 其电流分布面积在触发点和维持点也大致相同, 但是N+或P+注入区的加入改变了电流密度数值, 随之影响了DDSCR的鲁棒性能.其中, DDSCR_N+结构在触发点和维持点的总电流密度极值最小, 分别为5.07×103和7.19×104 A/cm2;DDSCR_P+结构次之, 在触发点和维持点分别为5.26×103和1.12×105 A/cm2;传统DDSCR的总电流密度极值最大, 在触发点和维持点分别为3.73×104和1.20×105 A/cm3.在相同的情况下, 总电流密度值较小的结构能够承受更高的电压, 从而拥有更强的ESD鲁棒性.

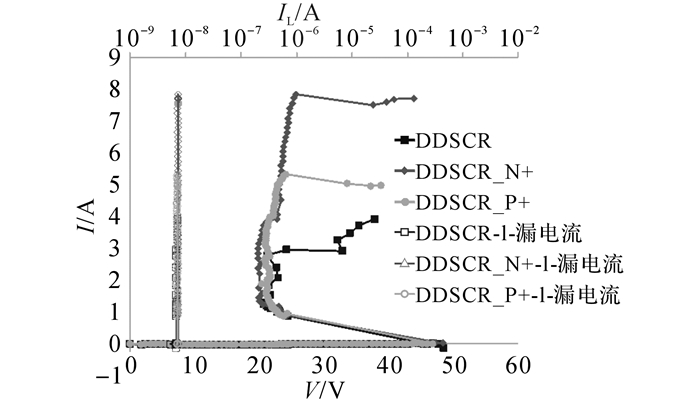

2.2 TLP测试基于华润上华0.5 μm BCD工艺流片制备了传统的DDSCR及其改进结构, 利用TLP 6000 Series测试系统进行传输线脉冲测试来表征DDSCR的ESD防护特性.TLP测试脉冲波形上升时间是5 ns, 脉冲宽度100 ns, 每施加一次TLP测试脉冲, 同时进行器件的漏电流测试.传统的DDSCR, DDSCR_N+及DDSCR_P+结构均为完全对称结构, 版图绘制完全对称, 正反向TLP测试结果大致相当, 给出正向的TLP测试结果进行比较分析.3个结构的正向TLP测试结果曲线如图 4所示, 其中V为电压,I为电流,IL为漏电流.相应的TLP测试结果数据如表 2所示.表中, Vt1为触发电压, Vh为维持电压, It2为二次击穿电流.

| 表 2 DDSCR, DDSCR_N+和DDSCR_P+的TLP测试数据 Table 2 TLP testing data for DDSCR, DDSCR_N+ and DDSCR_P+ |

图 4中3个器件的漏电流在二次击穿前都在纳安级别的范围, 因此可以有效地应用到I/O接口, 并且减少漏电损失对内部电路正常工作所带来的影响.传统的DDSCR及N阱中加入N+注入(DDSCR_N+)和P+注入(DDSCR_P+)的改进型DDSCR结构的触发电压Vt1分别为48.394、48.309、46.786 V;维持电压Vh分别为20.669、19.948、21.259 V.由于3个器件的触发的PN结相同, 即N阱和P阱所形成的PN结, 且剖面图横向尺寸相同, 所以触发电压和维持电压大致相当[12].

|

图 4 传统的DDSCR, DDSCR_N+和DDSCR_P+结构的TLP测试I-V曲线 Fig. 4 I-V curves of conventional DDSCR, DDSCR_N+ and DDSCR_P+ from TLP testing |

二次击穿电流是ESD防护器件能够承受的最大电流, 是衡量ESD鲁棒性的重要指标.3个器件的ESD二次击穿电流It2分别是2.962, 7.719和5.328 A, DDSCR_N+结构的It2相比传统的DDSCR提升了160%, DDSCR_P+结构的It2提升了79.8%.该测试结果与仿真结果相符, 证明了N+注入区和P+注入区对于ESD防护器件性能的影响, 即DDSCR_N+和DDSCR_P+结构的耐压能力更强, ESD鲁棒性更好.同时, DDSCR_N+结构比DDSCR_P+结构的二次击穿电流更大, 拥有更强的ESD鲁棒性.

3 结语本文基于华润上华0.5 μm BCD工艺, 制备了传统DDSCR结构以及2种改进型DDSCR结构:DDSCR_N+, DDSCR_P+.并且进行了TCAD软件的仿真和TLP测试.仿真和测试结果表明, 改进型的DDSCR器件和传统的DDSCR器件的触发电压和维持电压大致相同.其中, DDSCR_N+结构具有最高的二次击穿电流, 因此该结构ESD耐压能力强, 鲁棒性好, 能够更好的应用在要求较高的I/O端口上.在后续的工作中, 将会进一步考察器件的关键尺寸对触发电压和维持电压的调整以满足对双向ESD防护结构设计窗口的特殊要求.

| [1] | DUVVURY C. ESD protection device issues for IC designs[C]//2001 IEEE Custom Integrated Circuits. San Diego, USA:IEEE, 2001:41-48. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=929720 |

| [2] | KER M D, HSU K C. Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits[J]. IEEE Transactions on Device and Materials Reliability, 2005, 5(2): 235–249. DOI:10.1109/TDMR.2005.846824 |

| [3] | SALCEDO J A, LIOU J J, BERBIER J C. Design and integration of novel SCR-based devices for ESD protection in CMOS/BiCMOS technologies[J]. IEEE Transactions on Electron Devices, 2005, 52(12): 2682–2689. DOI:10.1109/TED.2005.859662 |

| [4] |

李冰, 王刚, 杨袁渊. 基于SCR的ESD保护电路防闩锁设计[J].

微电子学, 2009, 39(6): 786–789.

LI Bing, WANG Gang, YANG Yuan-yuan. Latch-up free design of SCR-based ESD protection circuits[J]. Microelectronics, 2009, 39(6): 786–789. |

| [5] | LIU Z W, VINSON J, LOU L F, et al. An improved bidirectional SCR structure for low-triggering ESD protection applications[J]. IEEE Electron Device Letters, 2008, 29(4): 360–362. DOI:10.1109/LED.2008.917111 |

| [6] | WANG Y, JIN X L, YANG L, et al. Robust dual-direction SCR with low trigger voltage, tunable holding voltage for high-voltage ESD protection[J]. Microelectronics Reliability, 2015, 55(3): 520–526. |

| [7] | VASHCHENKO V A, HOPPER P J. New dual-direction ESD device in Si-Ge BiCMOS process[C]//2010 IEEE 10th International Conference on Solid-State and Integrated Circuit Technology. Shanghai:IEEE, 2010:935-937. http://ieeexplore.ieee.org/document/5667487/ |

| [8] |

梁海莲, 董树荣, 顾晓峰, 等. 基于0.5 μm BCD工艺的双向SCR结构的ESD保护设计[J].

浙江大学学报:工学版, 2013, 47(11): 2046–2050.

LIANG Hai-lian, DONG Shu-rong, GU Xiao-feng, et al. ESD protection design of DDSCR structure based on the 0.5 μm BCD process[J]. Journal of Zhejiang University:Engineering Science, 2013, 47(11): 2046–2050. |

| [9] | GUO W, LI M L, DONG S R. Effect of metal routing on the ESD robustness of dual-direction silicon controlled rectifier[C]//2009 IEEE 16th International Symposium on the Physical and Failure Analysis of Integrated Circuits. Suzhou:IEEE, 2009:336-338. http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=5232637 |

| [10] | DU X Y, DONG S R, HAN Y, et al. Analysis of metal routing technique in a novel dual direction multi-finger SCR ESD protection device[C]//2008 IEEE 9th International Conference on Solid-State and Integrated Circuit Technology. Beijing:IEEE, 2008:337-340. http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4734540 |

| [11] | LEE J C, YOUNG R, LIOU J J, et al. An improved transmission line pulsing (TLP) setup for electrostatic discharge (ESD) testing in semiconductor devices and ICs[C]//2001 IEEE International Conference on Microelectronic Test Structures. Kobe:IEEE, 2001:233-238. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=928668 |

| [12] | WANG Y, LU G Y, ZHANG L Z, et al. Comprehensive study and corresponding improvements on the ESD robustness of different nLDMOS devices[C]//2014 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits. Marina Bay Sands, Singapore:IEEE, 2014:304-307. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=6898177 |