随着芯片面积的增大和工作频率的提升, 在芯片内部实现稳定、低偏斜的同步时钟信号传输成为一项极具挑战性的工作.传统时钟系统为了确保芯片各区域时钟负载点的时钟信号偏斜满足要求, 需要加入大量的时钟驱动器, 这些时钟驱动器将引入可观的时钟功耗.这些时钟驱动器容易受到所在区域实际工作电压、工作温度的影响, 导致时钟偏斜大于预期结果.同时, 分布广泛的时钟驱动器在生产过程中受工艺偏差的影响很大, 导致芯片不同部分的时钟偏斜进一步加大.

多时钟源设计、全局异步局部同步等新型时钟结构部分缓解了时钟偏斜、时钟功耗等方面的问题, 但面临着高频信号的反射问题, 难以彻底解决传统时钟面临的设计困难.采用振荡方式生成和分布时钟具有低功耗、低偏斜、高可靠等优点, 长期以来受到了广泛的关注和研究.这些结构包括了LC耦合振荡器[1-2]、分布振荡器[3]、行波振荡器(travalling-wave oscillator, TWO)[4]、驻波振荡器(standing-wave oscillator, SWO)[5-10]等.Gauthaus等[11-12]分析了各类振荡时钟的设计方法以及面临的主要挑战, 其中驻波振荡器可以在较大范围内提供相位偏差接近于0的高频时钟信号, 具有容忍电压、温度波动和工艺偏差的特性[13], 因此更适合应用在集成电路设计中.由于芯片实际使用时往往要求工作在一定频率范围内, 将驻波振荡器作为芯片时钟源必须解决在较宽的频率范围内进行调节的难题.

本文设计基于反型金属氧化物半导体场效应晶体管(inversion mode MOSFET, IMOS)的变容二极管(varactor)结构并集成在驻波振荡器中, 通过仿真分析该结构可变电容的不同分布方式对频率调节范围和功耗的影响.本文基于该驻波振荡器, 设计针对不同类型芯片的时钟系统, 通过仿真测试了这些时钟系统在不同温度、电压波动和工艺偏差下的频率变化.结果表明, 这些系统具有高可靠性的特点.

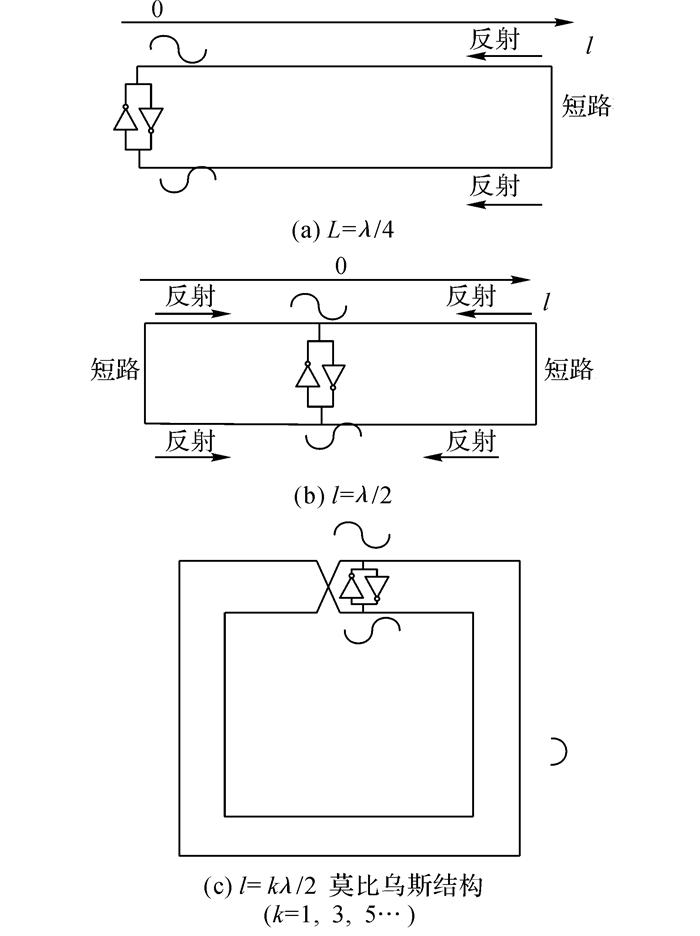

1 驻波振荡器设计 1.1 基本结构图 1列出多种驻波振荡器的结构示意图, 根据传输线长度与振荡频率的关系, 可以分为λ/4驻波振荡器、λ/2驻波振荡器和kλ/2驻波振荡器.所有的驻波振荡器均由两部分组成:差分传输线和交叉耦合反相器组(CCIP).振荡频率为

|

图 1 不同驻波振荡器结构 Fig. 1 Different kinds of standing-wave oscillators |

| $ f = \frac{1}{{2\pi \sqrt {{L_{\rm{W}}}\left( {C + {C_{\rm{W}}}} \right)} }}. $ | (1) |

式中:Lw、Cw为驻波振荡器的寄生电感和寄生电容, C为各类负载的源漏电容和栅电容.一旦驻波振荡器的基本参数确定, 振荡频率就已经确定.为了实现频率调节, 必须找到动态改变Lw、Cw和C的方法.

针对各类驻波振荡器, 学术界已经进行了大量的研究, 不同种类驻波振荡器的结构、振荡条件和关键模块设计方法都得到了详细阐述[5-8], 覆盖更大范围的驻波振荡器结构有了多种研究成果[9-10].其中借鉴行波振荡器的莫比乌斯(Mobius)结构可以实现λ/2驻波振荡器[9], 在此基础上可以进一步实现kλ/2驻波振荡器[10].

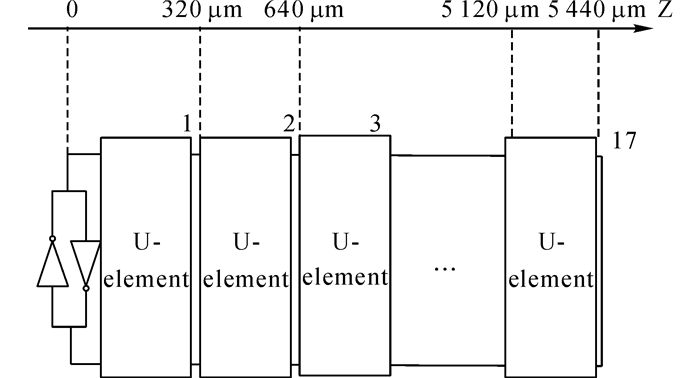

1.2 设计与仿真基于65 nm工艺, 构建了λ/4驻波振荡器的仿真结构, 如图 2所示.图中, 传输线采用HSPICE仿真工具中的基本传输线单元(U-element)来进行模拟.该驻波振荡器传输线总长度为5 440 μm, 共采用17个基本传输线单元.

|

图 2 λ/4驻波振荡器仿真结构 Fig. 2 λ/4 standing-wave oscillator simulation architecture |

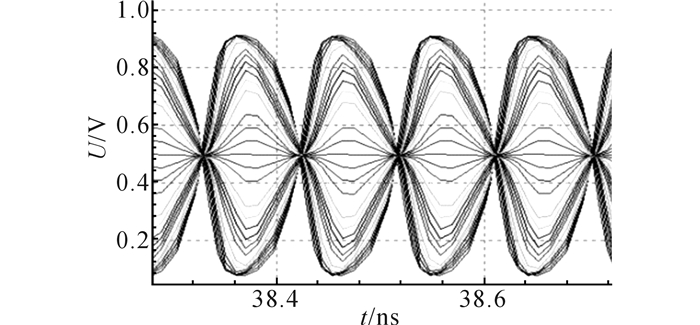

图 2中, 驻波振荡器的基本参数如表 1所示, 各基本传输线单元起始点波形的仿真结果如图 3所示.可以看出, 不同位置的振荡信号相位基本一致.仿真结果表明, 驻波振荡器频率达到5.3 GHz, 功耗为12.2 mW.

| 表 1 λ/4驻波振荡器仿真参数 Table 1 λ/4 standing-wave oscillator simulation parameters |

|

图 3 λ/4驻波振荡器不同位置仿真波形 Fig. 3 λ/4 standing-wave oscillator simulation waveforms |

维持工作电压为1 V, 针对NMOS/PMOS在(typical/typical, slow/slow, fast/fast)三种工艺角(corner)和25、75、125 ℃三种温度不同组合下的仿真发现, 该驻波振荡器的工作频率仅有极微小的变化, 符合对驻波振荡器工艺偏差容忍性的分析[13].可以认为在一定的设计参数范围内, 该结构具有良好的容忍工艺偏差和温度波动的特性.

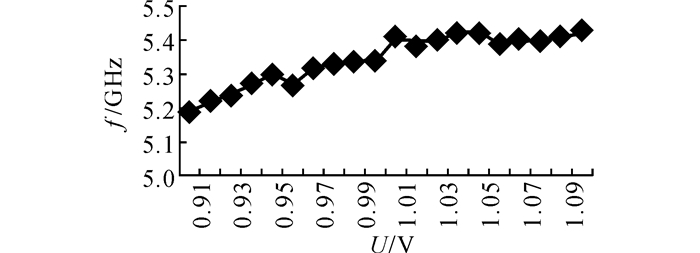

工作电压的变化在一定范围内, 将导致振荡频率的明显变化.如图 4所示, 当维持NMOS/PMOS在Typical/Typical工艺角和75 ℃条件, 工作电压由0.91 V升至1.1 V时驻波振荡器工作频率由5.19 GHz升至5.43 GHz.当工作电压低于0.9 V时, 驻波振荡器不能正常工作, 高于1.1 V时驻波振荡器的工作频率变化很小.这是因为交叉耦合反相器组的寄生电容可以视作驻波振荡器的负载, 该电容与连接点的电压有关, 且电容的显著变化局限在一定电压范围内.与传统基于时钟驱动器的时钟传播方式相比, 驻波振荡器具有对电压变化更好的容忍性[13].

|

图 4 λ/4驻波振荡器不同工作电压时的振荡频率 Fig. 4 λ/4 standing-wave oscillator's frequency under different voltages |

一般情况下, 各类处理器的工作频率要求有20%~50%的调节范围.式(1) 表明, 要实现驻波振荡器的频率调节, 需要找到动态改变Lw、Cw或C的方法.其中Lw、Cw主要由传输线的结构与参数确定, 难于实现动态调整.有的研究通过配置多个差分传输线中处于工作状态的差分线数目来改变Lw、Cw, 从而实现了频率的粗粒度调节[14-15].本文主要通过调节负载电容C来实现驻波振荡器的频率调节.

2.1 可变电容设计采用变容二极管来实现驻波振荡器频率调节的思想由来已久[6, 8], 在CMOS工艺中, 谐振电路常用MOS管来实现变容二极管.基于MOS管的变容二极管分为普通MOS管、反型MOS管和累积型MOS管3种.对3种变容二极管的大信号分析表明, 反型MOS管具有单调的可变电容, 更可靠且在正常工作电压下电容的变化范围最大[16].

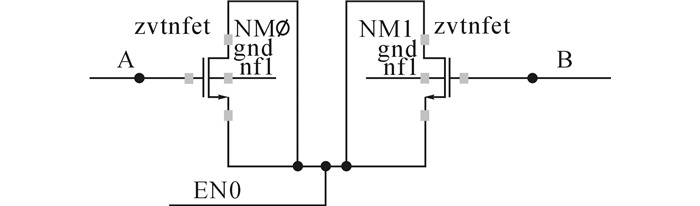

采用反型MOS管来实现变容二极管, 并采用背靠背的连接方式形成连接驻波振荡器差分信号线的负载, 结构如图 5所示.其中A、B端分别接驻波振荡器差分信号线的对应点, EN0端接电压调节端.当EN0端电压为0 V时, 电容最大; 当EN0端电压为1 V时, 电容最小.65 nm工艺提供了4种不同阈值电压的晶体管, 由高到低分别为高阈值、普通阈值、低阈值和零阈值.通过仿真发现, 阈值越低, 电容的变化范围越大, 因此选择零阈值的NMOS晶体管zvtnfet来构建变容二极管.

|

图 5 用于驻波振荡器的变容二极管结构 Fig. 5 Varactor structure for standing-wave oscillator |

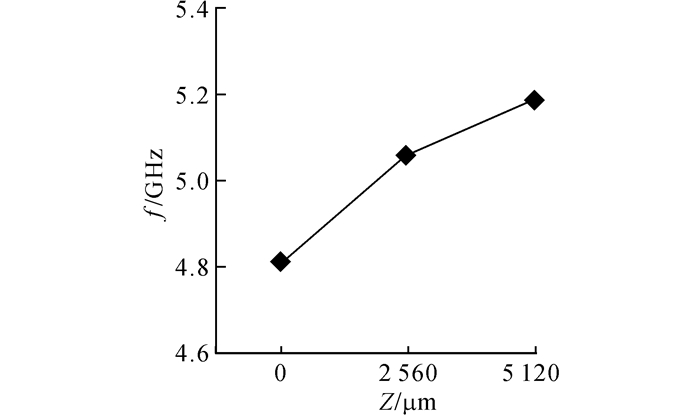

驻波振荡器中传输线不同位置的信号幅值不同, 变容二极管电容与A、B端与EN0端的电压有关, 因此该变容二极管应用于驻波振荡器不同位置, 对频率调节的影响效果不同.设置变容二极管中NMOS的宽度为47.5 μm, 设置EN0端电压为0 V, 基于图 2的仿真结构和表 1的参数, 仿真该变容二极管位于传输线0 μm、2 150 μm核5 120 μm处时的等效电容以及对应的驻波振荡器振荡频率, 结果如图 6所示.

|

图 6 不同位置变容二极管引起的振荡频率变化 Fig. 6 Frequency variation caused by varactors' placement |

当变容二极管的摆放位置由位置0 μm移向最远端时电容变小, 振荡频率由4.8 GHz提高到5.19 GHz, 而功耗由14.5 W降低为13.6 W.这是由于在位置0 μm处传输线上的电压最大, A、B端电压和EN0端电压差值的变化范围最大, 因此电容的可变范围最大.驻波振荡器的主要功耗来自于交叉耦合反相器组, 当变容二极管位于不同位置时振荡器频率不同.频率越低, 则反向器组的充电和放电速度越慢, 从而导致功耗越大.变容二极管放在位置0的功耗最高.

通过不同工艺角和温度条件的组合仿真发现, 该变容二极管对驻波振荡器频率的影响很小.如式(1) 所示, 驻波振荡器的振荡频率主要取决于传输线的参数, 因此该结构具有很好的容忍工艺和温度偏差的特性.

2.2 频率调节结构图 7显示了变容二极管集成在驻波振荡器中的两种结构.如图 7(a)所示为集总(lumped)式, 如图 7(b)所示为分布(distributed)式, 其中分布式结构采用均匀分布方式.根据2.1节的分析表明, 集总式分布的变容二极管的电容变化范围更大, 因此频率调节范围更大, 同时驻波振荡器的功耗更高.当采用了16级的变容二极管结构, 每个NMOS管宽度设置为9.5 μm时, 集总结构频率最高为5 GHz, 最低为4 GHz, 调节范围为20%, 对应的功耗分别为12.8和13.5 mW.均匀分布时, 最高频率为5.3 GHz, 最低为4.9 GHz, 调节范围为7.5%, 对应的功耗分别为12.2和13.1 mW.

|

图 7 集总变容二极管结构和分布变容二极管结构 Fig. 7 Lumped varactors and distributed varactors |

集总式分布有利于在更大范围内调节频率, 但振荡器最高频率下降, 功耗增加.集总式分布的频率调节方式在于改变了振荡的边界条件, 降低了振荡器的Q.分布式调节方式的本质是改变信号在传输线上的传输速度, 对Q的影响小.

这两种调节方式适用于其他类型的驻波振荡器.如表 2所示为其他结构驻波振荡器采用集总式变容二极管时的仿真结果.

| 表 2 不同类型驻波振荡器调节结果 Table 2 Frequency tuning result of different SWOs |

表 2中, λ/4驻波振荡器基本参数与表 1一致, λ/2驻波振荡器和莫比乌斯驻波振荡器的交叉耦合反相器组尺寸比λ/4驻波振荡器增加了1倍.

2.3 基于驻波振荡器的PLL将频率可调节驻波振荡器应用于芯片时钟系统设计时, 面临着时钟频率的配置方式问题.目前, 基于PLL的时钟系统根据参考时钟和配置信号来实现频率的自动锁定, 基于驻波振荡器的PLL可以采用同样方式实现时钟的配置[14-15], 本文中基于驻波振荡器的PLL(SPLL)的结构如图 8所示.该结构中的鉴频鉴相器(PFD)、电荷泵、滤波结构(loop filter)和分频结构(freq divider)与传统的PLL完全一致, 只是用驻波振荡器替换了压控振荡器; 同时, 为了进行频率相位比较, 增加了时钟恢复模块(clock recover)用于将驻波振荡器的正弦信号转化为方波信号.

|

图 8 SPLL结构 Fig. 8 SPLL architecture |

该结构的接口信号除了包含普通PLL的复位信号、参考时钟和分频配置信号外, 还增加了一组用于控制驻波振荡器中变容二极管的配置信号(EN*).驻波振荡器的变容二极管采用集总式结构, 分为固定信号配置部分和动态电压调节部分.根据目标频率, 可以通过粗粒度配置信号(EN*)设置驻波振荡器达到目标频率附近的一定范围, 由PLL鉴频鉴相结果控制的可变电平输出, 控制变容二极管的动态电压调节部分进行快速锁频.

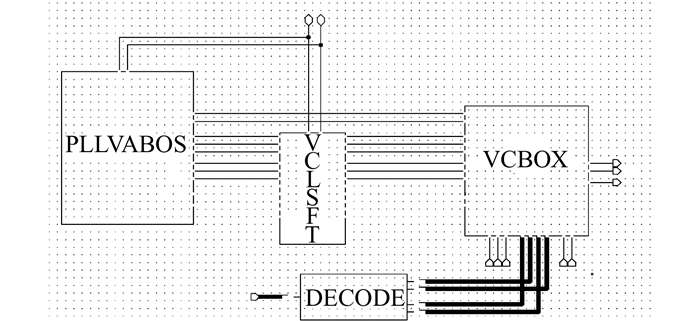

如图 9所示为SPLL的电路图, 其中DECODE和VCBOX是数字控制逻辑, VCLSFT为模拟信号数字信号转换逻辑, PLLVABOX包含了鉴频鉴相器、电荷泵、滤波结构、驻波振荡器.除驻波振荡器外, 其他逻辑已经过流片验证.SPLL的仿真采用基于电路的前仿真方式.

|

图 9 SPLL的电路图 Fig. 9 Schematic of SPLL |

SPLL的工作过程与普通PLL的类似, 图 10显示了在(slow/slow, 0.9 V, 125 ℃), (typical/typical, 1 V, 75 ℃)(fast/fast, 1.1 V, 25 ℃)3种条件下的锁定过程.所用的EN*信号配置为高电平, 参考时钟为300 MHz, 分频配置系数为16, 因此目标频率为4.8 GHz.可以看出, 选择合适的驻波振荡器设计参数后, SPLL可以在较宽的工艺、温度和电压偏差下正常工作.

|

图 10 不同条件下SPLL锁定过程 Fig. 10 Locking process of SPLL under different conditions |

其他采用驻波振荡器实现的PLL[14], 调节方式采用了粗粒度调节和细粒度调节方式.粗粒度调节通过打开过关闭参与振荡器的固定宽度的传输线数目来实现频率的调节, 细粒度频率调节通过控制衬底的偏置电压来实现.该PLL与本文描述的PLL的比较, 如表 3所示.

| 表 3 2种驻波振荡器PLL的性能比较 Table 3 Performance of two SWO-based PLL |

SPLL可以直接用于在一定的范围内进行时钟信号的高质量、可靠传播, 适用于全局异步局部同步特性的芯片(global asynchronous local synchronous, GALS).由于每个较小区域内可以只由1个PLL生成和传播同步时钟, 避免了多个PLL共同生成1个时钟时锁定过程不一致的情况.为了尽可能扩大该PLL的作用范围, 可以选择λ/2驻波振荡器来作为振荡源.

2.4 自定义频率调节结构尽管全局异步局部同步结构有利于芯片时钟系统设计, 但目前部分芯片要求在全芯片范围内布局同步时钟信号.当驻波振荡器用于该类时钟系统设计时, 需要多个驻波振荡器耦合形成全局时钟分布网络.该网络不能直接采用PLL的频率调节方式, 因为在大范围内传输电流源输出信号存在可靠性和延迟问题, 为此设计了全数字的频率自动调节结构和流程.

如图 11所示为自动锁频的驻波振荡器结构, 可以根据输入参考时钟的指示将频率锁定到参考时钟频率.驻波振荡器的频率调节分为固定信号配置部分和动态电压调节部分.根据目标频率, 可以通过类似于图 8的粗粒度配置信号设置粗粒度的变容二极管, 使振荡频率达到目标频率的一定范围内, 由频率比较结果生成动态配置信号, 控制细粒度的变容二极管, 使振荡频率在最接近目标频率时保持锁定.

|

图 11 自动锁频驻波振荡器 Fig. 11 Self-locking SWO |

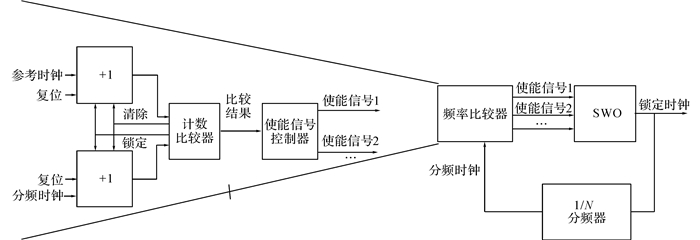

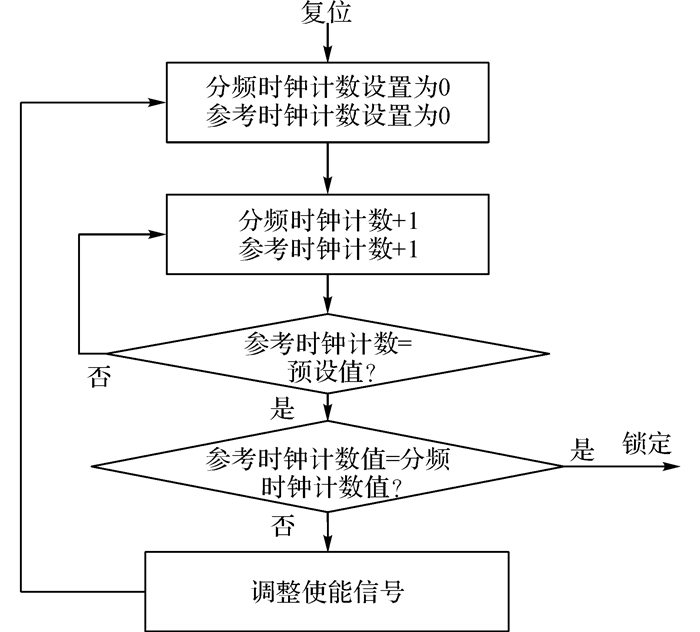

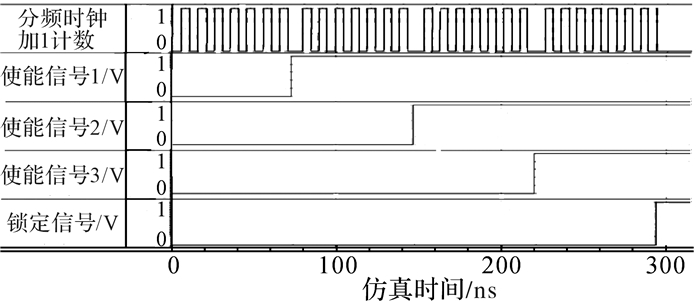

动态配置信号的生成由频率比较模块(freq cmp)控制, 采用计数比较的方式来比较经过分频后的振荡时钟和参考时钟的频率差异, 但不能比较相位.通过固定时间内两个时钟周期的计数值来判断频率的差异, 固定时间由参考时钟周期计数值来表示, 可以保存在配置寄存器(num)中.如图 12所示为该结构的频率锁定流程.

|

图 12 自动锁频控制流程 Fig. 12 Frequency locking control process |

复位结束后, 每隔配置寄存器指定的参考时钟周期检查振荡时钟周期计数.如果小于配置寄存器的数据表明, 振荡时钟慢于目标频率, 调整使能信号(enable*)的1位由低电压变为高电压, 以提高振荡时钟频率; 如果大于配置寄存器的数据, 则反向调整.若反复直至两个时钟周期计数相等(或差值在给定范围内), 则此时时钟处于锁定状态, 不再进行计数比较.可以看出, 该结构锁定后, 频率与目标频率有一定的误差, 具体误差与1位使能信号控制的变容二极管大小有关.

为了验证该算法的正确性, 采用集总式变容二极管结构来进行仿真, 其中驻波振荡器的长度为8 500 μm, 其余参数与2.2节一致, 振荡频率为3.0~3.6 GHz.为了加快仿真速度, 参考时钟选择3.3 GHz, 配置寄存器保存的数据为1;预先通过粗粒度配置信号, 将驻波振荡器初始频率调整为3.2 GHz, 以使得频率尽快锁定.如图 13所示为整个锁定过程, 选择2个时钟第4位计数来显示两者的频率差异.可以看出, 经过4次调节, 驻波振荡器的振荡频率超过参考时钟后, 系统进入锁定状态, 而驻波振荡器频率调节粒度决定了整个频率逼近的精度与速度.

|

图 13 驻波振荡器数字化自动锁频流程 Fig. 13 SWO digital locking process |

全局异步局部同步结构可以减小芯片级高频时钟的设计难度.以多核处理器为例, 每个处理核心都有自己的PLL, 各个核心之间的时钟没有时钟偏斜的控制要求, 因此不需要设计复杂的全局时钟网络.如图 14(a)所示为多核芯片中核心内SPLL的示意图.对多数芯片而言, λ/2驻波振荡器可以覆盖核心的面积.该SPLL不但可以提供稳定的时钟源, 而且本身实现了区域内的时钟分布.如图 14(b)所示为多核心芯片中SPLL的分布.4个核心、2个PCIE模块、2个DDR模块、一个互联模块都有各自独立的SPLL, 各部分之间不需要控制时钟的频率和相位.可以看出, SPLL对全局异步局部同步类型的芯片具有很好的适用性.

|

图 14 核心中的SPLL和多核芯片中的SPLL Fig. 14 SPLL in core and multi-core chip |

当前, 大量芯片需要在全芯片范围内共享同步的时钟信号, 其中很多芯片尺寸已经达到或超过了20 mm×20 mm.在单个驻波振荡器中, 传输线长度有限, 无法覆盖整个芯片, 因此需要在全芯片分布多个驻波振荡器.在这种情况下, 一般采用驻波振荡器耦合的方式实现特定结构的分布, 如阵列结构[5]、蛇形线结构[17]等.Mandal等[10]的研究表明, 不将驻波振荡器进行耦合, 采用统一的启动信号来控制各个驻波振荡器的初始振荡条件, 可以使各个驻波振荡器的振荡过程保持一致.

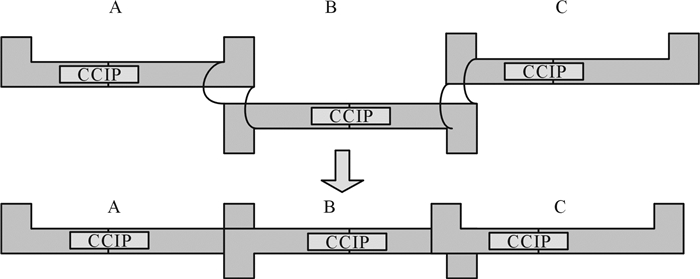

如图 15所示为A、B、C三个驻波振荡器通过将相同位置两两互连, 从而使各个驻波振荡器的振荡频率与相位保持一致.

|

图 15 驻波振荡器耦合结构 Fig. 15 SWO coupling architecture |

各个驻波振荡器耦合的强度取决于耦合的位置, 离传输线短路端的距离越近, 耦合强度越弱.研究表明, 当距离短路端的距离为传输线长度的15%~20%时, 可以保证足够的耦合强度.耦合后的振荡器由于存在相位平均效应, 各个驻波振荡器之间不匹配造成的时钟偏斜以及电压变化造成的时钟抖动都会减小[6-7].

针对4个采用图 15的耦合方式构成的网格(grid)结构驻波振荡器的理论分析和仿真结果都表明, 调节其中两个相邻的驻波振荡器10%的传输线长度, 将导致10 ps的振荡周期差异, 但4个振荡器中心点的时钟偏斜只有1 ps.

仿真了图 15中的3个振荡器处于不同工作电压时的振荡频率差异, 仿真结果如图 16所示.图中, fA、fB、fC分别为A、B、C驻波振荡器的频率.仿真结果表明, 当3个驻波振荡器的工作电压不同时, 耦合结构有助于缩小相互之间的频率差异.例如当A、B、C工作电压分别为1.1、0.9和1.1 V时, 耦合后的振荡频率分别为5.54、5.74和5.56 GHz, 频率误差为3.5%.在正常情况下, A、B、C全部工作在1.1和0.9 V条件下, 驻波振荡器的振荡频率差异为12%.耦合结构有利于控制大范围分布的驻波振荡器的频率差异, 从而有利于高频时钟的低偏斜分布.

|

图 16 耦合驻波振荡器不同工作电压下的频率 Fig. 16 Frequency of coupled SWOs under different voltages |

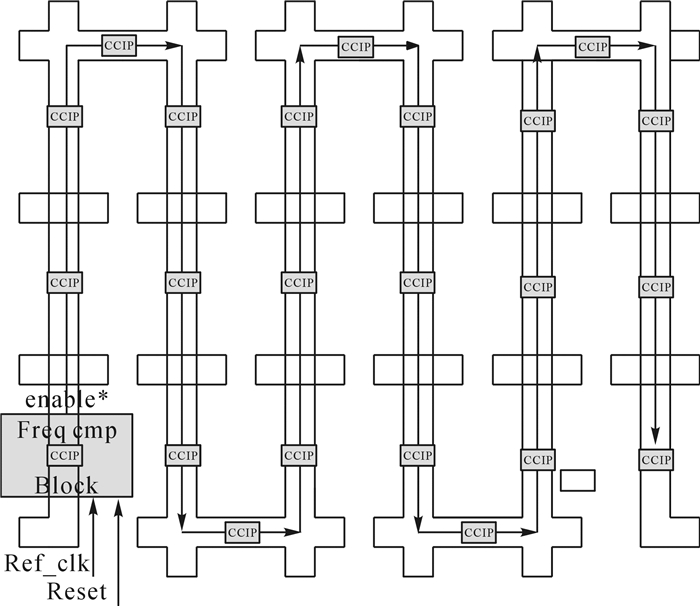

以λ/2驻波振荡器为基本单元, 采用多个驻波振荡器互连方式来组成整个芯片的时钟分布网络.为了节省资源, 没有采用阵列的方式, 采用蛇形的结构来完成多个驻波振荡器在全芯片内的分布.如图 17所示为采用该方式, 利用多个驻波振荡器构建全芯片的时钟分布结构.其中只包含一个频率比较模块, 该模块选择一个驻波振荡器的频率输出作为基准, 与参考时钟进行对比, 但生成的频率调节使能信号给所有驻波振荡器使用.由于计数周期较长, 使能信号有充分的时间传播给各个驻波振荡器使用.由于使能信号到达不同驻波振荡器的延迟不一致, 每次使能信号调节的集总式变容二极管的大小应足够小, 这样相邻驻波振荡器的频率差异有限, 再通过驻波振荡器耦合的相位平均效应可以保证不同驻波振荡器的频率一致和不同位置间时钟偏差可控.

|

图 17 蛇形多驻波振荡器耦合结构 Fig. 17 Serpentine multiple SWO coupling |

(1) 基于反型金属氧化物半导体场效应晶体管的变容二极管应用于驻波振荡器, 可以实现频率的调节, 最大频率调节范围达到20%.

(2) 集总式变容二极管比分布式变容二极管更适合有较大范围频率调节需求的应用, 但功耗略增加, 最高频率降低.

(3) 基于该频率可调驻波振荡器可以实现频率的自动调节与锁定, 其中SPLL结构可以实现传统PLL的功能, 而自定义频率锁定方式可以实现全数字方式的频率锁定.

(4) 基于该频率可调驻波振荡器设计的时钟系统具有容忍电压和温度波动以及工艺偏差的特性, 可以实现高频时钟信号的低偏斜、可靠传播.

| [1] | CHAN S C, RESTLE P J, SHEPARD K L, et al. A4.6 ghz resonant global clock distribution network [C] //Proceedings of IEEE International Solid-State Circuits Conference (ISSCC). San Fransisco: IEEE. 2004:341-343. |

| [2] | CHAN S C, SHEPARD K L, RESTLE P J. Design of resonant global clock distributions [C]// Proceedings of IEEE International Conference on Computer Design (ICCD). San Jose: IEEE, 2003: 238-243. |

| [3] | DRAKE A, NOWKA K J, NGUYEN T Y, et al. Resonant clocking using distributed parasitic capacitance[J]. IEEE Journal of Solid-State Circuits, 2004, 39(9): 1520–1528. DOI:10.1109/JSSC.2004.831435 |

| [4] | WOOD J, EDWARDS T C, LIPA S. Rotary traveling-wave oscillator arrays: a new clock technology[J]. IEEE Journal of Solid-State Circuits, 2001, 36(11): 1654–1665. DOI:10.1109/4.962285 |

| [5] | ANDRESS W, HAM D. Recent developments in standing-wave oscillator design: review [C]// Radio Frequency Integrated Circuits (RFIC) Symposium. Digest of Papers. Forth Worth: IEEE, 2004: 119-122. |

| [6] | MAHONY F O. 10 ghz global clock distribution using coupled standing-wave oscillators [D]. Palo Alto: Stanford University, 2003. |

| [7] | MAHONY F O, YUE C P, HOROWITZ M A, et al. A 10 ghz global clock distribution using coupled standing wave oscillators[J]. IEEE Journal of Solid-State Circuits, 2003, 38(11): 1813–1820. DOI:10.1109/JSSC.2003.818299 |

| [8] | ANDRESS W, HAM D. Standing wave oscillators utilizing wave-adaptive tapered transmission lines[J]. IEEE Journal of Solid-State Circuits, 2005, 40(3): 638–651. DOI:10.1109/JSSC.2005.843600 |

| [9] | CODERO V H, KHATRI S P. Clock distribution scheme using coplanar transmission lines [C]// DATE'08. Munich: IEEE, 2008: 985-990. |

| [10] | MANDAL A, KARKALA V, KHATRI S, et al.Interconnected tile standing wave resonant oscillator based clock distribution circuits [C]// 24th Annual Conference on VLSI Design. Chennai: IEEE, 2011: 82-87. |

| [11] | GAUTHAUS M R, TASKIN B. High-performance, low-power resonant clocking: embedded tutorial[C]// IEEE/ACM International Conference on Computer-Aided Design. San Jose: IEEE, 2012: 742-745. |

| [12] | HONKOTE V, TASKIN B. Skew analysis and design methodologies for improved performance of resonant clocking [C]// 2009 International SoC. Busan: IEEE, 2009: 165-168. |

| [13] | HONKOTE V, NAGARAJAN R D. Process variation sensitivities of rotary traveling wave and mobius standing wave oscillators [C]// International Symposium onElectronic System Design. Singapore: IEEE, 2013: 6-10. |

| [14] | KARKALA V, BOLLAPALLI K C, GARG R, et al. A PLL design based on a standing wave resonant oscillator [C]// IEEE International Conference on Computer Design (ICCD). Lake Tahoe: IEEE, 2009: 511-516. |

| [15] | MANDAL A, BOLLAPALLI K C, JAYAKUMAR N, et al. A low-jitter phase-locked resonant clock generation and distribution scheme [C]// IEEE 31st International Conference on Computer Design (ICCD). Asheville: IEEE, 2013: 487-490. |

| [16] | BUNCH R L, RAMAN S. Large-signal analysis of MOS varactors in CMOS-Gm LC VCOs[J]. IEEE Journal of Solid-State Circuits, 2003, 38(8): 1325–1332. DOI:10.1109/JSSC.2003.814416 |

| [17] | SHEN Mei-gen, ZHENG Li-Rong, TJUKANOFF E, et al. Concurrent chip package design for global clock distribution network using standing wave approach[C]// 6th International Symposium on Quality of Electronic Design. San Jose: IEEE, 2005: 573-578. |